(54) АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметико-логическое устройство | 1977 |

|

SU703808A1 |

| Устройство для сравнения чисел | 1978 |

|

SU809164A1 |

| Устройство для суммирования двоично-десятичных чисел | 1980 |

|

SU1001087A1 |

| Устройство для умножения | 1988 |

|

SU1670685A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для суммирования и вы-чиТАНия дВОичНО-дЕСяТичНыХ КОдОВ | 1978 |

|

SU813415A1 |

| Устройство для умножения | 1988 |

|

SU1578711A1 |

| Матричное устройство для умножения | 1985 |

|

SU1267408A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1977 |

|

SU693369A1 |

Изобретение относится к вычислительной технике и может быть применено при разработке- быстродействующих арифметико-логических устройств (АЛУ), выполняющих логические операции, а также операции двоичной и десятичной арифметики.

Известно многофункциональное АЛУ, содержащее два регистра, три малоразрядных сумматора, которые могут объединяться попарно или все вместе с помощью клапанов, блок управления 1 .

Недостатком из-вестного АЛУ явля ется его малое быстродействие из-за необходимости коммутации сумматоров на каждом шагу работы АЛУ.

Известно быстродействующее АЛУ, содержащее блок двоичной арифметики, предназначенный для выполнения арифметических операций над двоичными числами и логических операций, и блок цифровой десятичной арифметики 21 .

Основными недостаткг1мн этого АЛУ являются простаивание блока двоичной арифметики при работе блока цифровой десятичной арифметики и наоборот . большой объ«;м оборудования.

Известно также АЛУ, содержащее два входных регистра, узел транзита, инвертирования и десятичной коррекции, узел формирования логических функций, узел формирования межтетрадных переносов, узел формирования внутритетрадных переносов, узел селекции, выходной регистр, узел формирования признаков операций, причем

10 входы узла транзита, инвертирования к десятичной коррекции соединены с прямыми и инверсными выходами первого входного регистра, а выходы подключены к первой группе входов узла

15 формирования логических функций,-к второй группе входов которого подключены выходы второго входного регистра, первая и вторая группы выходов узла формирования логических

20 функций соединены соответственно с первой и второй группами узла формирования межтетрадных переносов, узла формирования внутритетрадных переносов и узла селекции, третья груп-f

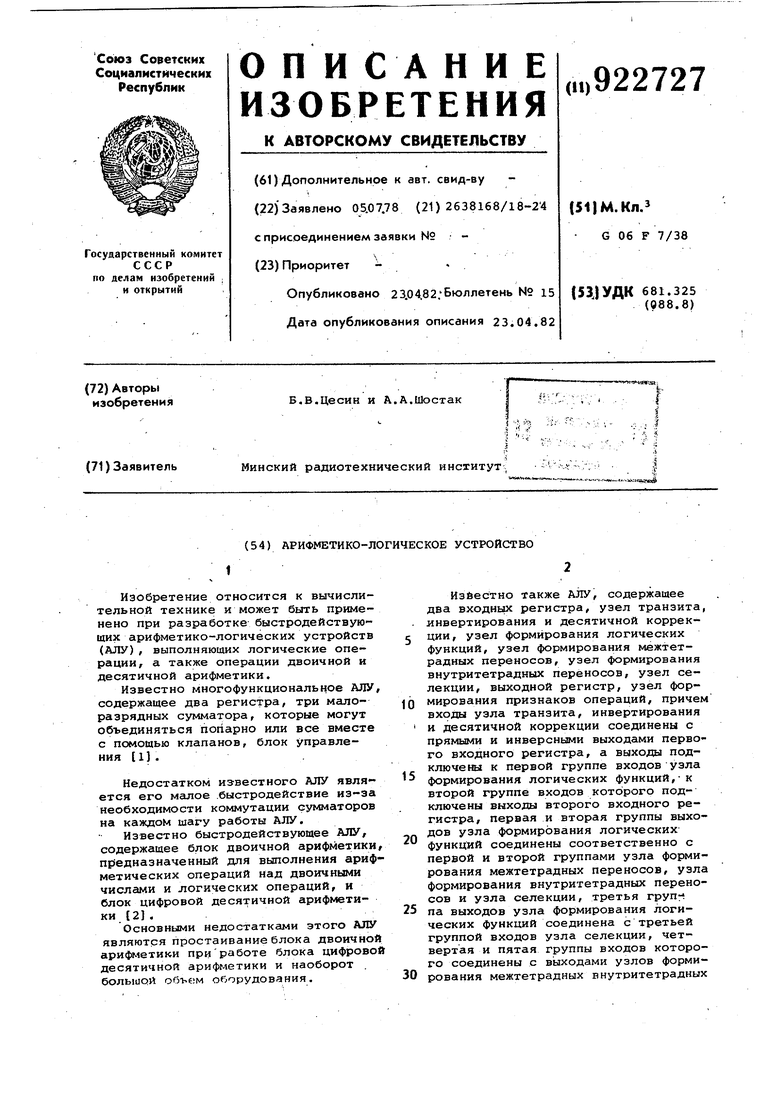

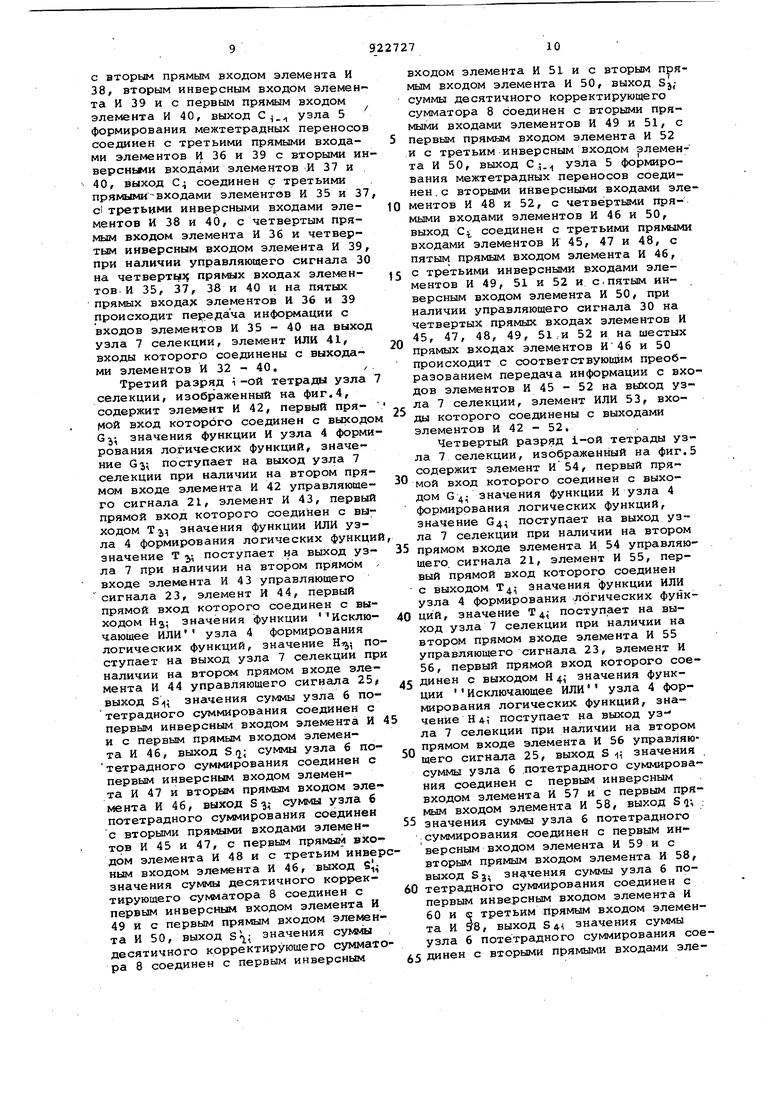

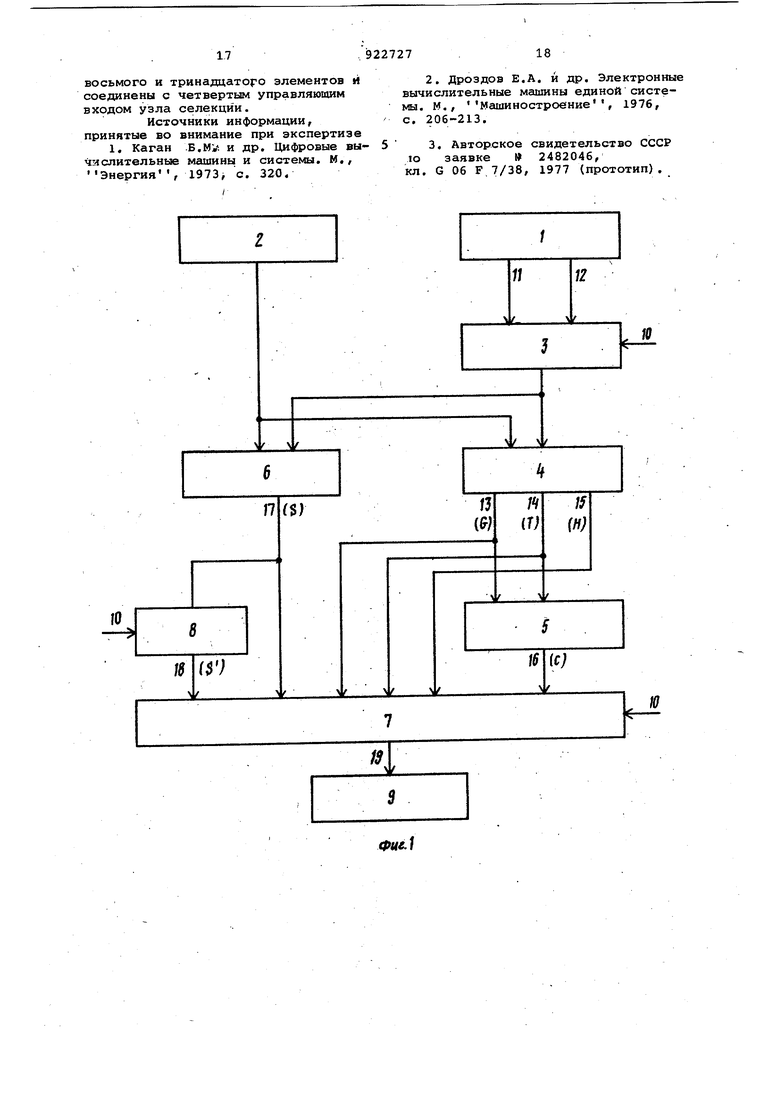

25 па выходов узла формирования логических функций соединена с третьей группой входов узла селекции, четвертая и пятая группы входов которого соединены с выходами узлов форми30рования межтетрадных внутритетрадных переносов, выходел узла селекции под ключены к входам выходного регистра третья группа входов узла формирова ния внутритетрадных переносов подкл чена к выходам узла межтетрадных переносов, выходы узла формирования признаков операций подключены к управляющим входам узла транзита, инвертирования и десятичной коррекции и узла поразрядной секции, кроме эт го устройство содержит дополнительны узлы транзита инвертирования и десятичной коррекции, формирования логических функций и формирования внутритетрадных переносов, причем входы дополнительного узла транзита инвертирования и десятичной, коррекции подключены к прямым и инверсным выходам первого регистра, а выходы подключены к первой группе вхо дов дополнительного узла ;.,формирова ния логических функций, первая и вт рая группы выходов которогосоединены соответственно с первой и второй группой входов дополнительного узла формирования внутритетрадных п реносов, третья группа входов которого подключена к выходам узла формирования межтетрадных переносов, а выходы соединены с шестой группой входов узла селекции, седьмая группа входов которого подключена к третьей группе выходов дополнительного узла формирования логических функций, вторая группа входов которого подключена к выходам второго р гистра 3 . Основным недостатком данного АЛУ является недостаточное быстродействие вследствие наличия узлов формирования внутритетрадных переносов включенных между узлом формирования межтетрадных переносов и узлом селекции. Цель изобретения - увеличение быстродействия арифметико-логическо го устройства. Поставленная цель достигается тем, что АЛУ, содержащее входные ре гистры, узел транзита, инвертирования и десятичной коррекции, узел формирования логических функций, узел формирования межтетрадных пере носов, узел селекции и выходной регистр, входы которого соединены с выходг1ми узла селекции, входы узла транзита, инвертирования и десятич ной коррекции соединены с прямыми и инверсными выходами первого входного регистра, а выходы подключены к первой группе входов узла формирова ния логических функций, к второй группе входов которого подключены выходы второго входного регистра, первая и вторая группы выходов узла формирования логических функций-сое динены cooTBeTCTBetiHO с первой и вт трой группами входов узла формирования межтетрадных переносов и узла селекции, третья группа выходов узла формирования логических функций соединена с третьей группой входов узла селекции, четвертая группа входов которого соединена с выходами узла формирования межтетрадных переносов, группа управляющих входов узла транзита, инвертирования и десятичной коррекции и узла селекции подключены к управляющему входу устройства, дополнительно содержит узел потетрадного суммирования и десятичный корреактиругощийсумматор, причем входы узла потетрадного -суммирования под-, рлючены к выходам узла транзита. Инвертирования и десятичной коррекции и второго входного регистра, а выходы подключены к входам десятичного корректирующего сумматора и пятой группы входов узла селекции, шестая группа входов которого подключена- к выходам десятичного корректирующего сумматора, управляющий вход которого, соединен с управляющим вхог- . дом устройства. Кроме того, узел селекции содержит в каждом разряде элементы И и ИЛИ, причем выходы элементов И подключены к входам элемента ИЛИ, выход которого соединен с выходом соответствующего разряда узла селекции, причем в первом разряде каждой тетрады узла селекции первые прямые входы первого, второго и третьего элементов И соединены с соответствующими входами первой, второй и треЕьй групп входов узла селекции, а вторые прямые входы этих элементов И соединены соответственно с первым, вторым и третьим управляющими входа-ми узла селекции, первый инверсный вход четвертого элемента И и первый прямой вход пятого элемента И подключены к соответствующему входу пятой группы входов узла селекции, первый инверсный вход шестого элемента И и первый прямой вход седьмого элемента И подключены к соответствующему входу шестой группы входов узла селекции , второй и третий прямые входы четвертого элемента И, второй инверсный и третий прямой входы пятого элемента И, второй прямой и третий инверсный входы шестого элемента И и второй и третий инверсные входы- седьмого элемента И подключены к соответствующим входам четвертой группы входов, .четвертые прямые входы четвертого, пятого, шестого и седьмого элементов И подключены к четвертому управляющему входу узла селекции, во втором разряде каждой тетрады узла селекции первые прямые входы первого, второго и третьего элементов И соединены с соответствующими входами первой, второй и третьей трупп входов узла селекции, а вторые прямые входы эти элементов И соединены соответственно с первым, вторым и третьим управ ляющими входами узла селекции, первый инверсный и второй прямой входы четвертого элемента И, первый прямой и второй инверсный входы пятого элемента И и первый прямой,вход шес того элемента и подключены к соотве ствующим входам пятой группы вхо. дов узла селекции, первый инверсный и второй прямой входы, седьмого элемента и, первый прямой и второй инверсный входы воЪьмого элемента И и первый прямой вход девятого элемента и подключены к соответствующим входам -шестой группы входов узла се лекции, третий прямой вход четвертого элемента и, третий и четвертый прямые входы пятого элемента И, вто рой инверсный и третий прямой входы шестого элемента И, третий инверсны вход седьмого элемента И, третий прямой и четвертый инверсный входы восьмого элемента И и второй и третий инверсные входы девятого элемента И подключены к соответствующим входам четвертой группы входов узла селекции, четвертые прямые входы четвертого, шестого, седьмого и девятого элементов И, а также пятые прямые входы пятого и восьмого элементов И соединены с четвертым управляющим входом узла селекции, в третьем разряде каждой т.етрады узла селекции первые прямые входы первого, второго и третьего элементов И соединены с соответствующими входами первой, второй и третьей групп входов узла селекции, а вторые прямые входы этих элементов И соединены соответственно с первым, вторым и третьим управляющими входами узла селекции, .первые инверсные и вторы прямые входы четвертого и пятого элементов И, первый прямой вход шес того элемента И, первый и второй прямые и третий инверсный входы седьмого элемента И подключены к соответствующим входам пятой группы входов узла селекции, первые инверсные и вторые прямые входы восьмого и девятого элементов И, первый прямой вход десятого элемента И, первый и второй прямые и третий инверсный входы одиннадцатого элемента И подключены к -COOTEJ TCTвующим входам шестой группы входов узла селекции, третьи прямые входы четвертого и пятого элементов И, второй инверсный и третий прямой входы шестого элемента И, четвертый и пятый прямые входы седьмого элемента И, третьи инверсные входы восьмого и девятого элементов И, второй и третий инверсные входы десятого элемента И, четвертый прямой и пятый инверсный входы одиннадцатого элемента И.подключены к соответствующим входам четвертой группы входов узла селекции, четвертые прямые входы четвертого, пятого, шее-, того, восьмого, девятого и десятого элементов И, а также шестые прямые входы седьмого и одиннадцатого элементов И соединены с четвертым управляющим входом узла селекции, в четвертом разряде каждой тетрады узла селекции первые прямые входы первого, второго и третьего элементов И соединены с соответствующими входами первой, второй и третьей групп входов узла селекции, а вторые прямые входы этих элементов И соединены соответственно с первым, вторым и третьим управляющими входами узла селекции, первыр инверсные и вторые прямые входы четвертого, пятого и шестого элементов И, первый прямой вход седьмого элемента И, а также первый, второй и третий прямые и четвертый инверсный входы восьмого элемента и подключены к соответствующим входам пятой группы входов.узла селекции, первые инверсные и вторые прямые входы девятого, десятого и одиннадцатого элементов И, первый прямой вход двенадцатого элемента И, а также первый, второй и третий прямые и четвертый инверсный входы двенадцатого элемента И подключены к соответствующим входам шестой группы входов уэла селекции, третьи прямые входы четвертого, пятого и шестого элементов И, второй инверсный и третий прямой входы седьмого элемента И пятый и шестой прямые входы восьмого элемента И, третьи инверсные входы девятого, десятого и одиннадцатого элементов И, второй и третий инверсные входы двенадцатого элемента И и пятый прямой и шестой инверсный входы тринадцатого элемента И подключены к соответствующим входам четвертой группы входов узла селекции, четвертый прямой вход четвертого, пятого, шестого, седьмого, девятого, десятого, одиннадцатого и двенадцатого элементов И, а также седьмой прямой вход восьмого и тринадцатого элементов И соединены с четвертым управляющим входом узла селекции. На фиг.1 приведена структурная схема арифметико-логического устройства;- на фиг.2 - 5 - функциональные схемы соответственно первого, второго, третьего и четвертого разрядов i-ой тетрады узла селекции. АЛУ, изображенное на фиг.1, содержит два входных регистра 1 и 2, узел 3 транзита, инвертирования и десятичной коррекции, узел 4 формирования логических функций, узел 5 формирования межтетрадных переносов узел 6 потетрадного суммирования, узел 7 селекции, десятичный корректирующий.; сумматор 8, выходной регистр 9, управляющий вход 10, причем входы узла 3 транзита, инвертирования и десятичной коррекции соединены с прямьлми 11 и инверсными 12 выходами первого входного регистра 1, а выходы подключены к первой группе входов узла 4 формирования логических функций, к второй Группе входов которого подключены выходы второго входного регистра 2, первая 13 и вторая 14 группы выходов, предназначенные для формирования соответственно значений функций И и ИЛИ узла 4 формирования логических функций, соединены соответственно с первой и второй группами входов узла 5 формирования мажтетрадных переносов и узла 7 селекции,- третья 15 группа выходов, предназ,начен ная для формирования значения- функции Исключающее ИЛИ узла 4 формирования логических функций, соединена с третьей группой входов узла 7 селекции, четвертая группа входов которого соединена с выходами 16 узла.5 формирования межтетрадных переносов, первая и вторая группы входов узла б потетрадного суммирования подключены соответств.енно к выходсш узла 3 транзита, инвертирования и десятичной коррекции и второго входного регистра 2, вход десятичного корректирующего сумматора 8 соединен с выходом 17 узла 6 потетрадного суммирования и с группой входов узла 7 селекции, шестая дополнительная группа входов которого соединена с выходом 18 десятичного корректирующего сумматора В, выход 19 узла 7 селекции соединен с входом выходного регистра 9.

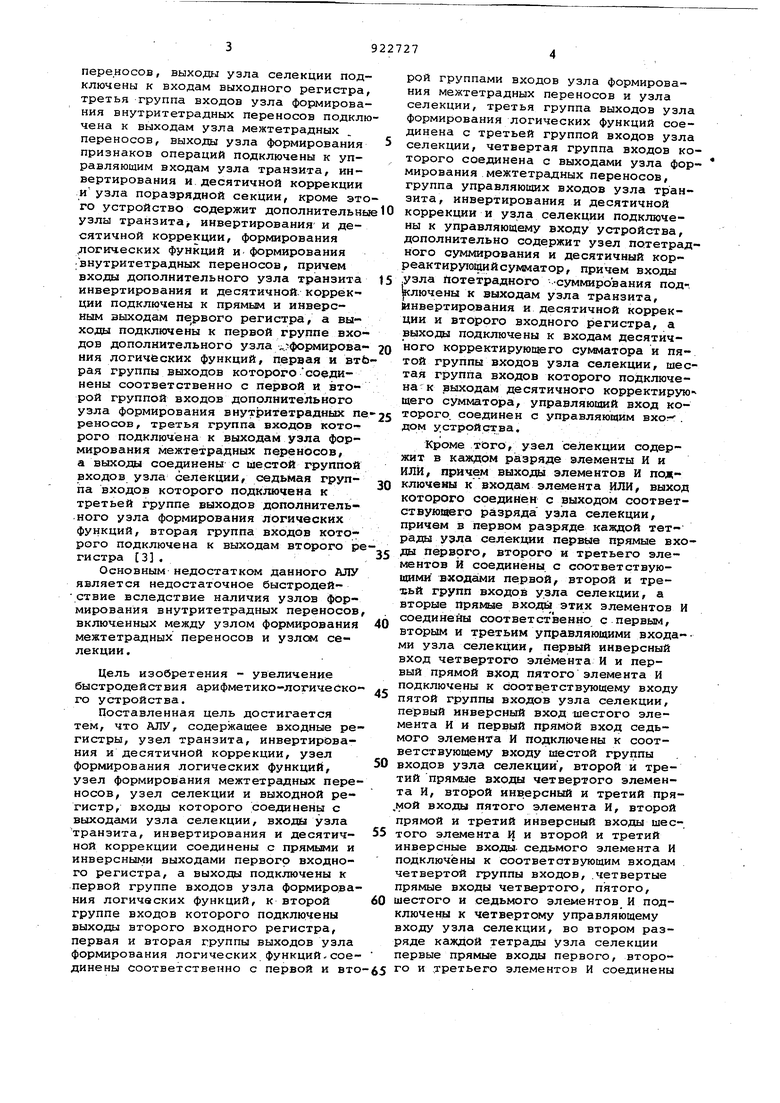

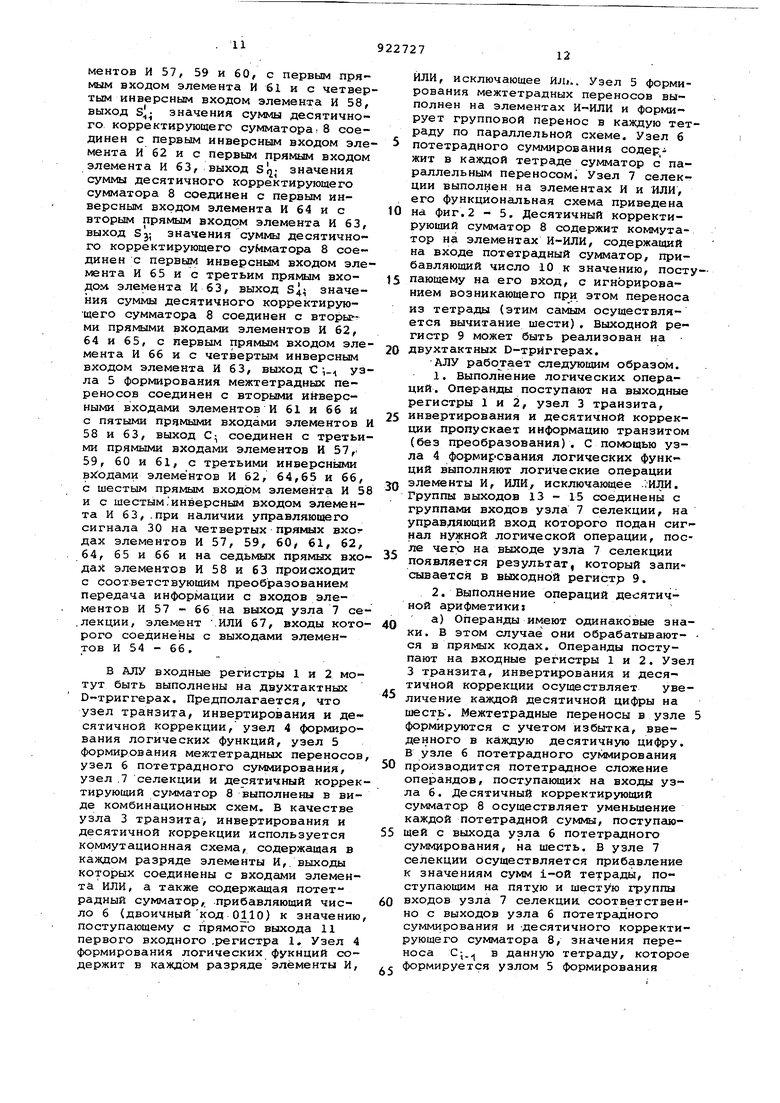

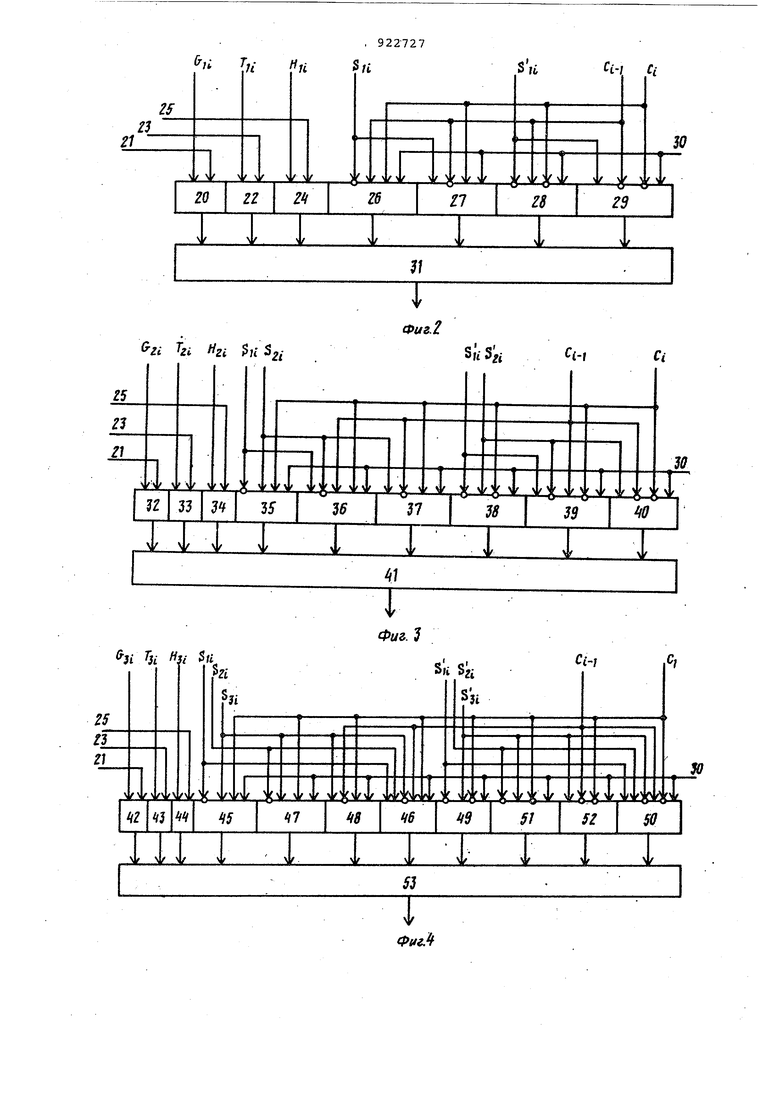

Первый разряд 1-ой тетрады узла 7 селекции, изображенный на фиг.2, содержит.-элемент И 20, первый прямой вход которого соединен с выходом значения функции И узла 4 формирования логических функций, значение G,- поступает-..на вход узла 7 селекции при наличии на втором прямом входе элемента И 20 управляющего сигнала 21, элемент И 22, первый прямой вход которого соединен . с выходом значения функции ИЛИ узла 4 формирования логических функций, значение Т. поступает на выход узла 7 селекции при наличии на втором прямом входе элемента И 22 управляющего сигнала 23, элемент И 24, первый прямой вход которого соединен с выходом Н . значения функции Исключающее -ИЛИ узла 4 формирования логических функций, значение Н:,,- поступает на вход узла 7

селекции при наличии на втором прямом входе элемента И 24 управляющего сигнала 25, выход S. значения .суммы узла 6 потетрадного суммирования соединен с первым инверсным входом элемента И 26 и с первым пря мым входом элемента И 27, выход s значения суммы десятичного корректирующего сумматора 8 соединен с -, первым инверсным входом элемента И

0 28 и с первым прямым входом элемента И 29, выход С 4- узла 5 формирования межтетрадных переносов соединен с вторыми прямыми входами элементов И 26 и И 28 и с вторыми йн5 версными входами элементов И 27 и 29, выход С- узла 5 формирования межтетрадных переносов соединен с третьими прямыми входами, элементов И 26 и И 27 и третьими кнверсны0 ми входами элементов И 28 и И 29, при наличии управляющего сигнала 30 на четвертых прямыз входах элементов И 26 - 29 происходит с соответствующим преобразованием передача

5 информации с входов элементов И 26 29 на выход узла 7 селекции, эле-г-: мент ИЛИ 31, входы которого соединены с выходами элементов И 20, 22, 24, 2.6, 27, 28 и 29.

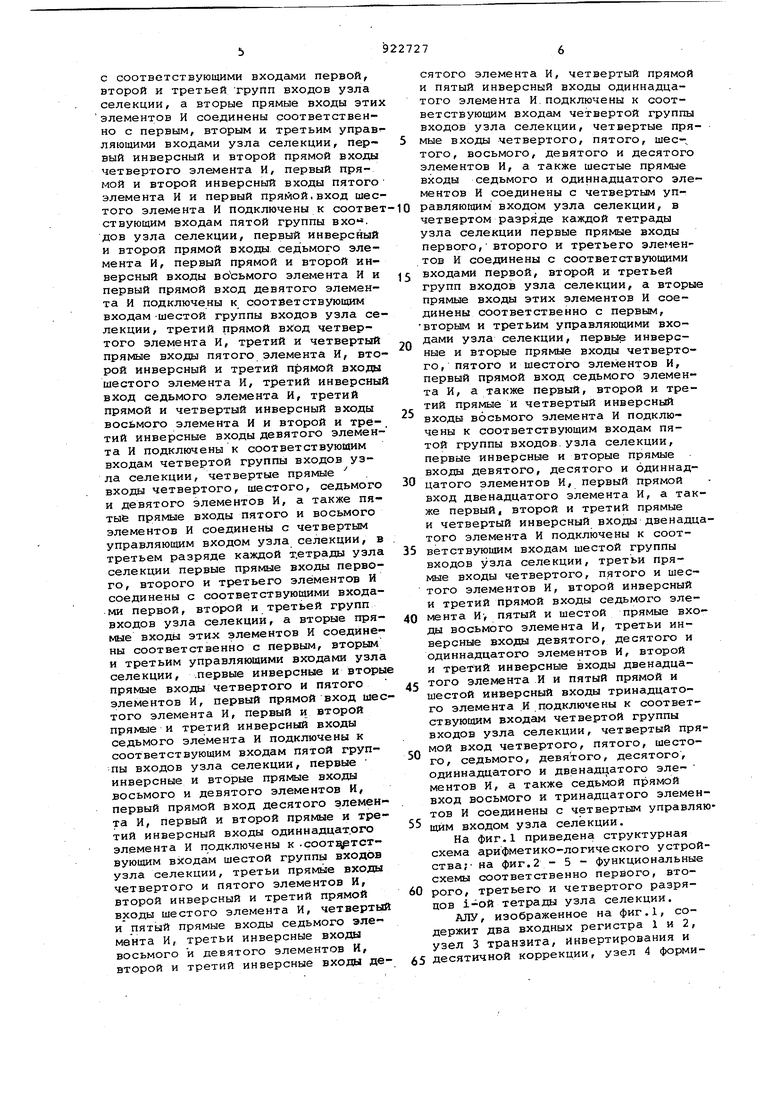

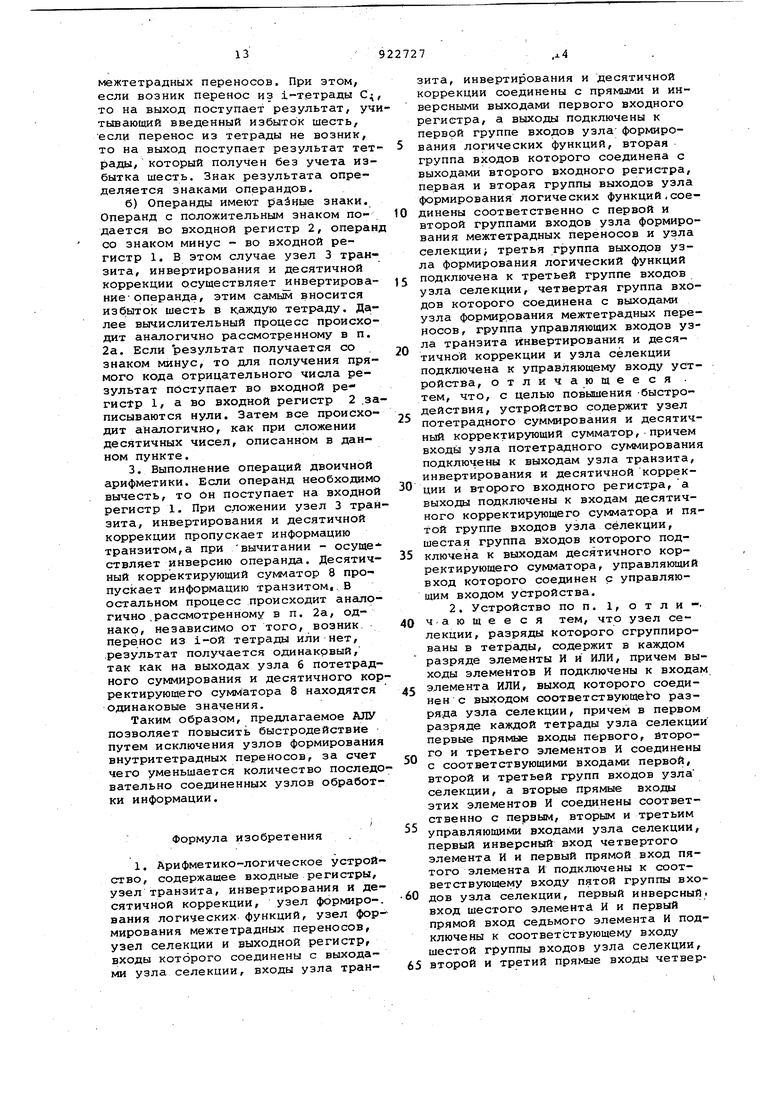

0 Второй разряд i-ой тетрады узла 7 селекции, изображенный на фиг.З содержитэлемент И 32, первый прямой, вход которого соединен с выходом G, значения функции И узла 4 формирова5 НИН логических функций, значение поступает на выход узла 7 селекции при наличии на втором прямом входе элемента И 32 управляющего сигнала 21 элемент И 33, первый прямой вход ко0торого соединен с выходом Т ii значения функции-ИЛИ узла 4 формирова-. ния логических функций, значение Tij, .поступает на выход узла 7 селекции при наличии на втором прямом входе

C элемента И 33 управляющего сигнала 23, элемент И 34, первый прямой вход которого- соединен с выходом Hiiv значения функции Исключающее ИЛИ узла 4 формирования логических функций, значение Н (j поступает на выход узла 7 селекции при наличии на втором прямом входе элемента И 34 управляющего сигнала 25, выход S значения суммы узла 6 потетрадного суммирования соединён с первым ин-

5 версным уходом.элемента И 35 и первым прямым входом элемента И 36, а выход S Q,- соединен с вторым прямым входом элемента И 35, вторым инверсным входом .элемента И 36 и с

0 первым прямым входом элемента. И 37, выход значения суммы десятичного корректирующего сумматора 8 соединен с первым инверсным входом элемента И 38 и первым прямым входом

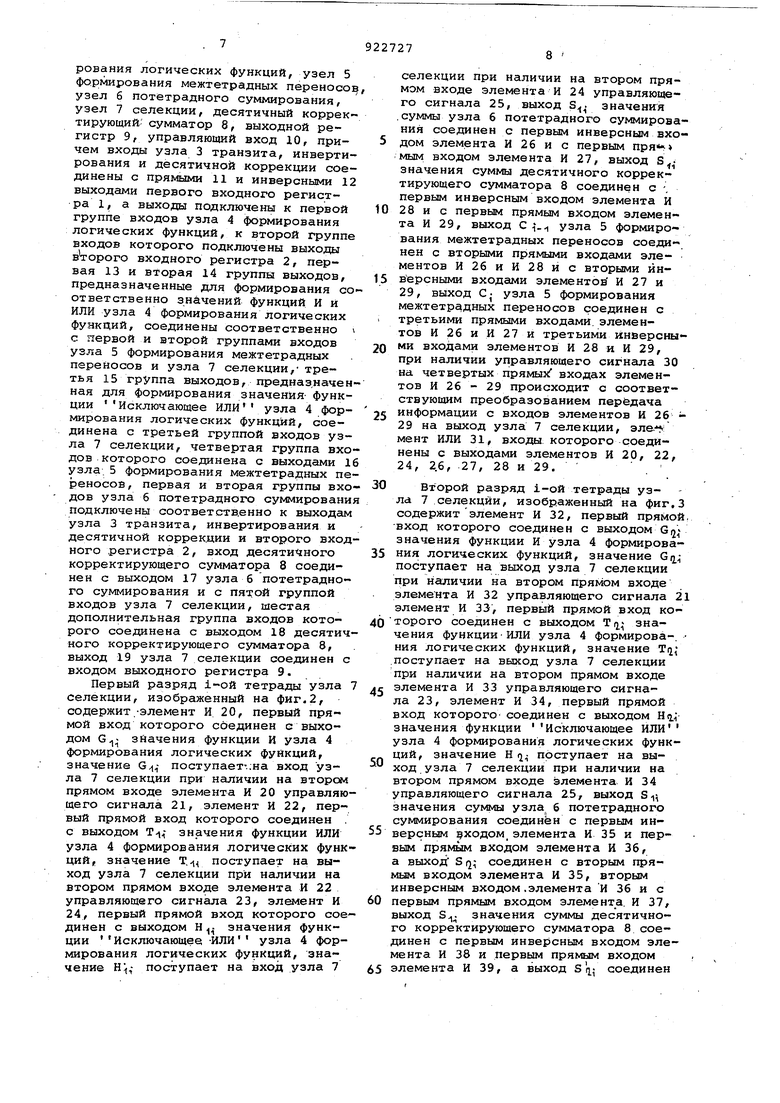

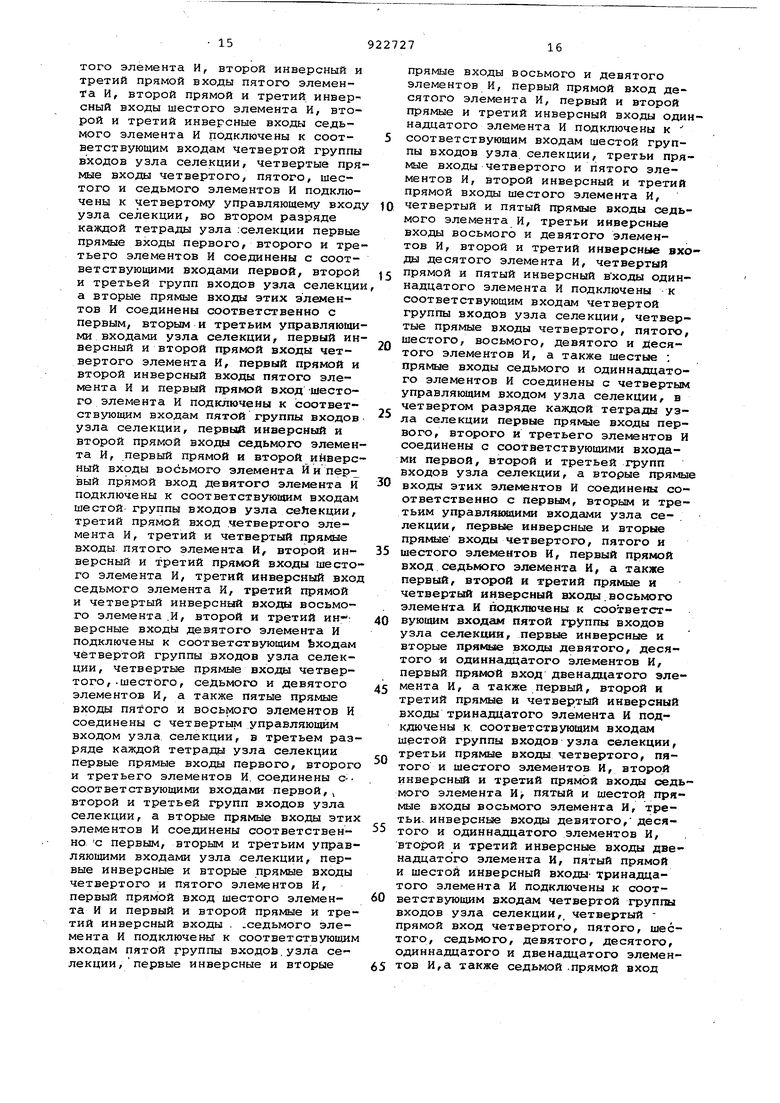

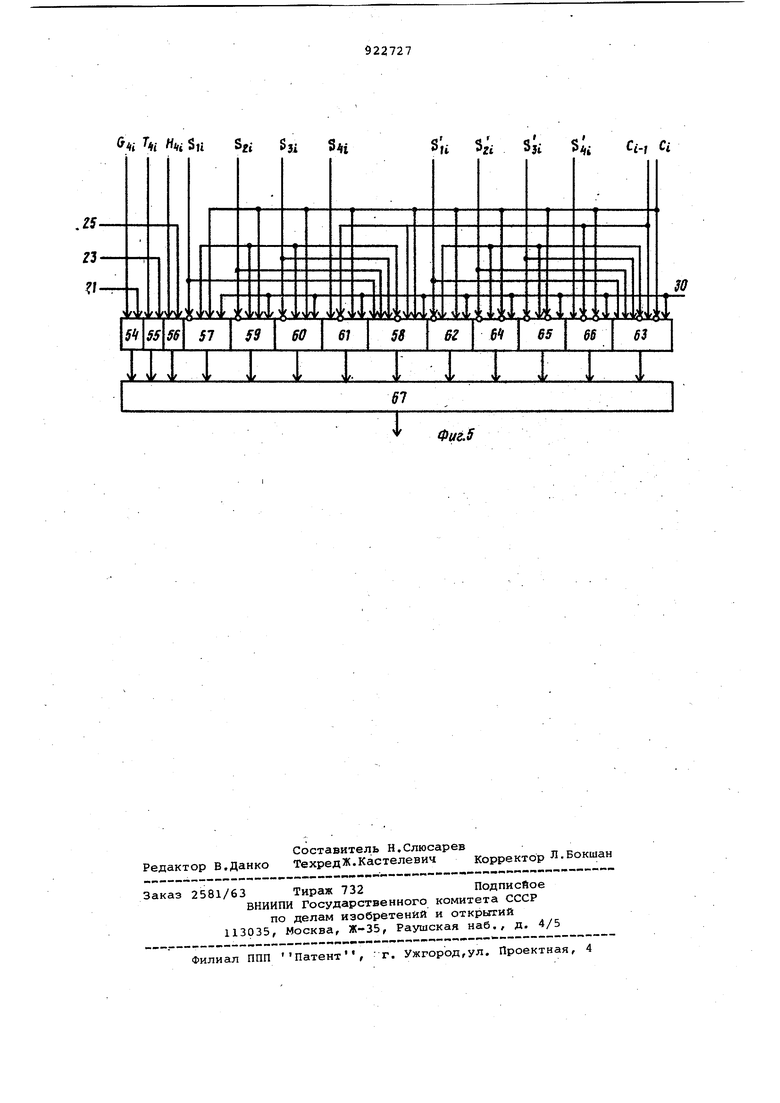

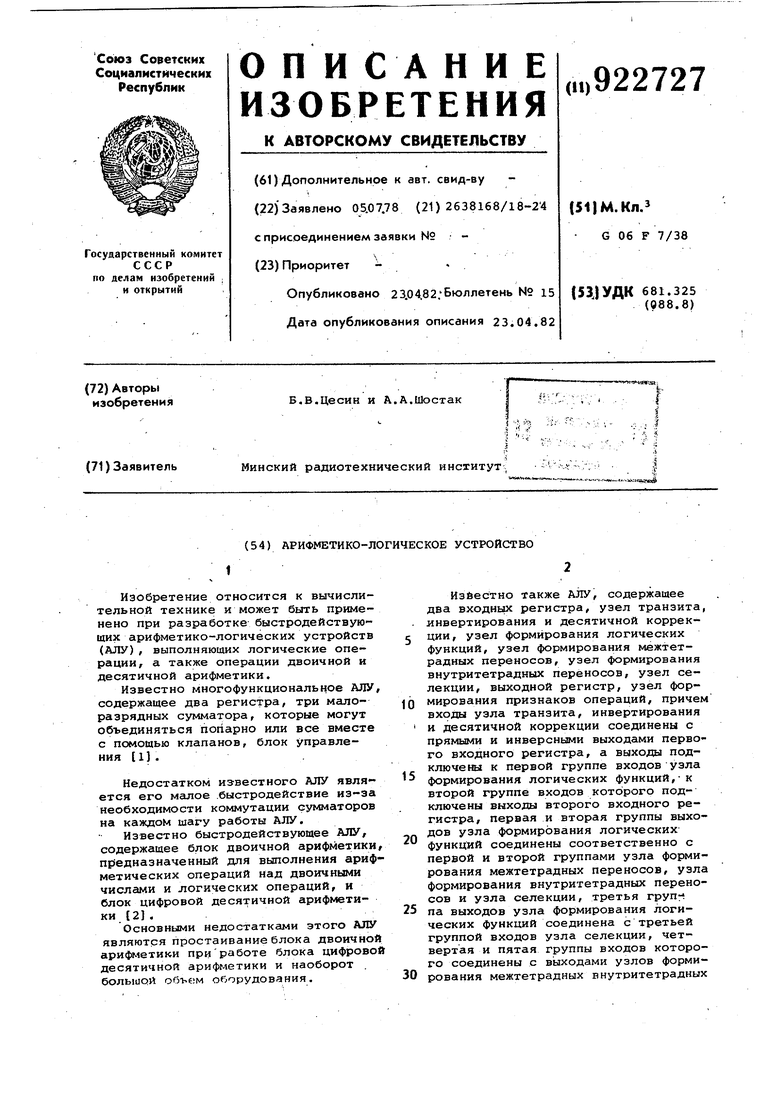

5 элемента И 39, а выход S li соединен с вторым прямым входом Элемента И 38, вторым инверсным входом элемен та И 39 и с первым прямым входом элемента И 40, выход С. узла 5 формирования межтетрадных переносов соединен с третьими прямыми входами элементов И 36 и 39 с вторыми ин версньми входами элементов Я 37 и 40, выход С соединен с третьими прямыми-входами элементов И 35 и 37 с третьими инверсными входами элементов И 38 и 40, с четвертым прямым входом элемента И 36 и четвертым инверсным входом элемента И 39, при наличии управляющего сигнала 30 на четверть : прямых входах элементов И 35, 37, 38 и 40 и на пятых прямых входах элементов И 36 и 39 происходит передача информации с входов элементов И 35 - 40 на выход узла 7 селекции, элемент ИЛИ 41, входы которого соединены с выходами элементов И 32 - 40., Третий разряд i-ой тетрады узла селекции, изображенный на фиг.4, содержит элемент И 42, первый вход которого соединен с выходо Gj значения функции И узла 4 форми рования логических функций, значе ние GT,, поступает на выход узла 7 селекции при нгшичии на втором прямом входе элемента И 42 управляйтего сигнала 21, элемент И 43, первый прямой вход которого соединен с выходом Tjij значения функции ИЛИ узла 4 формирования логических функци значение Т -у поступает на выход узла 7 при наличии на втором прямом входе элемента И 43 управляющего сигнала 23, элемент И 44, первый прямой вход которого соединен с выходом Hj; значения функции Исключающее ИЛИ узла 4 формирования логических функций, значение Hij по ступает на выход узла 7 селекции пр наличии на втором прямом входе элемента И 44 управляющего сигнала 25 выход S значения суммы узла 6 потетрадного суммирования соединен с первым инверсным входом элемента И и с первым прямым входом элемента И 46, выход Sij; суммы узла 6 потетрадного суммирования соединен с первым инверсным входом элемента И 47 и вторым прямым входом элемента И 46, выход S3,- узла б потетрадного сук®лирования соединен с вторыми прямыми входами элементов И 45 и 47, с первым прямым вхо-г дом элемента И 48 и с третьим инвер ным входом элемента И 46, выход 6 значения суммы десятичного корректирующего сумматора 8 соединен с первым инверсным входом элемента И 49 и с первым прямым входом элемента И 50, выход , значения суммы десятичного корректирующего суммато ра 8 соединен с первым инверсным входом элемента И 51 и с вторым прямым входом элемента И 50, выход Sj; суммы десятичного корректирующего сумматора 8 соединен с вторыми прямыми входами элементов И 49 и 51, с первым прямым входом элемента И 52 ,и с третьим инверсным входом элемента И 50, выход С;. узла 5 формирования межтетрадных переносов соединен .с вторыми инверсными входами элементов И 48 и 52, с четвёртыми прямыми входами элементов И 46 и 50, выход С; соединен с третьими прямыми входами элементов И 45, 47 и 48, с пятым прямым входом элемента И 46, с третьими инверсными входами элементов И 49, 51 и 52 и с.пятым инверсным входом элемента И 50, при наличии управляющего сигнала 30 на четвертых прямых входах элементов И 45, 47, 48, 49, 51.и 52 и на шестых прямых входах элементов И46 и 50 происходит с соответствующим преобразованием передача информации с входов элементов И 45 - 52 на вьйсод узла 7 селекции, элемент ИЛИ 53, входы которого соединены с выходами элементов И 42 - 52. Четвертый разряд 1-ой тетрады узла 7 селекции, изображенный на фиг.5 содержит элемент И 54, первый прямой вход которого соединен с выходом значения функции И узла 4 формирования логических функций, значение Сд поступает на выход уз ла 7 селекции при нгшичии на втором прямом входе элемента И 54 управляющего, сигнала 21, элемент И 55, первый прямой вход которого соединен с выходом T4i значения функции ИЛИ узла 4 формирования логических функций, значение Т 4; поступает на выход узла 7 селекции при наличии на втором прямом входе элемента И 55 управляющего сигнала 23, элемент И 56, первый прямой вход которого соединен с выходом Н 4, значения функции Исключающее ИЛИ узла 4 формирования логических функций, значение Н 4i поступает на выход уз-ла 7 селекции при наличии на втором прямом входе элемента И 56 управляющего сигнала 25, выход S i значения . суммы узла 6 .потетрадного суммирования соединен с первым инверсным входом элемента И 57 и с первым прямым входом элемента И 58, выход S ij-, : значения суммы узла 6 потетрадного суммирования соединен с первым инверсным входом элемента И 59 и с вторым прямым входом элемента И 58, выход БЗ зня1чения суммы узла 6 потетрадного суммирования соединен с первым инверсным входом элемента И 60 и с третьим прямым входом элемента И э8, выход значения суммы узла 6 потетрадного суммирования соединен с вторыми прямыми входами злементов И 57, 59 и 60, с первым прямым входом элемента И 61 и с четвертым инверсным входом элемента И 58, выход S значения суммы десятичного корректирующего сумматора.8 соединен с первым инверсным входом элемента И 62 и с первым прямым входом элемента и 63, выход значения суммы десятичного корректирующего сумматора 8 соединен с первым инверсным входом элемента И 64 и с вторым прямым входом элемента И 63, выход Sj; значения суммы десятичного корректирующего суМматора 8 соединен с первьш инверсным входом элемента и 65 и с третьим прямым входом элемента И 63, выход SJ значения суммы десятичного корректирующего сумматора 8 соединен с вторыми прямыми входами элементов И 62, 64 и 65, с первым прямым входом элемента И 66 и с четвертым инверсным входом элемента И 63, выход С i узла 5 формирования межтетрадных переносов соединен с вторыми инверсными входами элементов И 61 и 66 и с пятыми прямыми входами элементов И 58 и 63, выход С соединен с третьими прямыми входами элементов И 57, 59, 60 и 61, с третьими инверсными взводами элементов И 62, 64,65 и 66, с шестым прямым входом элемента И 58 и с шестыминверсным входом элемента И 63,.при наличии управляющего сигнала 30 на четвертых прямых вхсг дах элементов И 57, 59, 60 61, 62, 64, 65 и 66 и на седьмых прямых входах элементов И 58 и 63 происходит с соответствующим преобразованием передача информации с входов элементов И 57 - 66 на выход узла 7 се.лекции, элемент .ИЛИ 67, входы которого соединены с выходами элементов И 54 - 66,

В АЛУ входные регистры 1 и 2 мотут быть выполнены на двухтактных D-триггерах, Предполагается, что узел транзита, инвертирования и десятичной коррекции, узел 4 формирования логических функций, узел 5 формирования межтетрадных переносов узел 6 потетрадного суммирования, узел .7 селекции и десятичный корректирующий сумматор 8 выполнены в виде комбинационных схем. В качестве узла 3 транзита, инвертирования и десятичной коррекции используется коммутационная схема, содержащая в каждом разряде элементы И,, выходы которых соединены с входами элемента ИЛИ, а также содержащая потетрадный сумматор, .прибавляющий число 6 (двоичныйкод ) к значениК поступающему с прямого выхода 11 первого входного .регистра 1, Узел 4 формирования логических фукнций содержит в каждом разряде элементы И,

ИЛИ, исключающее ИЛ.. Узел 5 формирования межтетрадных переносов выполнен на элементах И-ИЛИ и формирует групповой перенос в каждую тетраду по параллельной схеме. Узел 6 потетрадного суммирования содержит в каждой тетраде сумматор с параллельным переносом Узел 7 селекции выполнен на элементах И и ИЛИ, его функциональная схема приведена на фиг.2 - 5, Десятичный корректирующий сумматор 8 содержит коммутатор на элементах И-ИЛИ, содержащий на входе потетрадный сумматор, прибавляющий число 10 к значению, постпающему на его вход, с игнорированием возникающего при этом переноса из тетрады (этим самым осуществляется вычитание шести). Выходной регистр 9 может быть реализован на двухтактных D-триггерах.

АЛУ работает следующим образом.

а) Операнды имеют одинаковые знаки. В этом случае они обрабатываются в прямых кодах. Операнды поступают на входные регистры 1 и 2. Узе 3 транзита, инвертирования и десятичной коррекции осуществляет увеличение каждой десятичной цифры на шесть . Межтетрадные переносы в узле формируются с учетом избытка, введенного в каждую десятичную цифру. В узле 6 потетрадного суммирования производится потетрадное сложение операндов, поступающих на входы узла 6. Десятичный корректирующий сумматор 8 осуществляет уменьшение каждой потетрадной суммы, поступающей с выхода узла 6 потетрадного суммирования, на шесть. В узле 7 селекции осуществляется прибавление к значениям сумм i-ой тетрады, поступающим на пятую и шестую группы входов узла 7 селекции соответственно с выходов узла 6 потетрадного суммирования и -десятичного корректирующего сумматора 8, значения переноса С;. в данную тетраду, которо формируется узлом 5 формирования межтетрадных переносов. При этом, если возник перенос из i-тэтрады С то на выход поступает результат, у тьшающий введенный избыток шесть, если перенос из тетрады не возник, то на выход поступает результат тет рады, который получен без учета из бытка шесть. Знак результата определяется знаками операндов. б) Операнды имеют равные знаки. Операнд с положительным знаком по дается во входной регистр 2, опера со знаком минус - во входной регистр 1. В этом случае узел 3 тран зита, инвертирования и десятичной коррекции осуществляет инвертирова ние- операнда, этим самым вносится изб1Ыток шесть в к,аждую тетраду. Да лее вычислительный процесс происхо дит аналогично рассмотренному в п. 2а. Если результат получается со знаком минус, то для получения прямого кода отрицательного числа результат поступает во входной регистр 1, а во входной регистр 2 .за писываются нули. Затем все происходит аналогично, как при сложении десятичных чисел, описанном в данном пункте. 3. Выполнение операций двоичной арифметики. Если операнд необходимо вычесть, то он поступает на входной регистр 1. При сложении узел 3 тран зита, инвертирования и десятичной коррекции пропускает информацию транзитом,а при вычитании - осуществляет инверсию операнда. Десятичный корректирующий сумматор 8 пропускает информацию транзитом, В остальном процесс происходит аналогично .рассмотренному в п. 2а, однако, независимо от того, возник, перенос из i-ой тетрады или нет, .результат получается одинаковый, так как на выходах узла 6 потетрадного суммирования и десятичного кор ректирующего сумматора 8 находятся одинаковые значения. Таким образом, предлагаемое АЛУ позволяет повысить быстродействие путем исключения узлов формирования внутритетрадных переносов, за счет чего уменьшается количество последо вательно соединенных узлов обработки информации. Формула изобретения 1. Арифметико-логическое устройство, содержащее входные регистры, узел транзита, инвертирования и десятичной коррекции, узел формиро-. вания логических функций, узел формирования межтетрадных переносов, узел селекции и выходной регистр, входы которого соединены с выходами узла селекции, входы узла транзита, инвертирования и десятичной коррекции соединены с прямыми и инверсными выходами первого входного регистра, а выходы подключены к первой группе входов узла- формирования логических функций, вторая группа входов которого соединена с выходами второго входного регистра, первая и вторая группы выходов узла формирования логических функций,соединены соответственно с первой и второй группами входов узла формирования межтетрадных переносов и узла селекции; третья группа выходов узла формирования логический функций подключена к третьей группе входов узла селекции, четвертая группа входов которого соединена с выходами узла формирования межтетрадных переносов , группа управляющих входов узла транзита и:н8ертирования и десятичной коррекции и узла селекции подключена к управляющему входу устройства, отличающееся . тем, что, с целью повышения -быстродействия, устройство содержит узел потетрадного суммирования и десятичный корректирующий сумматор,причем входы узла потетрадного суммирования подключены к выходам узла транзита, инвертирования и десятичной коррекции и второго входного регистра,а выходы подключены к входам десятичного корректирующего сумматора и пятой группе входов узла селекции, шестая группа входов которого подключена к выходам десятичного корректирующего сумматора, управляющий вход которого соединен с управляющим входом устройства. 2. Устройство по п. 1, о т л и - ч-ающееся тем, что узел селекции, разряды которого сгруппированы в тетрады, содержит в каждом разряде элементы И и ИЛИ, причем выходы элементов И подключены к входам элемента ИЛИ, выход которого соединен с выходом соответствующего разряда узла селекции, причем в первом разряде каждой тетрады узла селекции первые прямые входы первого, йторого и третьего элементов И соединены с соответствующими входами первой, второй и третьей групп входов узла селекции, а вторые прямые входы этих элементов И соединены соответственно с первым, вторым и третьим управляющими входами узла селекции, первый инверсный вход четвертого элемента И и первый прямой вход пятого элемента И подключены к соответствующему входу пятой группы входов узла селекции, первый инверсный вход шестого элемента И и первый прямой вход седьмого элемента И подключены к соответствующему входу шестой группы входов узла селекции, второй и третий прямые входы четвертого элемента И, второй инверсный и третий прямой входы пятого элемента И, второй прямой и третий инверсный входы шестого элемента И, второй и третий инверсные входы седьмого элемента И подключены к соответствующим входам четвертой группы входов узла селекции, четвертые прямые входы четвертого, пятого, шестого и седьмого элементов И подключены к четвертому управляющему входу узла селекции, во втором разряде каждой тетрады узла .селекции первые прямые входы первого, второго и третьего элементов И соединены с соответствующими входами первой, второй и третьей групп входов узла селекции а вторые прямые входы этих элементов И соединены соответственно с первым, вторым и третьим управляющи ми входами узла селекции, первый ин версный и второй прямой входы четвертого элемента И, первый прямой и второй инверсный входы пятого элемента и и первый прямой вход-шестого элемента И подключены к соответствующим входам пятой группы входов узла селекции, первый инверсный и второй прямой входы седьмого элемен та И, первый прямой и второй инверс ный входы восьмого элемента И и первый прямой вход девятого элемента И подключены к соответствующим входам шестой группы входов узла сейекции, третий прямой вход .четвертого элемента И, третий и четвертый прямые входы пятого элемента И, второй инверсный и третий прямой входы шестого элемента И, третий инверсный вход седьмого элемента И, третий прямой и четвертый инверсный входы восьмого элемента .И, второй и третий версные входы девятого элемента И подключены к соответствующим Ьходам четвертой группы входов узла селекции, четвертые прямые входы четвертого, -шестого, седьмого и девятого элементов И, а также пятые прямые входы пятого и восьмого элементов И соединены с четвертым управляющим входом узла селекции, в третьем разряде каждой тетрады узла селекции первые прямые входы первого, второго и третьего элементов И. соединены с-соответствующими входами первой, второй и третьей групп входов узла селекции, а вторые прямые входы этих элементов И соединены соответственно С первым, вторым и третьим управляющими входами узла селекции, первые инверсные и вторые прямые входы четвертого и пятого элементов И, первый прямой вход шестого элемента И и первый и второй прямые и третий инверсный входы . .седьмого элемента И подключены к соответствующим входам пятой группы входоь.узла селекции, первые инверсные и вторые прямые входы восьмого и девятого элементов И, первый прямой вход десятого элемента И, первый и второй прямые и третий инверсный входы одиннадцатого элемента и подключены к соответствующим входам шестой группы входов узла селекции, третьи прямые входы четвертого и пятого элементов И, второй инверсный и третий прямой входы шестого элемента И, четвертый и пятый прямые входы седьмого элемента И, третьи инверсные входы восьмого и девятого элементов И, второй и третий инверсные входы десятого элемента И, четвертый прямой и пятый инверсный входы одиннадцатого элемента И подключены -к соответствующим входам четвертой группы входов узла селекции, четвертые прямые входы четвертого, пятого, шестого, восьмого, девятого и десятого элементов И, а также шестые : прямые входы седьмого и одиннадцатого элементов И соединены с четвертым управляющим входом узла селекции, в четвертом разряде каждой тетрады узла селекции первые прямые входы первого, второго и третьего элементов И соединены с соответствующими входами первой, второй и третьей групп входов узла селекции, а вторые прямые входы этих элементов И соединены соответственно с первым, вторым и третьим управляющими входами узла селекции, первые инверсные и вторые прямые входы четвертого, пятого и шестого элементов И, первый прямой вход седьмого элемента И, а также первый, второй и третий прямые и четвертый инверсный входы.восьмого элемента И подключены к соответствующим входам пятой группы входов узла селекоия, первые инверсные и вторые прямые входы девятого, десятого я одиннадцатого элементов И, первый прямой вход двенадцатого элемента И, а также первый, второй и третий прямые и четвертый инверсный входы тринадцатого элемента И подкдючены к соответствующим входам шестой группы входов узла селекции, третьи прямые входы четвертого, пятого и шестого элементов И, второй инверсный и третий прямой входы седьмого элемента и пятый и шестой прямые входы восьмогчз элемента И, третьи инверсные входы девятого, десятого и одиннадцатого элементов И, второй и третий инверсные входы двенаддатого элемента И, пятый прямой и шестой инверсный входы- тринадцатого элемента И подключены к соответствующим входам четвертой группы входов узла селекции, четвертый прямой вход четвертого, пятого, шестого, седьмого, девятого, десятого, одиннадцатого и двенадцатого элементов И,а также седьмой .прямой вход

восьмого и тринадцатого элементов и соединены с четвертым управляющим входом узла селекции.

Источники информации, принятые во внимание при экспертизе

(

}7

(S)

10

($)

W

с. 206-213.

кл. G Об F 7/38, 1977 (прототип).

и

12

W

J

/(

Jf (Н)

13 (&)

П (Г)

iS

(С)

IL IL

21 Ф Ф w fe.y,ok 35 I

f t

% Гц

i $ti

% Sji

L

13 Z} -2l { w f

/

f

f

W 1 л Sk у W «...Q

I

Фиг. 3

Ci-;

Sii Sji M w ч y w 9

WM/

S3 f y O Т О-Т I ir ,Q. T, I Ljii- D i SO ii 4i Sii Sji S iSji

Фиг.5 Sji Ci-, Ct

Авторы

Даты

1982-04-23—Публикация

1978-07-05—Подача