(54) УСТРОЙСТВО ДЛЯ СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметико-логическое устройство | 1978 |

|

SU922727A1 |

| Устройство для деления десятичных чисел | 1976 |

|

SU744562A1 |

| Устройство для умножения | 1988 |

|

SU1670685A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

| Устройство для умножения | 1988 |

|

SU1578711A1 |

| Устройство для суммирования и вы-чиТАНия дВОичНО-дЕСяТичНыХ КОдОВ | 1978 |

|

SU813415A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1977 |

|

SU693369A1 |

| Арифметико-логическое устройство | 1977 |

|

SU703808A1 |

| Суммирующее устройство с контролем | 1983 |

|

SU1140112A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

1

Изобретение относится к вычислительной технике и может быть использовано для выполнения операций десятичной арифметики чисел, записанных в двоично-десятичной системе счисления.

Известно арифметико-логическое устройство, содержащее два входных регистра, два узла транзита, инвертирования и десятичной коррекции, узел,д формирования логических функций, узлы формирования межтетрадных переносов, узел поразрядной селекции и выходной регистр 1 Т.

Данное устройство обеспечивает повышение быстродействия арифметико-логического устройства при обработке десятичных чисел за счет расширения аппаратуры. Це; есообразно его исполь-2о зовать при параллельной обработке одной-двух цифр и построении схем на Элементах мал1 й cTenon-i интеграции, однако оно (irf/(fii при iicnnrih: oBaнии элементов большой или средней степени интеграции, так как элементы БИС (большой интегральной схемы) типа сумматоров имеют широкий спектр выполняемых функций и двоичное суммирование составляет лишь часть функций элемента. Поэтому дублирование элементов с целью повышения быстродействия суммирования приводит к их недоиспользованию по другим функ 4иям-.

Наиболее близким к предлагаемому является устройство для суммирования двоично-десятичных чисел, содержащее основной сумматор и два корректирующих сумматора, первый из которых со5единен с входами первого операнда и осуществляет его предварительную коррекцию на +6.

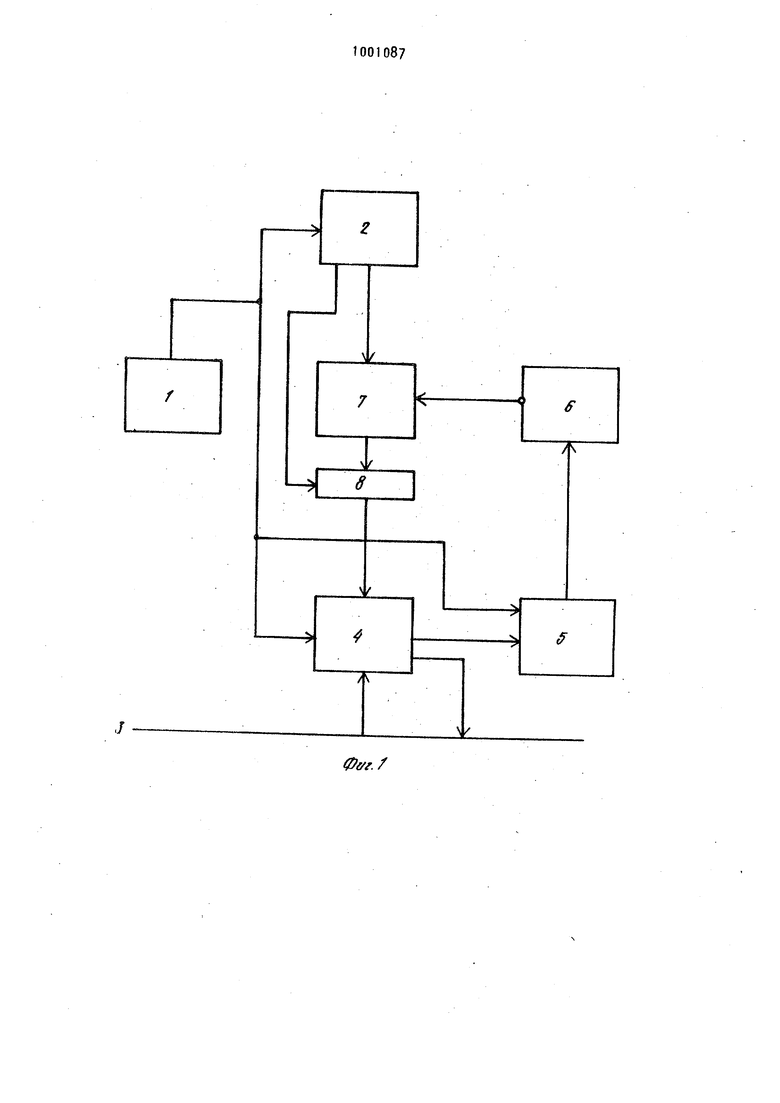

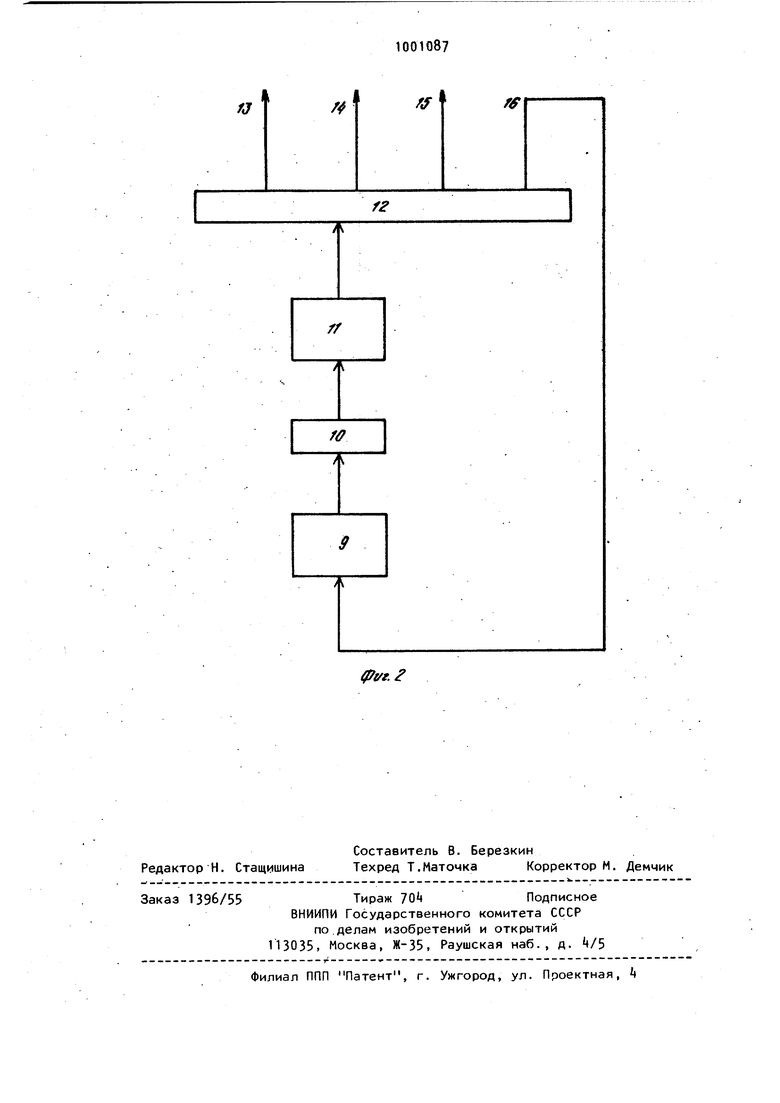

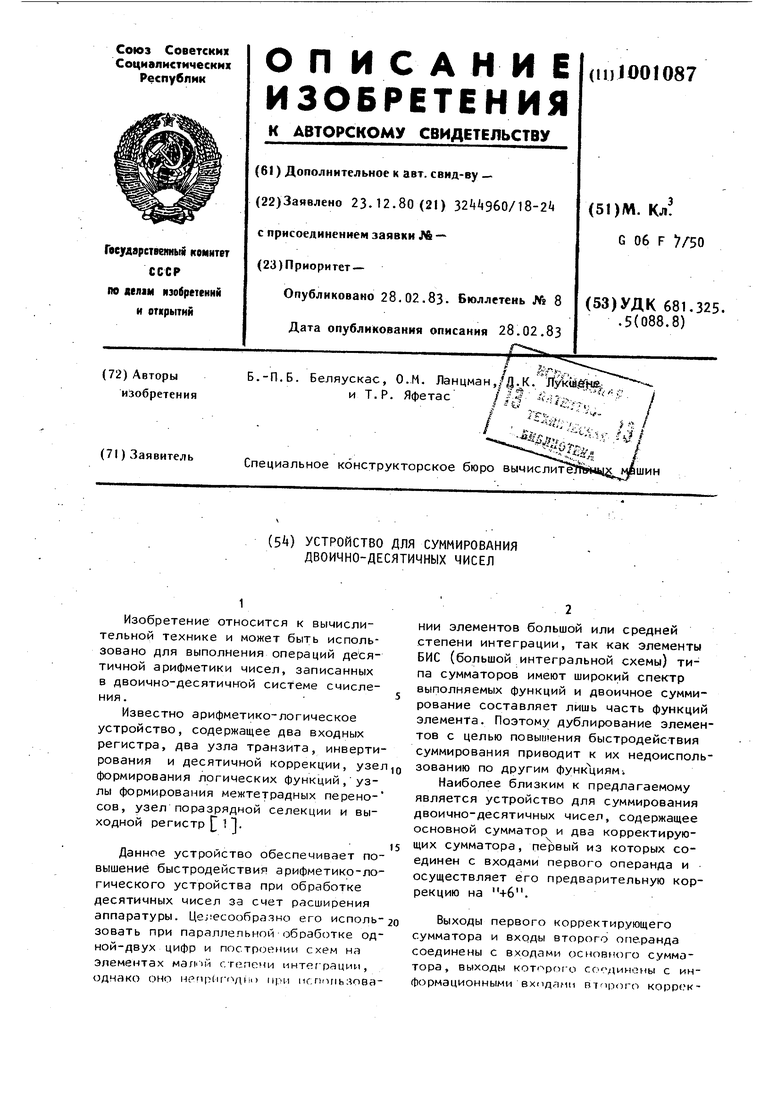

Выходы первого корректирующего сумматора и входы второго операнда соединены с входами основного сумматора , выходы которого соединены с информационными вхпд,ии1 BTopdrt) KOppf.Kтирующего сумматора, осуществляющего коррекцию на -6. Управление коррекцией при этом осуществляется сигналами отрицания переноса из тетрад основ ного сумматора C2j. Недостатком известного устройства является сравнительно больиюе количес тво оборудования, связанное с использованием трех полноразрядных сумматоров. Цель изобретения - упрощение устройства. Поставленная цель достигается тем что устройство для суммирования двоично-десятимных чисел, содержащее сумматор, генератор констант, группы элементов И, блок управления, первый и второй выходы которого соединены с управляющими .входами генератора констант и сумматора, первая группа входов сумматора соединена с информационными входами устройства, выходы переносов тетрад сумматора соединены с первыми входами элементов И первой группы, содержит регистр и группу элементов ИЛИ, входы которых соединены с соответствующими выходами первой группы генератора констант и элемен тов И второй группы, первые входы которых соединены с соответствующими выходами второй группы генератора констант, а вторые входы - с соответствующими инверсными выходами регистра, входы которого соединены с выходами элё 1ентйв И первой группы, вторые вхо ды которых соединены с третьим выходом блока управления, выходы элементов ИЛИ группы подключены к второй группе входов сумматора, выходы которого соединены с выходами устройства. На фиг. 1 показана блок-схема арифметико-логического устройства; на фиг. 2 - конструкция блока управления Устройство содержит микропрограммный блок Г управления, предназначенный для выдачи управляющих сигналов, разрешающих выполнение определенного алгоритма операций в устройстве, генератор 2 констант, предназначенный для выдачи констант под управлением блока 1, шину 3 данных, представляющую собой магистраль передачи данных между источниками и приемниками информации и соединенную с входами и выходами устройства, сумматор , выполняющий под управлением блока 1 операции над данными, представленными по две цифры в байтовом формате, группу элементов И 5, информационными входами которых являются выходы межтетрадных (межцифровых) переносов сумматора k, а управляющими входаМи - соответствующий выход блока управления 1, регистр 6, предназначенный для хранения переносов, вход которого подключен к выходам элементов И 5. группу элементов И 7, входами которых являются выходы генератора констант 2 и инверсные выходы разрядов регистра 6, группу элементов ИЛИ 8, одни входы которых подключены к выходам элементов И 7, а другие входы - к выходам генератора 2 констант. Блок 1 управления содержит узел 9 формирования адреса, регистр 10 адреса , узел 11 памяти микрокоманд и регистр 12 микрокоманд, выходы которого (соответствующие различным информационным полям регистра) соединены соответственно с управляющими входами генератора 2 констант, сумматора , элементов И 5 группы и входами узла 9. на который также поступают из вне тактовые сигналы. Устройство работает следующим образом. При сложении десятичных цифр с одинаковыми знаками первый операнд, поступающий по шине 3 данных, под упра влением блока 1 принимается сумматором k и складывается с кодом 6, формируемым генератором 2 констант и без изменений проходящим через элементы ИЛИ 8, т.е. первый операнд подготавливается в коде с избытком 6. Второй операнд, поступающий по шине 3 данных, добавляется к первому операнду, подготовленному с избытком 6, и межтетрадные переносы, полученные при сложении двух операндов через элементы И 5 под управлением блока 1 заносятся в регистр 6. В цикле коррекции десятичного результата под управлением блока 1 генератор 2 констант выдает единственную константу коррекции АДА..., где число корректирующих шестнадцатеричных А равно параллельно обрабатываемому количеству десятичных цифр. Эта константа модифицируется путем логического умно кения каждой тетрады константы с инверсным выходом соответствующего бита регистра 6 с помощью элементов И 7 и через элементы ИЛИ 8 поступает в сумматор f, где складывается с двоичными разрядами суммы, полученной при 5 сложении двух операндов. В результате получается откорректированная сум ма в двоично-десятичном коде. Например 783 + 1957 9791 Первый операнд в коде с избытком 6 будет 783 k D Е 9 А 1101 1110 1001 1010 При суммировании с вторым операндом он дает на одном выходе сумматора Ц двоичную сумму, а на другом переносы1101 1110 1001 1010 1111 0111 1111 . 0001 (двоичная сумма) О 1 О 1 (переносы) Наличие переноса с первой и треть ей тетрад двоичной суммы означает, что их содержание соответствует значе нию десятичного разряда без коррекци так как для них значение переноса 16 покрывает десятичный перенос и компенсирует избыток 6 первого операнда (10 + 6 16). Тетрады без переносов в старшую тетраду должны дополняться шестнадцатиричным числом А 1010 с тем, чтобы вместе с избытком 6 первого операнда образовывать перенос и в результате этого в тетрадах получить сумму слагаемых с компенсированным избытком 6 н дополнением А. Для этого содержание регист ра 6 0101 поступает с инверсного выхода в виде 1010 на входы элементов И 7, на выходе которых ;получается модифицированная константа коррекции I АААА А 1010 АОАО. DI В сумматоре ч она суммируется с двоичной суммой 1111 0111 1111 0001 двоичнаясумма 1010 0000 1010 0000 констан та коррекции1001 01il 1001 0001 десятич ный результати получается окончательнь1й результат 9791. 87« В случае вычитания операндов, т.€. сложения операндов противоположных знаков, первый операнд подается на устройство в прямом коде, а второй в дополнительном двоичном коде и получается двоичная сумма, коррекция которой выполняется аналогично. Предлагаемое устройство эффективно может использоваться также для логической обработки данных по маске. При этом- вместо сумматора Ц необходимо использовать арифметико-логический блок. За счет использования одного сумматора вместо трех, как в прототипе, осуществляется упрощение устройства. Формула изобретения Устройство для суммирования двоично-десятичных чисел, содержащее сум- . матор, генератор констант, группы элементов И, блок управления, пврвь1й и второй выходы которого соединены с управляющими входами генератора констант и сумматора, первая группа вхо-г дов сумматора соединена с информационными входами устройства, выходы переносов тетрад сумматора соединены с первыми входами элементов.И первой -. группы, отличающееся тем, что, с целью упрощения устройства, оно содержит регистр и группу элементов ИЛИ, входь которых соединены с соответствующими выходами первой группы генератора констант и элементов И второй группы, первые входы которых соединены с соответствующими выходами второй группы генератора констант, а вторые входы - с соответствующими инверсными выходами регистра, входы которого соединены с выходами элементов И первой группы, вторые входы которых соединены с третьим выходом блока управления, выходы элементов ИЛИ группы подключены к второй группе входов сумматора, выходы которого соединены с выходами устройства. Источники информации, Принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 703808, кл. G 06 F 7/38, 19792.Беляускас Б.-П. Б. и др. Вычислительный комплекс М5100. Особенности аппаратурной реализации. М., Статистика, 1980, с. 75-78, рис. 4.23 (прототип) .

LC±

0fff.f

r

/J

/.f

ve.

Авторы

Даты

1983-02-28—Публикация

1980-12-23—Подача