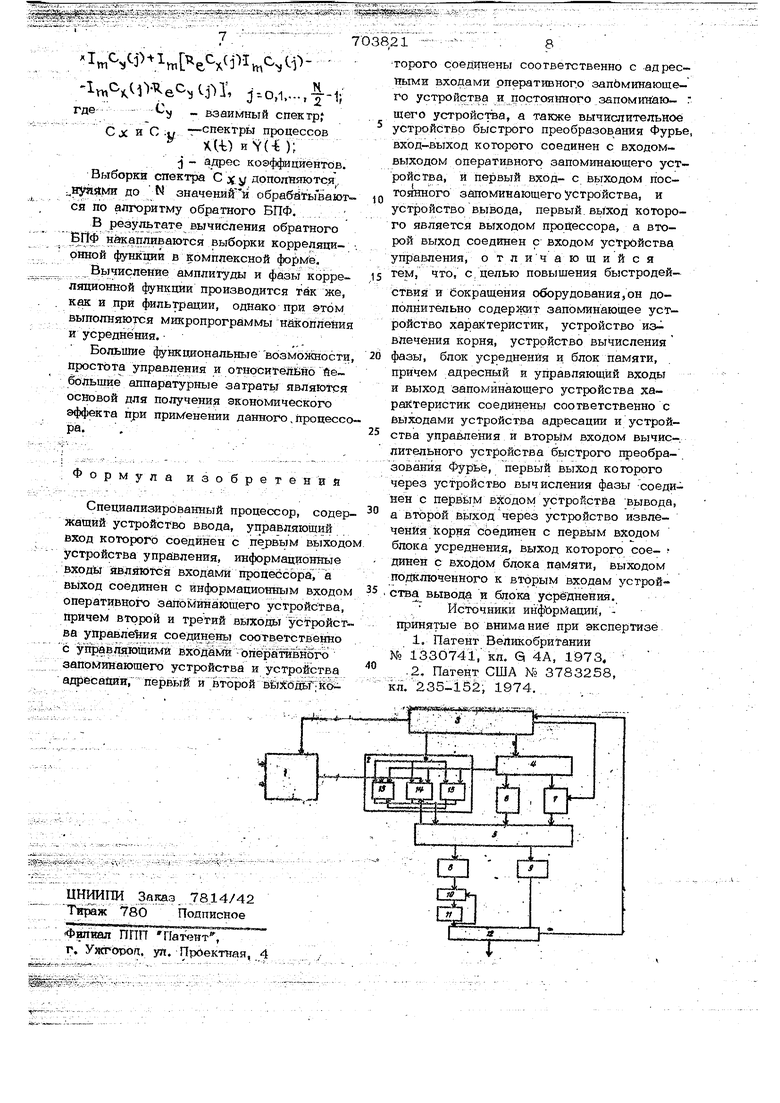

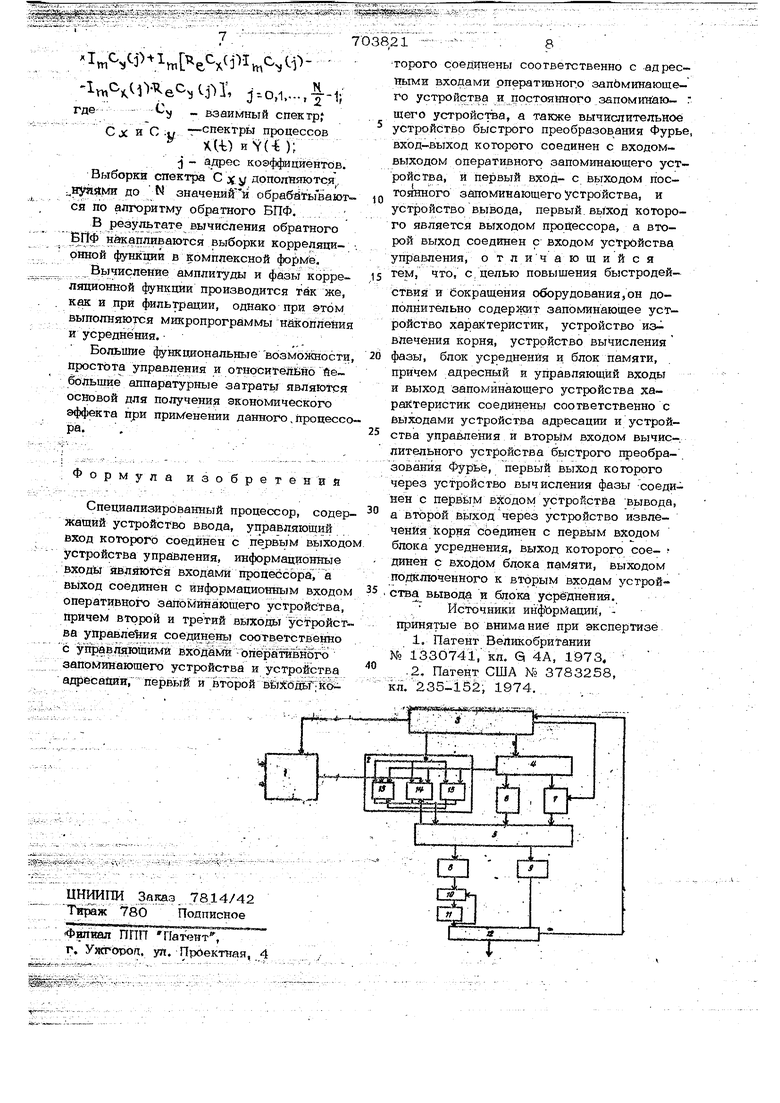

Изобретение относится к области вычислительной техники. Процессор, в частности, может быть использован для расчета в реальном NfacmTa6e времени спектральных компонентов сложного мноРдчястотного колебания, как цифровой прогрбм мируемый. фильтр, для вычисления корреляционных функций и моделирования, объектов. Известна специализированная вычислительная машина, содержащая устройство управления, оперативное запоминающее устройство, центральный процессор, процессор массива ij . Недостатками известной машины являются наличие большого объема оборудования, недостаточное быстродействие и надежность. Наиболее близким к изобретению по технической сущности является специализированный процессор, содержащий устройство ввода, управляющий вход которого соединен с первым выходом устройстраупрая ения,. информационные входы ЯВЛЯЮТСЯ входами процессора, а вь1ход , соединен с информационным входом оперативного запомйнающетч) устройства, причем второй и третий выходы устройства управления соединены соответственно с .управляющими входами оперативного запоминающего устройства и устрЪйства Адресации, первый и второй выходы которого соединены ссиэтветственно с адресными входами оперативного зап|р минающего устройства и постоянного запоминающего устройства, а также вычислительное устройство быстрого 11реобразования Фурье, вход-выход которого соединен с входомвыходом оперативного запоминающего устройства, а первый вход - с выходом постоянного запоминающего устройства, и устройство вывода, первый выход которого является выходом процессора, а второй выход соединен с входом устройства управления 2 . Недостатками такого процессора являются большой объем оборудования и быстродействие. Цепью изобретения является повышение быстродействия и сокращение оборудования. Поставленная цепь достигается тем, что процессор допопнитепьно содержит запоминающее устройство характеристик, устройство извпечения корня, устройство вычиспения фазы, бпок усреднения и бпок памяти. Причем адресный, и управляющий входы и выход запоминающего устройства характеристик соединены соответственна с выходами устройства адресации и устройства управления и вторым входом вычислительного устройства быстрого преобразования Фурье, первый выход которого через устройство вычиспения фазы соединен с первым входом устройства вывода, а второй выход через устройство извлечения корня соединен с первым входом блока усреднения, выходом подключенного к входу блока памяти, выход которого соединен с вторыми входами устройства вывода и блока усреднения. На чертеже представлена ,блок-схема процессора, который содержит усТ1э6йство 1 ввода, оперативное запоминающее устройство (ОЗУ)2, устройство 3 управления устройство 4 адресации, вычислительное устройство 5 быстрого преобразования Фурье, постоянное запоминающее устройство (ПЗУ) 6, запоминающее устройство (ЗУ) 7 характеристик, устройство 8 извлечения корня, устройство 9 вычисления фазы, блок 10 усреднения, бпок 11 памяти, устройство 12 вывода. ОЗУ 2 состоит из трех блоков памяти 1 3, 14 и Л 5. Устройство управления 3 Построено по микропрограммному принципу и для увеличения быстродействия Bfce микропрограммы реализованы аппаратным методом, при этом последовательность микропрограмм может задаваться различной. ЗУ 7 хранит частотную характеристику реализуемого фильтра либо результа Т1 прямого БПФ при вычислении корреляционных функций, либо характеристики объектов моделирования. Процессор работает следующим обра.зом. При определении спектра мощности исследуемого сигнала в заданной полосе частот сигнал подается на вход устройства 1 ввода, где он квантуется по уровню и частоте, после чего выборки пискрйТногчэ сигнала умножаются на весовую 4 нкцию и заносятся в ОЗУ 2, причем каждый из блоков 13, 14, 15 позволяет одновременное считывание двух операндов при выполнении БПФ (многоканального буферного преобразования Фурье), Первоначально заполняется блок 13 , адреса записи которого формирует устойство 4. При заполнении блока 13 устройство 3 формирует сигнал конец занесения и все последующие выборки заносятся в блок 14. Одновременно устройство 3 вырабатывает сигнал начала iмикропрограммы прямого БПФ, в резуль-; тате чего устройство 4 формирует адреса для считывания операндов из блока 13, адреса значений тригонометрических функций в ПЗУ 6 и адреса записи резульTaiTOB вычислений в блок .15 согласно алгоритму прямого БПФ. Операнды, считанные из устройства 3 и ПЗУ 6, поступают в вычислительное устройство 5,которое согласно алгоритму прямого БПФ выполняет над ними сле/1ующие операции , .tKVA(i).vN, . где А (с шдексом) - комплексные числа; - . W-комплексный весовой коэффициент. Результаты указанных вычислений перемножаются на операнды, определяющие частотную характеристику фильтра и хранящиеся в 35 7 по алгоритму . п.шсн,фд где А. (.;() - комплексные коэффициенты Фурье;. Н.| (. J) - значения операндов частотной характеристики фильтра. По окончании микропрограммы свертки устройство 3 формирует микропрограмму обратного БПФ, при этом процессор работает как при прямом БПФ. Результат вычислений обратного БПФ представляет собой сигнал в заданной попосе частот, спектр мощности которого необходимо определить. Окончив программу фильтрации, устройство 3 вырабатывает сигналы для определения спектра, под воздействием которых процессор выполняет микропрограмму прямого БПФ. Затем устройство 3 вырабатывает микропрограмму определения амплитудных составляющих комплекс-. нОго спектра по следующей формуле Bf-tReA, где R Af 1 А {- реальная и мнимаз составляющие комплексного спектра; B-i - квадрат амппиту дь1 спектра. После этого устройство формирует микропрограмму накЬппения, и результа вычислений через устройство 8 извлечен корня и блок 1О усреднения поступают блок памяти 11, в каждой ячейке которо го фиксируется результат вычислений по алгоритму где;.111 - число накоплений; Кф- квадрат амплитуды определенных частот спектра мощности. По окончании указанных вычислений оказывается, что блок 14 заполнен выборками входного сигнала, поэтому устройство 3 вырабатывает сигнал конец занесения в блок 14 и все последующие выборки заносятся в блок 13. По получении заданного числа накоплений устройство 3 вырабатывает сигнал конец накопления и формирует микропрограмму усреднения по алгоритму . -1 « .ТДб,уу, число накоплений; ) - суммарное значение , ам1-1плитуд результатов накоп Закончив усреднение, устройство 3 подает команду йа вывод информации. В режиме фильтрации сигналов процес сор выполняет следующие операции в дополнение к вышеуказанным. По окончании обратного БПФ устройство 3 вырабатывает микропрограмму, по которой в устройстве 5 производятся следующие вычисления: .,.c,.:,; где , - действительная, и мнимая составляющие выходного сигнала; -квадрат амплитуды выходного сиг нала; -аргумент для выч сления фазы выход ного сигнала. Результаты вычислений подаются в устройства 8 и 9, где соответственно вычисляются амплитуда и фаза выходного сигнала. После операций накопления и усреднения подается команда на вывод отфильтрованной информации. В режиме вычисления корреляционных функций исследуемые /сигналы подаются: на соответствующие входы устройства 1 ввода, которое после квантования и умножения на взвешива1осцую функцию объё-; диняет два входных сигнала в один комплексный по алгоритму, иСЮ -хСкН -Ч(, K 0,1,...,N-|, где L (к) - объединенный .комплексный сигнал, )- исследуемые сигналы. Объединенный комплексный сигнал заносится в блок 13 и после накопления N выборок начинает заполняться блок 14. После обработки указанных выборок i по алгоритму прямого БПФ производится полное упорядочивание массива данных. По окончании вычислений устройство 3 ормирует микропрограмму разделение процессов и процессор работает по алгоитмуCxU Rel eC2Cj)KeC. , - С,,),2. ); ro,i,..., где C.l.j)|C. (j) - разделенные выборки входных сигналов пос ле прямого БПФ; - Iо бъединенные ььгборки сигналов после прямого БПФ с адресами j и N-J. В процессе разделения сигналов выборки Cv, СО , заносимые в .ЗУ 7, упорядочиваются по алгор)игму c,,( - где. С - преобразование выбор-( (j) - порядок замены адресов. После разделения сигналов устройство формирует управляющие сигналы, по оторым определяется взаимный спектр игналов по алгоритму,

7

1тЧФ-.п,.,фj--oH.-,-|-1;

.

( С

гдеw,y

- взаимный спектр, --спектры процессов

Сх и С

У

ка) иУ(-е);

-J - адрес коэффициентов.

Выборки спектра С х V ДополН5Потся, ;. до N значенийй обрабйгываются по алгоритму обратного БПФ.

В результате вычисления обратного БГТФ накапливаются выборки корреляцириной функдаи в комплексной форме.

Вычисление амплитуды и фазы корреляционной функций производится так же, как и при фильтрации, однако при этом выполняются микропрограммы накопления и усреднения.

Большие функциональные возможности простота управления и отнрсиТёпШо fte большие аппаратурные затраты являюп я основой для получения экономического эффекта при применении данного,процессора. ,

Ф о

рмула изобр

е тения

Специализированный процессор, содержащий устройство ввода, управпяюгций вход которого соединен с первым выходо устройства управления, информационные входы являются входами процессора, а выход соединен с информационным входом операти;вного запоминающего устройства, причем втррой и третий выходы устройст ва управле|1ия соединеиь соответственно с угцэавляющимй вхоДЙШ -ЬпёративнЗго запоминающего устройства и устройства адресами, первый и втЬ1эой вь1:сбШ.Т -kofc703821

торого соединены соответственно с адресными входами рперативного запЬминающе- го устройртва и постоянного запоминаю- г

щего устройстаа, а также вычислительное устройствр быстрого преобразования Фурье, вход-выход которого соединен с входомвыходом опера тивногр запоминающего устройства, и первый вход- с выходом постоянного запоминающего устройства, и устройство вывода, первый, выход которого является выходом процессора, а второй выход соединен с входом устройства управления, о т л ич а ю щ и и с я тем, что, с/целью повышения быстродействия и бокращения оборудования,он дополнительно содержит запоминающее устройство характеристик, устройство извлечения корня, устррйство вычисления фазы, блок усреднения и блок памяти, причем адресный и управляющий входы и выход запоминающего устройства характеристик соединены соответственно с выходами устройства адресации и устройства управления и вторым входом вычис-, лительного устройства быстрого преобразования Фурье, первый выход которого через устройство вычисления фазы -соединен с первьтм входом устройства вывода, а второй выход через устройство извлечения корня соединен с первым входом блока усреднения, выход которого сое- . - динен с входом блока памяти, выходом подк:люченного к вторым входам устрой, ства вывода и блока усреднения. Источники инфЪрМации, принятые во внимание при экспертизе

1. Патент Великобритании № 1330741, кл. О 4А, 1Э73,

.2, Патент США № 3783258, кл.235-152, 1974. ,.

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемый процессор спектральной обработки сигналов | 1982 |

|

SU1092517A1 |

| Устройство для формирования адресов процессора быстрого преобразования фурье | 1987 |

|

SU1499373A1 |

| Устройство для формирования адресов процессора быстрого преобразования Фурье | 1989 |

|

SU1691853A1 |

| Устройство для формирования широкополосного случайного процесса | 1986 |

|

SU1432514A1 |

| Коррелятор вибросейсмических данных | 1989 |

|

SU1665326A1 |

| Устройство управления для процессора быстрого преобразования Фурье | 1983 |

|

SU1111173A1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| Программируемый процессор спектральной обработки сигналов | 1978 |

|

SU744603A1 |

| Устройство для формирования адресов операндов процессора быстрого преобразования Фурье | 1983 |

|

SU1133597A1 |

| Микропрограммный процессор | 1987 |

|

SU1517034A1 |

Авторы

Даты

1979-12-15—Публикация

1976-06-28—Подача