(54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для умножения десятичных чисел | 1984 |

|

SU1182514A1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| Устройство для вычисления матрицы направляющих косинусов | 1983 |

|

SU1233142A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| Устройство для умножения | 1977 |

|

SU695364A1 |

| Устройство для умножения данных переменной длины | 1985 |

|

SU1291972A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

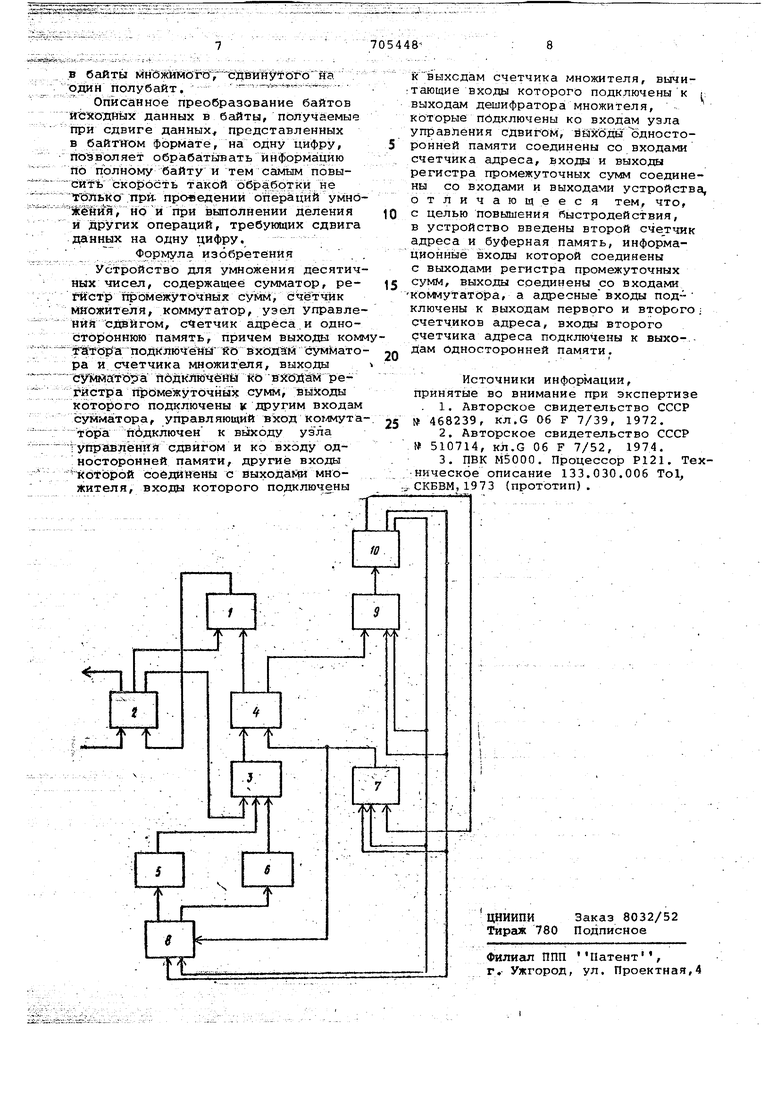

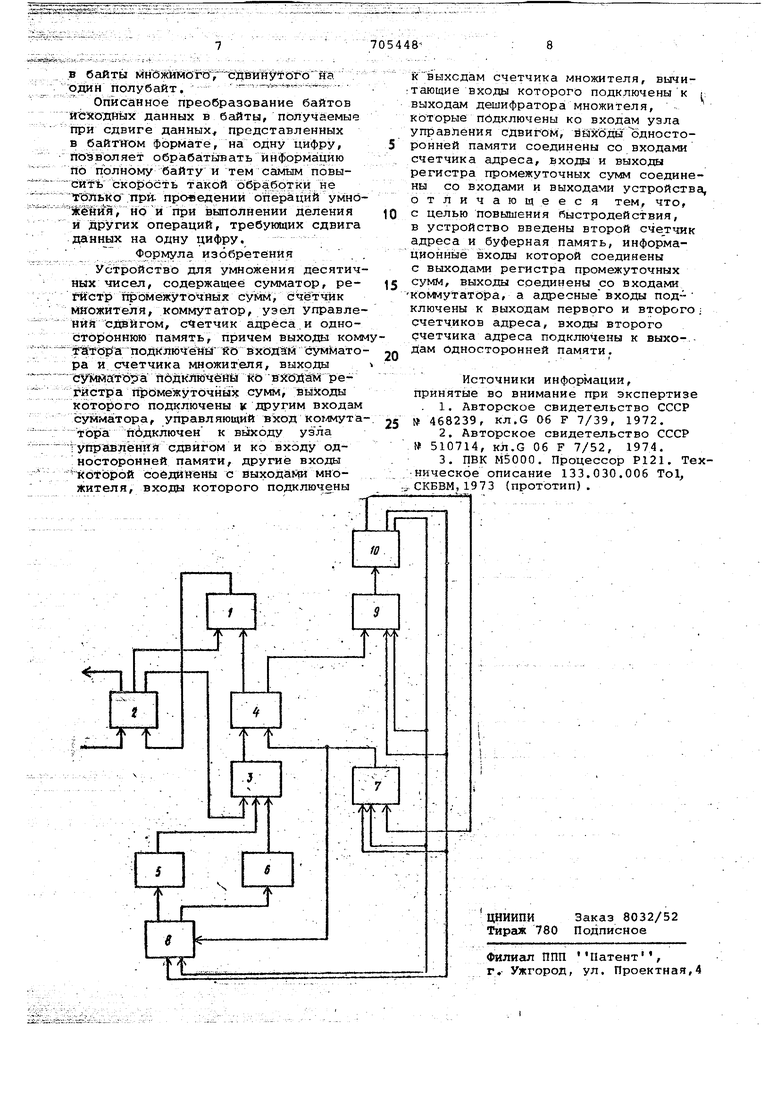

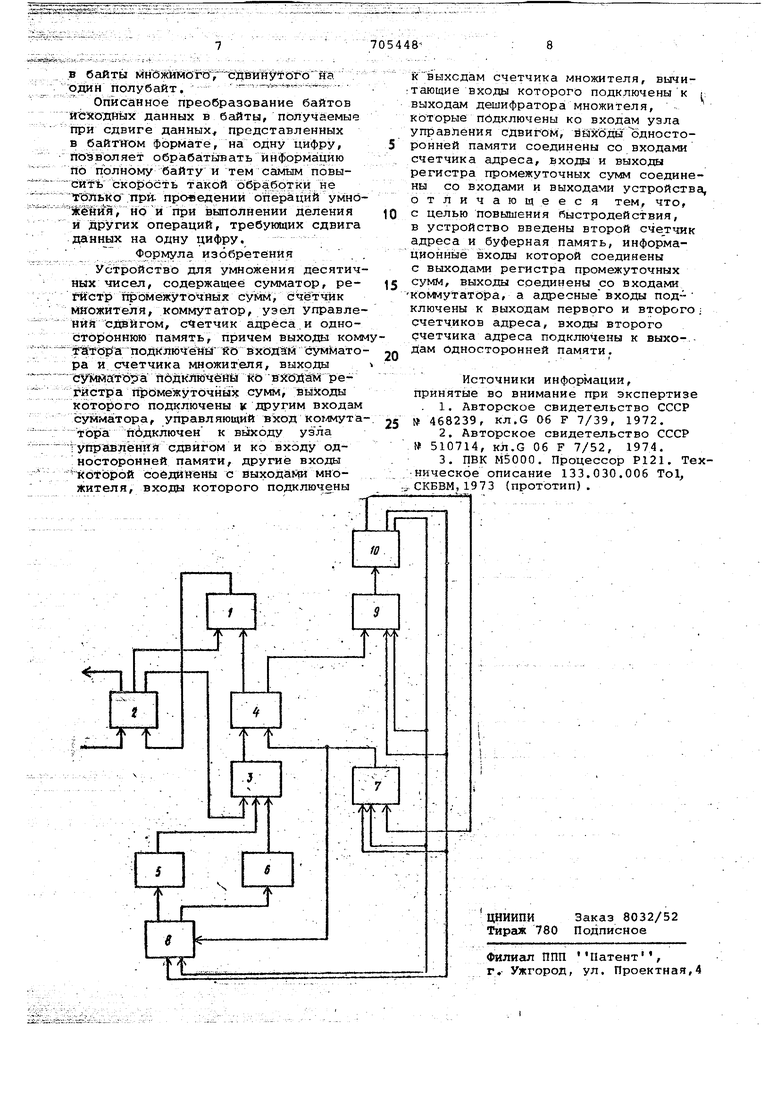

Изобретение относится к области ЦИФРОВОЙ вычислительной техники и может быть использовано в устройствах для умножения и деления десят ных чисел, представленных в байтном формате. Известны устройства для умножени в которых цифры умножаемых чисел обрабатываются параллельно 1 и {2 Данные устройства обладают больши быстродействием за счет расширения аппаратуры. При обработке данны) переменной длины аппаратура должна соответствовать максимальной длине данных и, следовательно, при обработке данных длина которых не является максимальной, часть аппаратуры не используется. В этом заключается недостаток этих устройств. Наиболее близким техническою решением к данному является устройство для умножения арифметического устрой ства процессора вычиcлитeльиOJrp комплекса М5000/4/, в котором ОДНИМ байтом кодируются две цифры 3 Однако параллельная обработка в нем двух цифр в операциях, требующих сдвига обрабатываемых данных на одну цифру (в частности,в операции умножения) , невозможна по той ;причине, что после сдвига на одну цифру один полубайт выходит из состава байта и в диспозиции обрабатывающего устройства остается только один полубайт (одна цифра), над которым может проводиться операция. Это обстоятельство значительно снижает скорость выполнения операций умножения и деления десятичных чисел при обработке их последовательно побайтно. Целью предлагаемого изобретения является увеличение &астродействия устройства для умножения путем обеспечения параллельной обработки обоих полубайтов. .Это достигаёт ся тём,что в устройстве для умножения, содержащем сумматор, регистр промежуточных сумм, счетчик множителя,дешифратор множителя, коммутатор, узел управления сдвигом, счетчик адреса и одностороннюю память, причем выходы коммутатора подключены ко входам сумматора и счетчика множителя, выходы сулфлатора подключены ко входам регистра промежуточных сумм, выходы которого подключены к другим входам сумматора, управляющий вход коммутатора подключен к выходу узла управления сдвигом и ко входу односторонней памяти,.другие входы которой соединены с выходами дешифр тора множителя, входы которого подклгочены к выходам счетчика множител вычитающие входы которого подключен jK выходам дешифратора множителя, которые подключены, ко входам узла управления сдвигом, выходы односторо ней памяти соединены со входами счетчика адреса, входы и выходы регистра промежуточных сумм Соедине со входами и выходами устройства, введены второй счетчик адреса и буферная память, информационные входы которой соединены с выходами регист ра промежуточных сумм, выходы соединены со входами коммутатора, а ад ные входы подключены к вйхойай го и второго счетчиков адреса, подключены к выходам.односторонней памяти. На чертеже представлена блоксхема устройства для умножения. Устройство содержит сумматор 1 предназначенный для обработки инфор мации по одному байту, т.е. по 2 десятичные цифры, регистр 2 промеж точных сумм, предназначенный для связи с оперативной памятью в ка честве промежуточного регистра и дл Н.капливания промежуточных сумм, в операции умножения, буфернуюпамять 3 для хранения исходных данных операций, в которой байты данны хранятся в виде полубайтов в двух самостоятельно адресуемых ее частях коммутатор 4, своими входами подклю ченный к выходам сумматора 1, счетчики 5 и б для хранения адреса полубайтов буферной памяти 3, узел 7. управления сдвигом, своим- выходом подключенный к управляющему входу коммутатора 4, одностороннюю память 8 для формирования начальных адресов полубайтов, выходы которой подк чены к счетчикам адреса 5 и б для хранения очередного байта множителя причем входы счетчика 9 мнбжиТёля подключень к выходам коммутатора 4 дешифратор 10 множителя, -причем входы дешифратора множителя 10 подключены к выходам счетчика 9 множи теля, а вйходы соединена со входами односторонней памяти. 8, к которо подключен также выход узла 7 управ ления сдвигом , выходы дешифратора множителя 10 подключены также ко вх6дам узла 7 управлениясдвигом и к вычитающим входам счетчика множителя 9, выходы счетчиков адреса 5 и б подключены к -адреснЕлм входам буферной памяти 3, к информационным входам которой подключен выходы регистра 2, входы сумматора 1 подключены к выходам регистра 2 и коммутатора 4. Устройство работает следующим Образом. . В начале операции умножения множитель и множение поступают из оперативной .памяти (на чертеже не показано) на входы устройства для умно жения, а с них - на регистр 2 промежуточных сумм,откуда переписываются в буферную память 3. Каждый байт множителя и множимого имеет свой адрес, по соторому он хранится в памяти 3 и выбирается из нее по полубайтам; один полубайт по адресу в счетчике 5,а другой - по адресу в счетчике б. Начальный адрес полубайта данных на счетчики 5 и б. поступает с выхода односторонней памяти 8. Для ускорения операции: умножения в буферную память 3 заносится также двойное множимое. Умножение чисел производится, последовательно по одному байту, множимое выбирается из буферной па.мяти 3, промежуточные суммы произведения хранятся на регистре 2, а очередной байт множителя записывается в счет-чик 9 множителя. Если умножение ведется с младших разрядов, то дешифратор 10 множителя проводится анализ младшей цифры байта множителя . Если цифра множителя больше единицы, формируется со.:ответствующий сигнал, по которому односторонняя память 8 записывает в счетчики 5 и б начальный адрес ДВОЙНС.ГО множимого; если цифра мног жителя равна единице, то с дешифратора 10 поступит сигнал, по-, которому в счетчики 5 и 6 будет начальный адрес однократного множимого. В соответствии с этими адресами из буферной памяти 3 выбираются полубайты младшего байта двойного (или однократного, в зависимости от величины цифры множителя) множимого и через коммутатор 4, который в данный момент не изменяет входной информации, подается на вход сумматора 1, Первая промежуточная сумма произведения получается при сложении множимого с нулем, т.е. содержимое выхода буферной памяти 3 просто пересыла- ется в регистр данных 2. Содержимое счетчиков адреса 5 и б уменьшается на единицу после выбора очередного байта из буферной памяти, что обуславливает выборку следующего более старшего байта множимого вследующем такте. Таки образом, все множимое пересылаете на регистр 2. При пересылке последнего байта множимого в регистр 2 счетчики адреса 5.. и б Приходят в исходное состояние, причем дешифратор 10 множителя вырабатывает сигнал, уменьшающий содержимое счетчика 9 множителя на 1 или на 2, в зависимости от выборки байтов однократного.или двухкратного множимого. и в зависимости от значения изменен ной цифры ввдает сигнал, сргласно которому одностб1ронняя Память 8 зап сывает в счетчики 5 и б начальный |адрес однократного или двойного мно жимого. При этом однократное или двухкратное множимое выбирается поб тно из буферной памяти 3, начиная от младших байтов, и складвшаётся с промежуточной суммой, побайтно поступающей из регистра 2 в сумматор 1, Результат, т.е. новая промежуточная сумма, полученная в еумматоре 1, возвращается побайтно в регист 2 на место байтов, подверпАсхся обработке. Умножение на младшую цифру множителя.продолжается до тех пор, пока она не становится, равной нулю. При этом дешифратор 10 переходит на анализ старшей цифры множителя и по ее значению выдает сигнал, определяю1ций для односторонней памяти 8 запись начального адреса одноБайты данных в буферной памяти 3 по совпадаюшм адресам g счетчике

Данные на выходе буферной памяти 3 при опережении ад15есом в счетчике 5 На единицу адреса в счетчике б

Данные на выходе коммутатора 4 ,.,..,,. о Ьо а Ь а« Ь} ... а о

Байту придается форма Ъ а где Ъ старший полубайт, а а - младший полубайт. После сдвига множимого его байты принимают форму di.bi.

Суммирование таким образом сформованных байтов с байтами промежуточной cyMNtJ осуществляется так, как 4 при умножении на младшую цифру множителя. Когда старсйая цифр множителя становится равной нулю, сигнал на выходе узла 7 управления сдвигом исчезает. При этом коммутатор 4 возвращается на режим, в котором выход буферной памяти 3 пере.г дается без взаимозамены полубайтов, а односторонняя память 8 после поступления на счетчик.9 множителя.

4v ч

Ьо ЦОо bgO

следующего байта множителя записнвает одинаковый начальный адрес полубайтов в оба счетчика 5 и 6.

При умножении на следующий байт множителя промежуточная сумма в регистре 2 сдвигается на 1 байт

вправо. Само умножение происходит аналогично, т.е. при уменьшении на младшую цифру байта множителя байты множимогр выбираются полубайтно из буферной памяти 3 в соответствии

С совпадакадим содержанием счетчиков адреса 5 и 6 и суммируются с байтами промежуточной суммы, а при умножении на старшую цифру байта множителя байты множимого перед суммированием с байтами промежуточной.суммы преобразуются вышеописанным образом кратного или двойного множимого в счетчики. 5 и 6. Этот сигнал поступает также на вход узла 7 управления сдвигом. На другой вход этого узла поступает сигнал с деишЛратора 10 множителя, индицируюший превращение в нуль младшего полубайта множителя. Под воздействием выходного сигнала узла 7 управления сдвигом односторонняя память 8 меняет начальный адрес старшего полубайта так, чтобы он опережал на единицу начальный алрес мпадаего полубайта. Коммутатор 4 под воздействием управляющего сигнала осуществляет взаимозамену полубайтов, выбранных по соседним адресг1М., в результате чего получается байт, предртавляющий лолный байт множимого, сдвинутого на одну цифру. Формирование байтов данных, сдвинутых на одну цифру, иллюстрируется следующей таблицей.

Авторы

Даты

1979-12-25—Публикация

1978-01-04—Подача