ставленной цели в него введены допол- нительно счетчик 6, элемент ИЛИ-НЕ 7, регистр константы 8, блок памяти 10, элемент И 9, п/2 групп элементов И. Сущность изобретения состоит в том, что длина перемножаемых данных может быть различной и ограничивается длиной регистра множимого. Цикл умноже1

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах ЭВМ средней производительности.

Целью изобретения является повышение быстродействия.

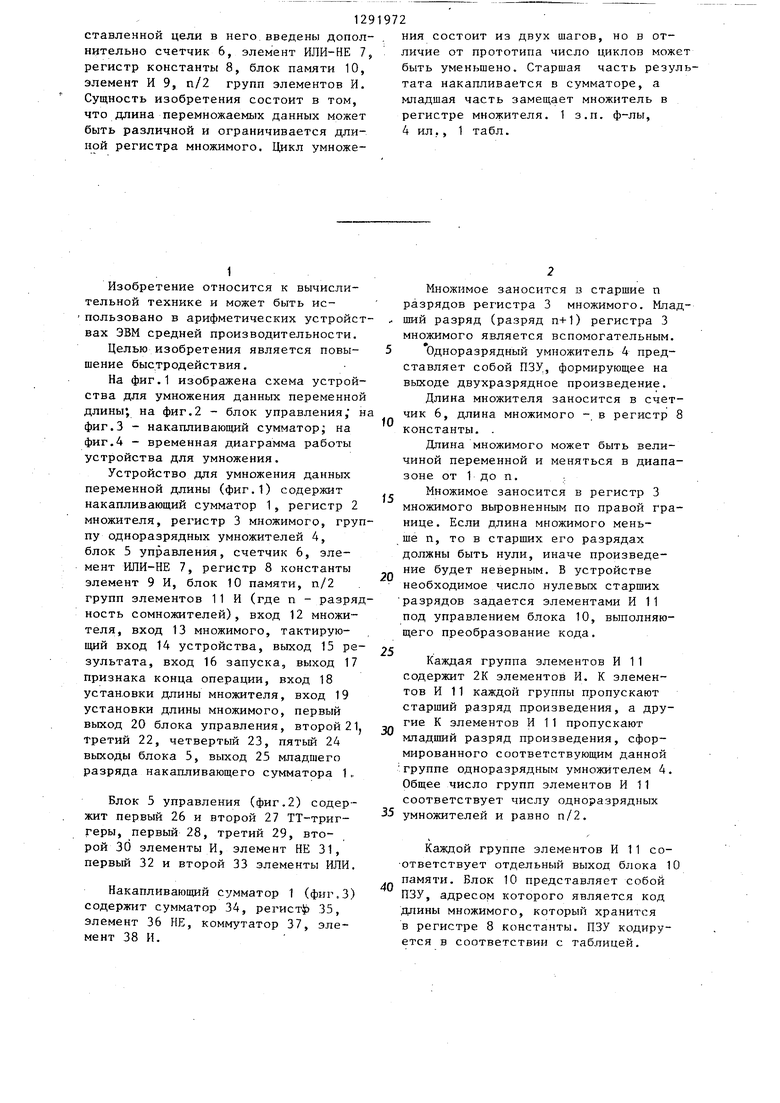

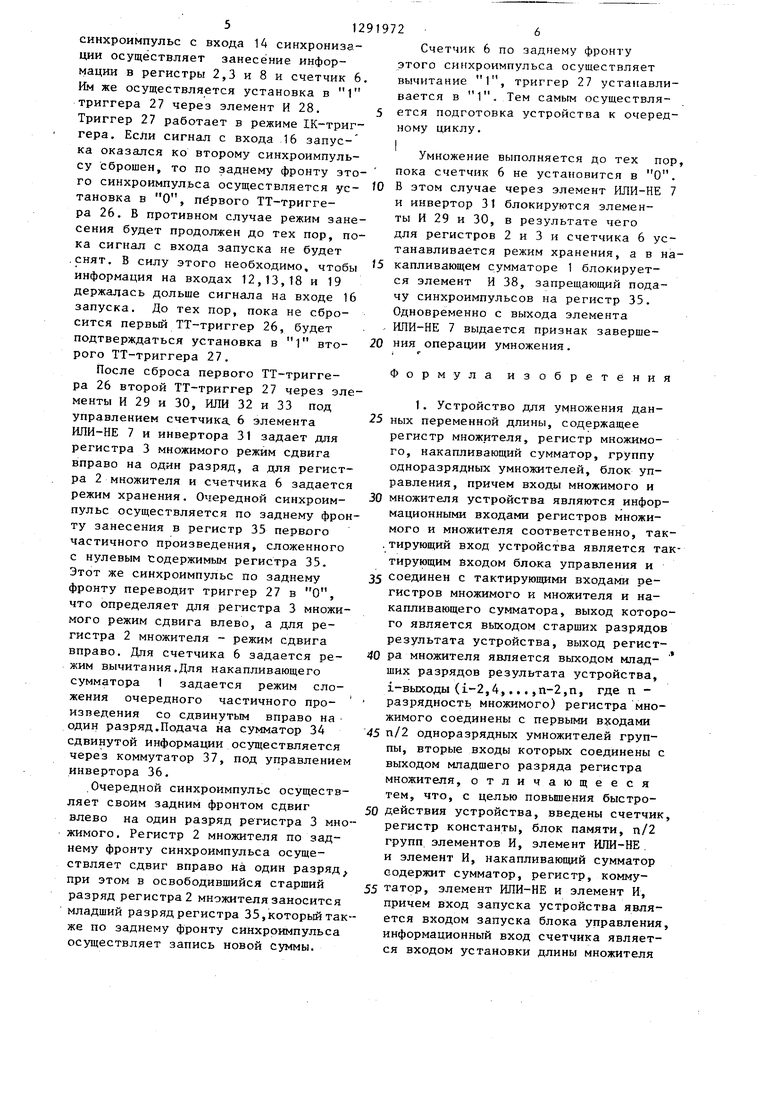

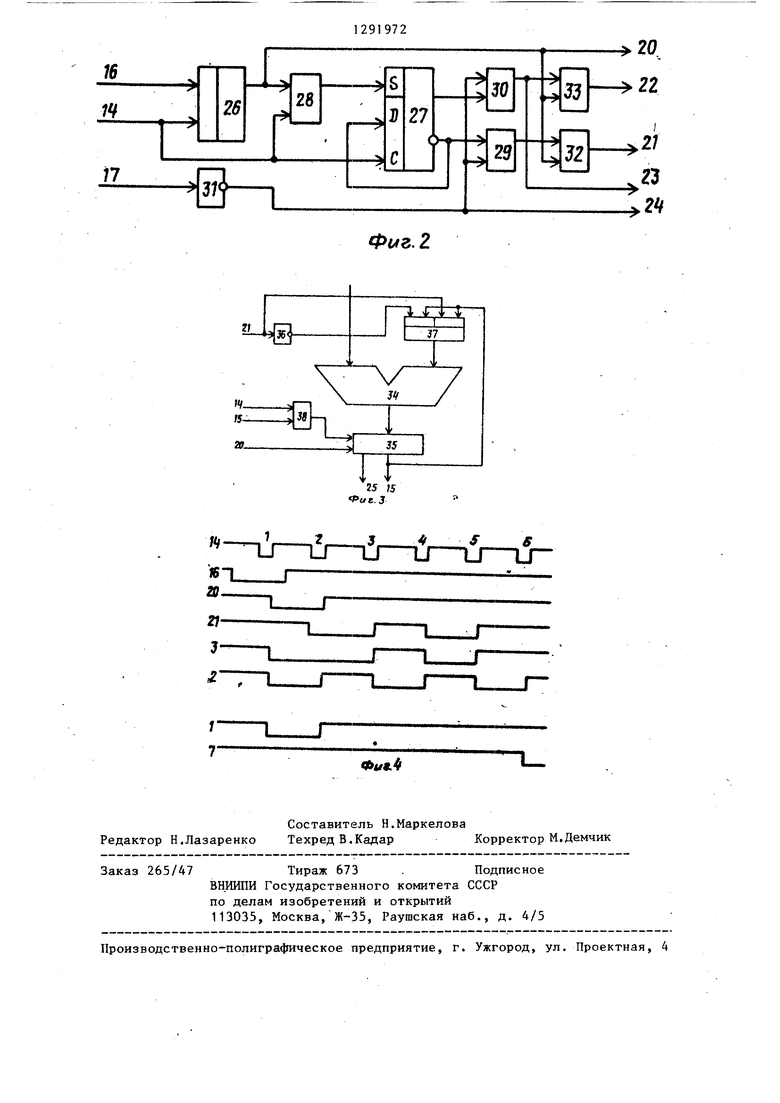

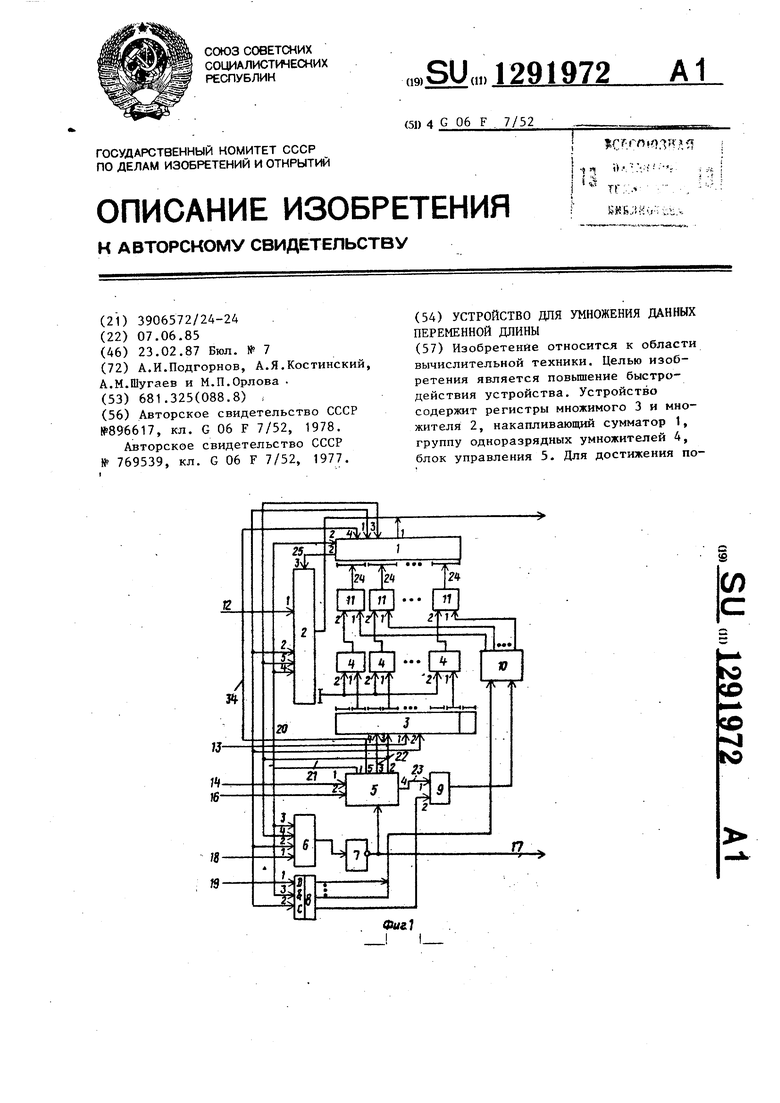

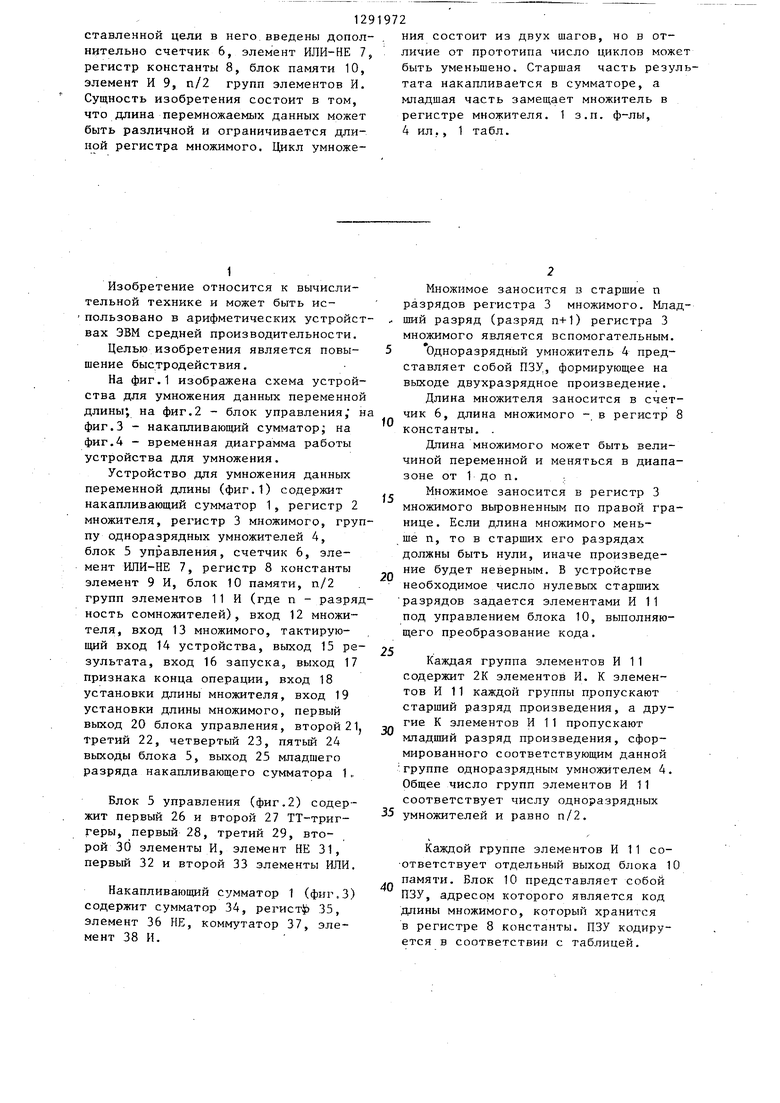

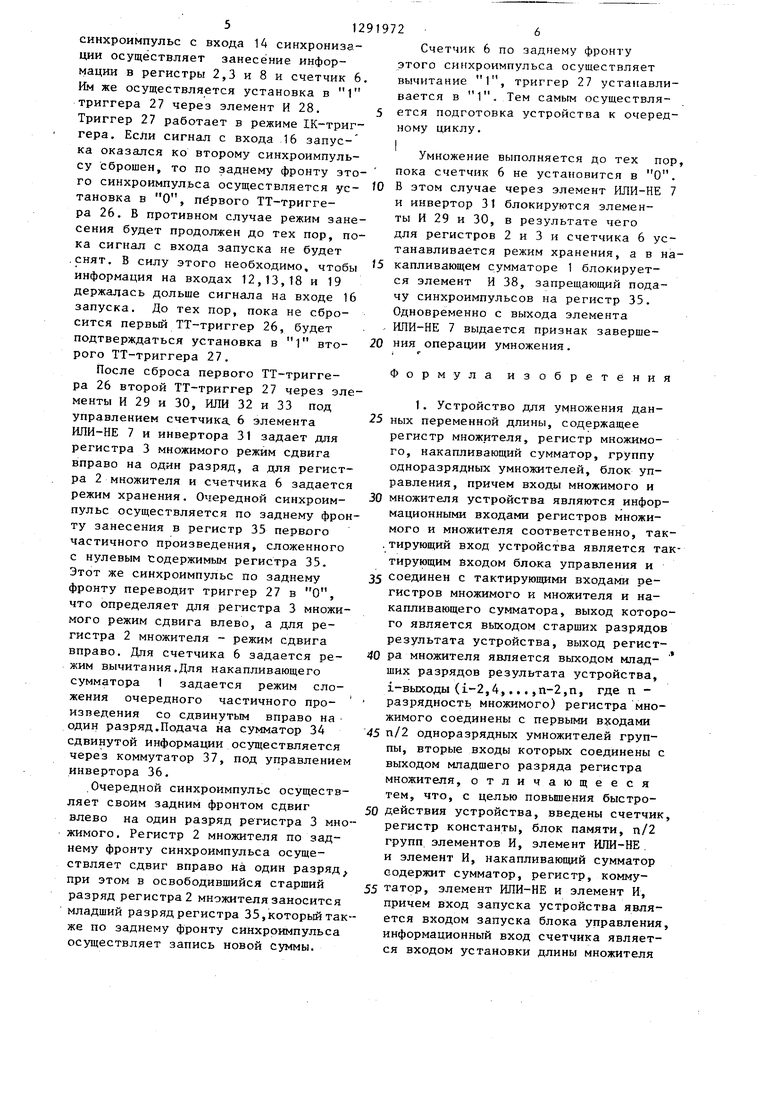

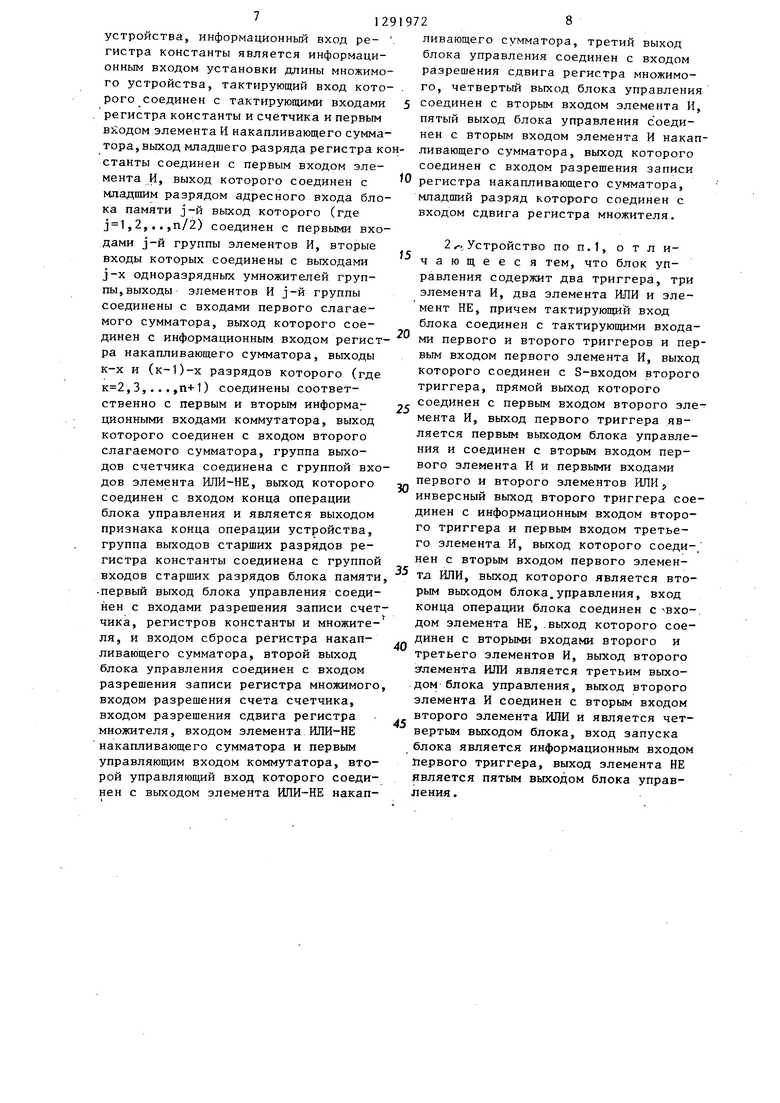

На фиг.1 изображена схема устройства для умножения данных переменной длины; на фиг.2 - блок управления; н фиг.З - накапливающий сумматорj на фиг.4 - временная диаграмма работы устройства для умножения.

Устройство для умножения данных переменной длины (фиг.1) содержит накапливающий сумматор 1, регистр 2 множителя, регистр 3 множимого, группу одноразрядных умножителей 4, блок 5 управления, счетчик 6, элемент ИПИ-НЕ 7, регистр 8 константы элемент 9 И, блок 10 памяти, п/2 групп элементов 11 И (где п - разрядность сомножителей), вход 12 множителя, вход 13 множимого, тактирующий вход 14 устройства, выход 15 результата, вход 16 запуска, выход 17 признака конца операции, вход 18 установки длины множителя, вход 19 установки длины множимого, первый выход 20 блока управления, второй 21, третий 22, четвертый 23, пятый 24 выходы блока 5, выход 25 младшего разряда накапливающего сумматора 1„

Блок 5 управления (фиг.2) содержит первый 26 и второй 27 ТТ-триг- геры, первый 28, третий 29, второй 30 элементы И, элемент НЕ 31, первый 32 и второй 33 элементы ИЛИ.

Накапливающий сумматор 1 (фиг.З) содержит сумматор 34, регистр 35, элемент 36 НЕ, коммутатор 37, элемент 38 И.

ния состоит из двух шагов, но в отличие от прототипа число циклов может быть уменьшено. Старшая часть результата накапливается в сумматоре, а младшая часть замещает множитель в регистре множителя. 1 з.п. ф-лы, 4 ил., 1 табл.

Множимое заносится в старшие п разрядов регистра 3 множимого. Мпад- ший разряд (разряд п+1) регистра 3 множимого является вспомогательным. Одноразрядный умножитель 4 представляет собой ПЗУ, формирующее на выходе двухразрядное произведение.

Длина множителя заносится в счетчик 6, длина множимого - в регистр 8 константы. .

Длина множимого может быть величиной переменной и меняться в диапазоне от 1 до п.

Множимое заносится в регистр 3 множимого выровненным по правой границе . Если длина множимого меньше п, то в старших его разрядах должны быть нули, иначе произведение будет неверным. В устройстве необходимое число нулевых старших разрядов задается элементами И 11 под управлением блока 10, выполняющего преобразование кода.

Каждая группа элементов И 11

содержит 2К элементов И. К элементов И 11 каждой группы пропускают старший разряд произведения, а другие К элементов И 11 пропускают младший разряд произведения, сформированного соответствующим данной группе одноразрядным умножителем 4. Общее число групп элементов И 11 соответствует числу одноразрядных умножителей и равно п/2.

Каждой группе элементов И 11 соответствует отдельный выход блока 10

памяти. Блок 10 представляет собой

ПЗУ, адресом которого является код

длины множимого, который хранится в регистре 8 константы. ПЗУ кодируется в соответствии с таблицей.

Умножение множимого на разряд множителя осуществляется за два шага

На первом шаге на цифру множителя умножаются младшие разряды двухразрядных регистров, содержащих множимое. Результат умножения складывается на накапливающем сумматоре с промежуточным произведением. В конце этого шага осуществляется сдвиг вправо на один разряд регистра 3 множимого.

На втором шаге на ту же цифру множителя умножаются старшие разряды двухразрядных регистров, содержапщх множимое, которые в результате сдвига вправо помещаются в позиции младших разрядов. Разряд п в результате сдвига попадает в разряд п+1, которы выполняет функцию буферного регист- ра для младшего разряда множимого. Новое произведение складывается со сдвинутым вправо на разряд частичным произведением, хранящимся на накапливающем сумматоре 1.

В конце второго шага осуществляется сдвиг влево регистра 3 множимого на одну цифру. В результате сдвига

5

0

0

5

5

множимое занимает первоначальную позицию в регистре 3 множимого. Одновременно со сдвигом множимого осуществляется сдвиг регистра 2 множителя на один разряд вправо. В результате сдвига на одноразрядные умножители 4 подается очередная цифра множителя, а в освобождающуюся позицию вдвигается младший разряд произведения из накапливающего сумматора 1, Окончательное произведение хранится на на- капливакмцем сумматоре 1 (старшая часть произведения) и на регистре 2 множителя (младшая часть произведения) .

Устройство для умножения работает следующим образом.

По си1 налу, поступающему на вход 16 запуска, и по заднему фронту синхроимпульса с входа 14 синхронизации устанавливается в 1 первый ТТ-триггер 26, который совместно с элементами ИЛИ 32 и 33 устанавливает режим занесения в регистр 2 множителя, регистр 3 множимого, счетчик 6, регистр 8 константы, а также устанав- .ливает в О регистр 35. Следующий

512

синхроимпульс с входа 14 синхронизации осуществляет занесение информации в регистры 2,3 и 8 и счетчик 6 Им же осуществляется установка в 1 триггера 27 через элемент И 28. Триггер 27 работает в режиме 1К-триг- гера. Если сигнал с входа 16 запус- ка оказался ко второму синхроимпульсу сброшен, то по заднему фронту этого синхроимпульса осуществляется установка в О, первого ТТ-тригге- ра 26. В противном случае режим занесения будет продолжен до тех пор, пока сигнал с входа запуска не будет .снят. В силу этого необходимо, чтобы информация на входах 12,13,18 и 19 держалась дольше сигнала на входе 16 запуска. До тех пор, пока не сбросится первый ТТ-триггер 26, будет подтверждаться установка в 1 второго ТТ-триггера 27.

После сброса первого ТТ-триггера 26 второй ТТ-триггер 27 через элементы И 29 и 30, ИЛИ 32 и 33 под управлением счетчика 6 элемента ИПИ-НЕ 7 и инвертора 31 задает для регистра 3 множимого режим сдвига вправо на один разряд, а для регистра 2 множителя и счетчика 6 задается режим хранения. Очередной синхроимпульс осуществляется по заднему фронту занесения в регистр 35 первого частичного произведения, сложенного с нулевым содержимым регистра 35. Этот же синхроимпульс по заднему фронту переводит триггер 27 в О, что определяет для регистра 3 множимого режим сдвига влево, а для регистра 2 множителя - режим сдвига вправо. Для счетчика 6 задается режим вычитания,Для накапливающего сумматора 1 задается режим сложения очередного частичного произведения со сдвинутым вправо на один разряд,Подача на сумматор 34 сдвинутой информации осуществляется через коммутатор 37, под управлением инвертора 36,

Очередной синхроимпульс осуществляет своим задним фронтом сдвиг влево на один разряд регистра 3 множимого. Регистр 2 множителя по заднему фронту синхроимпульса осуществляет сдвиг вправо на один разряд при этом в освободившийся старший разряд регистра 2 множителя заносится младший разряд регистра 35,который также по заднему фронту синхроимпульса осуществляет запись новой суммы.

2 6

Счетчик 6 по заднему фронту этого синхроимпульса осуществляет вычитание 1, триггер 27 устанавливается в 1,. Тем осуществляется подготовка устройства к очередному циклу.

Умножение выполняется до тех пор, пока счетчик 6 не установится в О.

В этом случае через элемент ИЛИ-НЕ 7 и инвертор 31 блокируются элементы И 29 и 30, в результате чего для регистров 2 и 3 и счетчика 6 устанавливается режим хранения, а в накапливающем сумматоре блокируется элемент И 38, запрещающий подачу синхроимпульсов на регистр 35. Одновременно с выхода элемента ИЛИ-НЕ 7 выдается признак завершения операции умножения.

1

Формула изобретения

1. Устройство для умножения данных переменной длины, содержащее регистр множителя, регистр множимого, накапливающий сумматор, группу одноразрядных умножителей, блок управления, причем входы множимого и

множителя устройства являются информационными входами регистров множимого и множителя соответственно, так- тирующий вход устройства является тактирующим входом блока управления и

соединен с тактирующими входами регистров множимого и множителя и накапливающего сумматора, выход которого является выходом старших разрядов результата устройства, выход регистра множителя является выходом младших разрядов результата устройства, i-вькоды (i-2,4,,.. ,п-2,п, где п - разрядность множимого) регистра множимого соединены с первыми входами

п/2 одноразрядных умножителей группы, вторые входы которых соединены с выходом младшего разряда регистра множителя, отличающееся тем, что, с целью повышения быстродействия устройства, введены счетчик, регистр константы, блок памяти, п/2 групп, элементов И, элемент ИЛИ-НЕ. и элемент И, накапливающий сумматор содержит сумматор, регистр, коммутатор, элемент ИЛИ-НЕ и элемент И, причем вход запуска устройства является входом запуска блока управления, информационный вход счетчика является входом установки длины множителя

12919728

устройства, информационный вход ре- .ливающего сумматора, третий выход гистра константы является информаци-блока управления соединен с входом онным входом установки длины множимо-разрешения сдвига регистра множимого устройства, тактирующий вход кото-. го, четвертый выход блока управления рого соединен с тактирующими входами5 соединен с вторым входом элемента И, регистра константы и счетчика и первымпятый выход блока управления с оеди- в Содом элемента И накапливающего сумма-нен с вторым входом элемента И накап- тора,выход младшего разряда регистра кон-ливающего сумматора, выход которого станты соединен с первым входом эле-соединен с входом разрешения записи мента И, выход которого соединен с регистра накапливающего сумматора, младшим разрядом адресного входа бло-младший разряд которого соединен с ка памяти j-й выход которого (гдевходом сдвига регистра множителя. ,2,..,п/2) соединен с первыми входами j-й группы элементов И, вторые2, Устройство по п.1, о т л и- входы которых соединены с выходамичающееся тем, что блок уп- J-X одноразрядных умножителей груп-равления содержит два триггера, три пы,выходы элементов И j-й группыэлемента И, два элемента ИЛИ и эле- соединены с входами первого слагае-мент НЕ, причем тактирующий вход мого сумматора, выход которого сое-блока соединен с тактирующими входа- динен с информационным входом регист-ми первого и второго триггеров и пер- ра накапливающего сумматора, выходывым входом первого элемента И, выход к-х и (к-1)-х разрядов которого (гдекоторого соединен с S-входом второго ,3,...,п+1) соединены соответ-триггера, прямой выход которого ственно с первым и вторым информа-25 ° первым входом второго эле- ционными входами коммутатора, выходмента И, выход первого триггера яв- которого соединен с входом второголяется первым выходом блока управле- слагаемого сумматора, группа выхо-« « соединен с вторым входом пер- дов счетчика соединена с группой вхо- ого элемента И и первыми входами дов элемента ИЛИ-НЕ, выход которогоу. первого и второго элементов ИЛИ соединен с входом конца операцииинверсный выход второго триггера сое- блока управления и является выходомДинен с информационным входом второ- признака конца операции устройства, триггера и первым входом третье- группа выходов старших разрядов элемента И, выход которого соеди-. гистра константы соединена с группой ен с вторым входом первого элемен- входов старших разрядов блока памяти,та ИЛИ, выход которого является вто- .первый выход блока управления соеди-Рым выходом блока.управления, вход йен с входами разрешения записи счет-конца операции блока соединен . чика, регистров константы и множите- дом элемента НЕ,.выход которого сое- ля, и входом сброса регистра накап-динен с вторыми входами второго и ливающего сумматора, второй выходтретьего элементов И, выход второго блока управления соединен с входомзглемента ИЛИ является третьим выхо- разрешения записи регистра множимого,дом блока управления, выход второго входом разрешения счета счетчика,элемента И соединен с вторым входом входом разрешения сдвига регистра.. второго элемента ИЛИ и является чет- множителя, входом элемента ИЛИ-НЕвертым выходом блока, вход запуска накапливающего сумматора и первымблока является информационным входом управляющим входом коммутатора, вто-первого триггера, выход элемента НЕ рой управляющий вход которого соеди-является пятым выходом блока управ- иен с выходом элемента ИПИ-НЕ накап-пения.

Фиг,2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1985 |

|

SU1278838A1 |

| Арифметическое устройство | 1985 |

|

SU1287144A1 |

| Устройство для умножения | 1983 |

|

SU1130859A1 |

| Устройство для умножения | 1988 |

|

SU1654814A2 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249845C1 |

| Устройство для умножения | 1978 |

|

SU896617A2 |

| Устройство для умножения | 1986 |

|

SU1427361A1 |

Изобретение относитс,я к области вычислительной техники. Целью изобретения является повьшение быстродействия устройства. Устройство содержит регистры множимого 3 и множителя 2, накапливающий сумматор 1, группу одноразрядных умножителей 4, блок управления 5. Для достижения поi (Л

т

Составитель Н.Маркелова Редактор Н.Лазаренко Техред В,Кадар Л Л Г- .- J.U- J 11-T1M J...M.- -.---

Заказ 265/47Тираж 673 . Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

ФУ9.

| Устройство для умножения | 1978 |

|

SU896617A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1977 |

|

SU769539A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-23—Публикация

1985-06-07—Подача