(54) ЦИФРОВОЙ РЕГИСТРАТОР ОДНОКРАТНЫХ ДЛИТЕЛЬНЫХ ИМПУЛЬСНЬ Х СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой регистратор | 1984 |

|

SU1164549A1 |

| Цифровой регистратор однократныхиМпульСОВ | 1979 |

|

SU851765A1 |

| Цифровой регистратор | 1980 |

|

SU920379A1 |

| Устройство формирования напряжения развертки для масштабно-временного преобразователя | 1990 |

|

SU1775673A1 |

| Устройство сбора данных для цифрового анализатора сигналов | 1990 |

|

SU1751683A1 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

| Устройство для регистрации информации | 1982 |

|

SU1167635A1 |

| Устройство для индикации однократных сигналов | 1984 |

|

SU1275519A1 |

| Многоканальный цифровой регистратор | 1981 |

|

SU959113A1 |

| Устройство для записи каротажных диаграмм | 1988 |

|

SU1520464A1 |

1

Изобретение относится к области измерительной техники и может быть использовано для регистрации однократных длительных импульсных сигналов с быстроизменяющейся начальной и медленНоменяющейся заданной фазой сигнала, отношение медленной фазы к быстрой может быть 10 и более.

Известен цифровой регистратор, содержаидайзапоминающее устройство, блок управления, генератор тактовых импульсов, времязадающее устройство и преобразователь аналог-код 1.

Недостатком известного устройства. является то, что при записи сигналов, имеющих быструю фазу и медленную фазу, которая по времени на несколько порядков превышает быструю, фазу, требуется значительный объём памяти для запоминания значений медленной фазы сигналов.

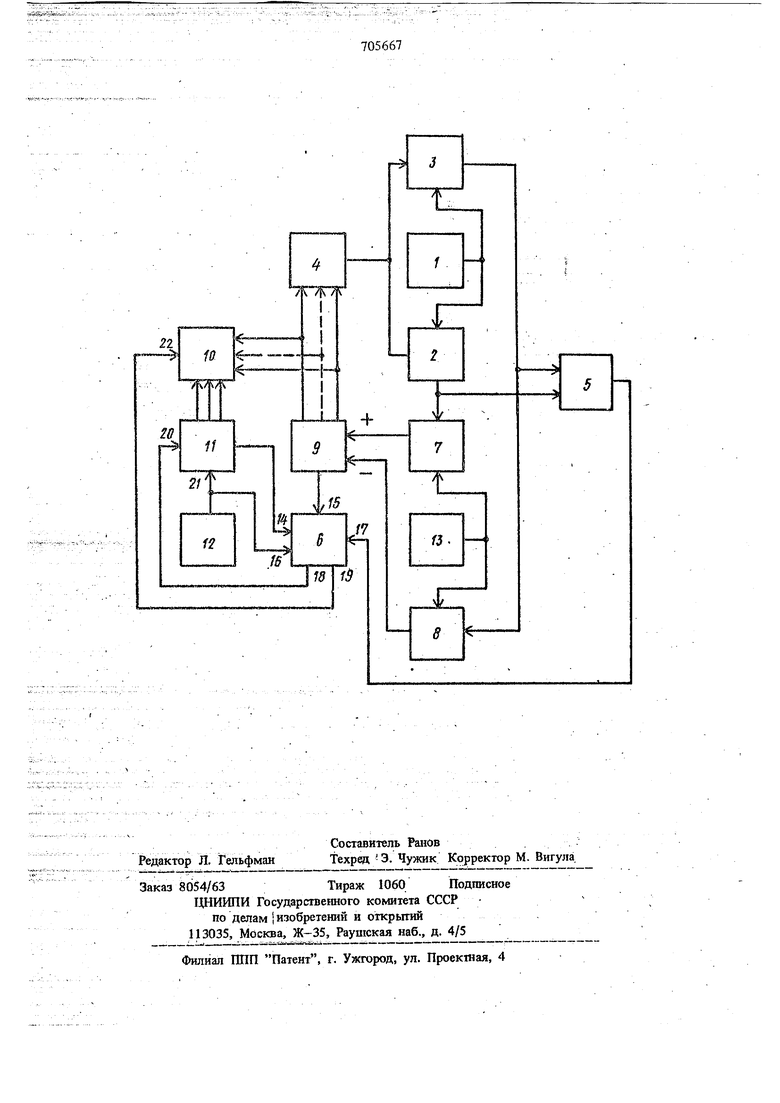

Известен также цифровой регистратор однократных длительнььх импульсных сигиалов, содержащий зaпo шнaющee устройство, блок управления, первый генератор импульсов, датшк сигналов, времязадающее устройство, имеющее тактовый вход и вход управления, и следящий преобразователь, состоящий Из реверсивного счетчика, цифроаналогового преобразователя, двух элементов срапиепня, двух элементов И и второго генератора импульсов, выход которого соединен с первым входам элементов И, вторые входы которых соедр неиь с выходами соответствующих элементов сравнения, выходы элементов И соединены с входами реверашного счетчика, первые входы элементов сравнения соединены с выходом датчика сигналов, вторые входы - с выходом цифроаналогового преобразователя, информационные входы которого соединены с выходами реверсивного счетчика и с nepnbiMif входами данных запоминающего устроства, вторые входы данных которого соединены с инфор. мационнылчи выходами времязадающего устройства, управляющий выход которого соединен с лервым входом устройства управления, второй вход которого соединен с управляюЩ11М выходом реверсивного счегшка, третий вход - с выходом первого reifepaTopa импульсов, апервый выход - с входом записи запоминающего устройства, второй выход устройства управлеьшя соединен с тактовым ихо.дом времязадающего устройства, а третий выход - соеданен с входом управления времязадающего устройства 2. Недостатком изиеспюго устройства является то, что при записи сигналов, имеющих быструю и медлештую фазы требуется большой объем запоминающего устройства. Так, например, при затшси сигнала, отношение медленной к быстрой которого составляет величину 10 и при записи медленной фазы в пяти ягчейках памяти запоминающего устройства требуется объем памяти равной 510 слов разрядность которых равна шслу разрядов реверсивного счетчика. Целью изобретения является уменьщетше объема Памяти запоминающего устройства. Поставленная цель достигается тем, что в цифровом регистраторе однократных длительных импульсных сигналов, содержащем запоминающее устройство, устройство управления, первый генератор импульсов, датчик сигналов, времязадающее устройство, имеющее тактовый вход и вход- управления, и следящи преобразователь, состоящий из реверсивного счётчика, цйфроаналогового преобразователя, двух элементов сравнегшя, двух элементов И и Второго гене атора импульсов, выход котоJ3oro соединен с первыми вхоД;ами элементов И, вторые входы которых соединены с выходами соответствующих элемеггтов сравнения, вькоды элементов И соединены с входами реверсивного счетчика, первые входы элементов сравнения соединены с выходом датчика сигналов, вторые входы - с выходом цифроаналогового преобразователя, информационные входы которого соединены с выходами ревершвноТо счетчика и с первыми входами данны запоминающего устройства, вторые входы дан ных которого соединены с информациогшыми выходами времязадающего устройства, управляющий выход которого соединен с первым входом устройства управления, второй вход которого соединен с зшравляющим выходом реверсивного счетчика, третий вход - с выхо дом первого генератора импульсов, а первый выход - с входом записи запоминающего уст ройства, в следящий преобразователь введен элемент ИЛИ, дополнительный вход устройсг ва управле1шя соединен с выходом элемента ИЛИ, входы которого соединены с выходами элементов сравнения, второй выход устройства управления соединен с входом управления времязадающего устройства, тактовый вход к торого соединен с выходом перрого тактового генератора. На чертеже представлена структурная электрическая схема цифрового регистратора однократных длительных импульсных сигнало - 4 Устройство содержит дат-шк сигналов 1, элементы сравнения 2, 3, иифроаналоговый преобразователь 4, олемент ИЛИ 5, устройство управления 6, элементы И 7, 8, реверсивный счетчик 9, запоминающее устройство 10, времязадающее устройство И, генераторы импульсов 12, 13, входы устройства управления 14, 15, 16, 17, выходы устройства управления 18, 19, управляющий и Тактовый входы времязадающего устройства соответственно 20, 21, вход записи запоминающего устройства 22. Устройство работает следующим образом. Код На выходах реверсивного счетчика 9 постоянно отлеживает входное напряжение, поступающее с выхода датчика сигнала 1. В процессе регистрации сигнала можно выделить два режима работы регистратора: режим регистрации переднего фронта и быстрых фаз сигнала (режим 1) и режим регистрации остальных фаз сигнала (режим 2). Переключение режимов осуществляет блок управления б. Регистрация фронта сигнала начинается после того, как на вход 15 устройства управления 6 с управляющего вьаода реверсивного счетчика 9 поступает цифровой ситал. Этот сигнал поступает в том случае, когда реверс1шный счетчик 9 накопит заданное (экспериментатором , до начала регистрации) число имнульсов, что будет означать достижение сигналом с выхода датчика 1 заданного уровня. После поступления на вход 15 устройства управления 6 цифрового сигнала, на вход записи 22 запоминающего устройства 10 начинают поступать с вы- , хода 19 устройства управле1шя 6 импульсы, которые следуют через равные промежутки времени Tj, задаваемые генератором 12, и обеспечивают запись в запоминающее устройство 10 данньк с выходов реверсивного счетчргка 9 и времязадающего устройства 11. После записи в запоминающее устройство 10 Nj значений регистрируемого сигнала начинается отсчет времени i5O времязадающем устройстве 11 (дгтя этого с выхода 18 устройства управления 6 на управляющий вход 20 времязадающего устройства 11 поступает цифровой сигнал), и в устройстве управления регистратором 6 происходит подключеьше его выхода. 19 к входу 17 (это переключение переводит регистратор во 2-й режим работы). При работе регистратора в релсиме 2 запись в запоминающее устройство 10 данных с выхода реверсивного счетчика о величине сигнала происходит в моменты времени срабатьшания элементов сравнения 2 или 3) при этом в запоминающее устройство 10 также записьшаются данные с информационных выходов йремязадающего устройства 11 о знатении этого момента времени. При поступлении с -выхода датчика 1 быстрых фаз сигнала устройство управления 6 отключает свой вход 17 от своего выхода 19 и обеспечивает поступление с него на управляющий вход 22 запоминающего устроаствя 10 Nj импульсов, следующих с периодом Tj. После поступления импульсов вновь происходит переключение режимов работы регистратора (регистратор будет работать в режиме 2)v Окончание регистрации производится устройством управле1шя б либо при переполнении запоминающего устройства 10 (сигнал переполнешш вырабатывает устройство управления) либо через промежуток времени Л Т после начала регистрации сигнала (в этом случае сигнал вырабатьшает времязадающее устройство 11, и этот сигнал поступает с управляющего выхода времязадающего устройства 11 на вход 14 устройства управления 6). Предаоженное устройство позволяв значительно снизить объем запоминаемой информаци по сравнению с известными цифровыми регист раторами.. Формула изобртенй я Цифровой регистратор однократных длительных импульсных сигналов, содержащий запоминающее устройство/ устройство управления, первый генератор импульсов, датчик сигна лов, времязадающее устройство, имеющее тактовой вход и вход управления, и следящий преобразователь, состоя1ций из peBepcstisHoro счетчика, цифроаналогового преобра:зователя, двух элементов сравнения, двух элемйиов И; и второго генератора импульсов, вькоД которого соединён с первыми входами элементов И, вторые входы которых соединерш с выходами соответстауюцдах элементов- срав1гення, выходы элементов И соединены с входами реверсивного счетчика, первые вхоДЬ элементов сравнения соединены с выходом датП{ка сигналов, вторые Входы - с выходом цифроаналогового преобразователя, информациотп 1е входы которого соединены с выходами реверсивного счетчика и с первыми входами данных запоминайщёго устройства, вторые входы данных которого соединены с информационными выходами времязадающего устройства, управляющий выход которого соединен с первым входом устройства управления, второй вход которого соединен с управляющим выходом реверсивного счетчика, третий вход - с выходом первого генератора импульсов, а первьш выход - с входом записи запоминающего устройства, отличающ и и с я тем, что, с целью уменьшения объема памяти запоминающего устройства, в следяцдай преобразователь введен элемент ИЛИ, Допол1штельньш вход устройства управления соединен с выходом элемента ИЛИ, входы которогосоединены с выходами элементов сравнения, Второй вькод устройства управления соединен с входом управлетшя времязадающего устройства, тактовый вход которого соединен с выходом первого тактового генератора. . Источники информации, .принятые во внимание при экспертизе 1.Техническое описание П5 3031002 к щфовому накопителю Сигма, блок схема 53031002 СхБ. СКВ БП АН СССР, 1968. 2.Смолов В. Б. и др. Полупроводтпсовые одирующие и декодирующие преобразователи апряжения. Энергия, 1967, с. 135, рис. 2-5а.

Авторы

Даты

1979-12-25—Публикация

1977-06-01—Подача