(54) МНОГОКАНАЛБНЫЙ ЦИФРОВОЙ РЕГИСТРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой регистратор формы импульсных сигналов | 1980 |

|

SU962821A1 |

| Устройство для регистрации информации | 1982 |

|

SU1167635A1 |

| Запоминающее устройство | 1981 |

|

SU1018150A1 |

| Устройство для отображения однократных электрических сигналов | 1983 |

|

SU1141445A1 |

| Устройство для измерения среднеквадратического значения сигнала | 1990 |

|

SU1781625A1 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

| Логический анализатор | 1984 |

|

SU1259267A1 |

| Устройство для измерения среднеквадратического значения сигнала | 1989 |

|

SU1728808A1 |

| Устройство для многоканальной записи аналоговых процессов | 1985 |

|

SU1304070A1 |

| Устройство для регистрации однократных процессов | 1981 |

|

SU959147A1 |

Изобретение относится к автоматике и вычислительной технике, предназначено для цифровой регистрации быстропротекающих процессов, и может быть использовано для исследования формы однократных непериодических сигналов и измерения их параметров. Известны устройства цифровой регистрации однократных .процессов, содержащие последовательно соединенные датчик, усилитель, аналого-цифровой преобразователь, блок памяти, системы управления и индикации Г. Однако построение многоканальной системы регистрации быстропротекающих процессов по аналогичной схеме связано с дополнительной трудностью, определяющейся спецификой параллельного преобразования информационных сигналов: необходимостью сохранения временного соответствия мгновенных значений процессов меж ду каналами. Наиболее близким к предложенному является устройство для цифрового измерения и регистрации однократных процессов малой длительности, содержащее датчик, измерительный усилитель, аналого-цифровой преобразователь (АЦП) и запоминающий блок, соединенные последовательно, блок управления памятью, блок начала регистрации, выполненный на усилителе, соединенном с пороговым элементом, счетчик, соединенный с нулевым в.ходом триггера начала и конца регистрации, элемент И, один вход которого соединен с выходом триггера, а другой подсоединен к выходу генератора тактовых импульсов, а выход соединен со входом блока управления памятью 2. В таком устройстве при внешней синхронизации регистрация начинается с момента прихода запускающего импульса. Если частота дискретизации высокая, а время от момента прихода импульса синхронизации до прихода информационного сигнала значительно, то память может быть заполнена информацией предзаписи или вместит в себя только часть сигнала, на максимальную длитель-ность которого она рассчитана.. Эта возможность более вероятна в многоканально.м регистраторе, где информационные сигналы поступают от пространственно

распределенных датчиков и моменты их поступления существенно различны.

Целью изобретения является обеспечение надежной записи сигналов, время поступления которых априорно неизвестно, без потери начального участка записи первого приходящего сигнала.

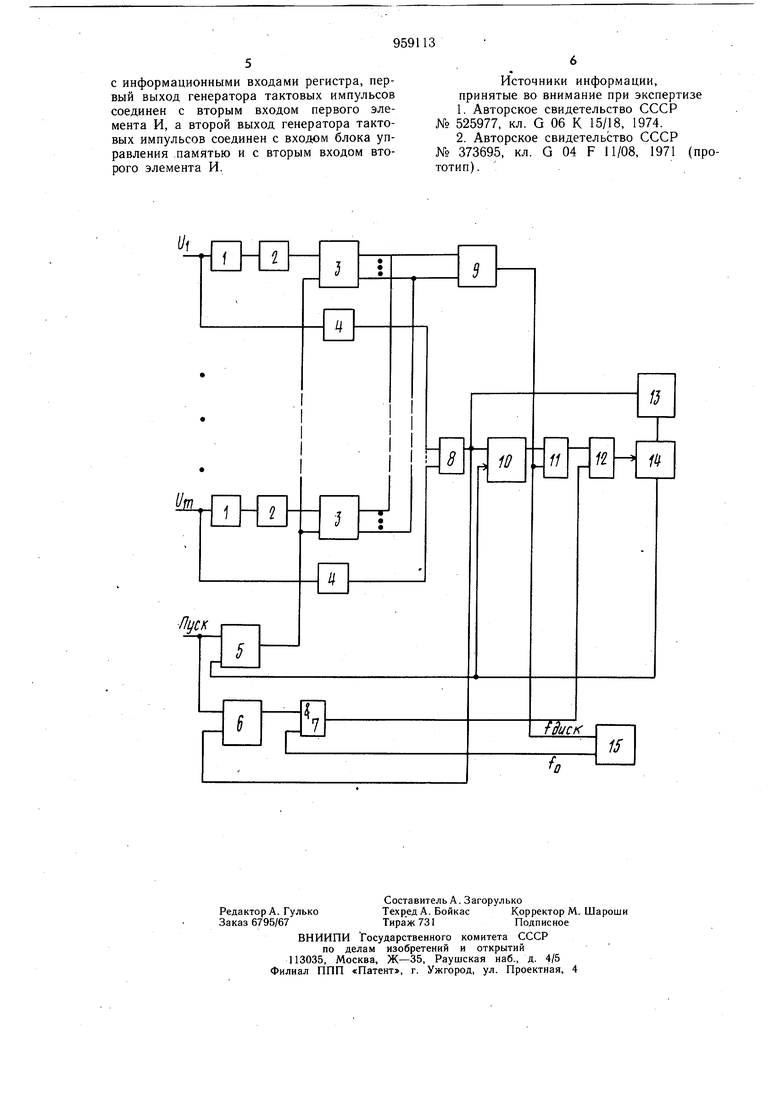

Цель достигается тем, что в многоканаль ный цифровой регистратор, содержащий первый и второй триггеры, элемент И, счетчик, блок управления памятью, генератор тактовых импульсов и в каждом канале последовательно соединенные усилитель, аналого-цифровой преобразователь, блок памяти и усилитель-формирователь, введены первый и второй элементы ИЛИ, третий триггер, второй элемент И, регистр, причем входы первого элемента ИЛИ подключены к выходам усилителей-формирователей, а выход элемента ИЛИ соединен с входом разрешения записи регистра, с нулевым входом второго триггера и с единичным входом третьего триггера, выходы второго и третьего триггеров через соответствующие элементы И и второй элемент ИЛИ соединены с входом счетчика, выход которого соединен с нулевыми входами первого и третьего триггеров, а выходы группы счетчика соединены с информационными входами регистра, первый выход генератора тактовых импульсов соединен с вторым входом первого элемента И, а второй выход генератора тактовых импульсов соединен с входом блока управления памятью и с вторым входом второго элемента И.

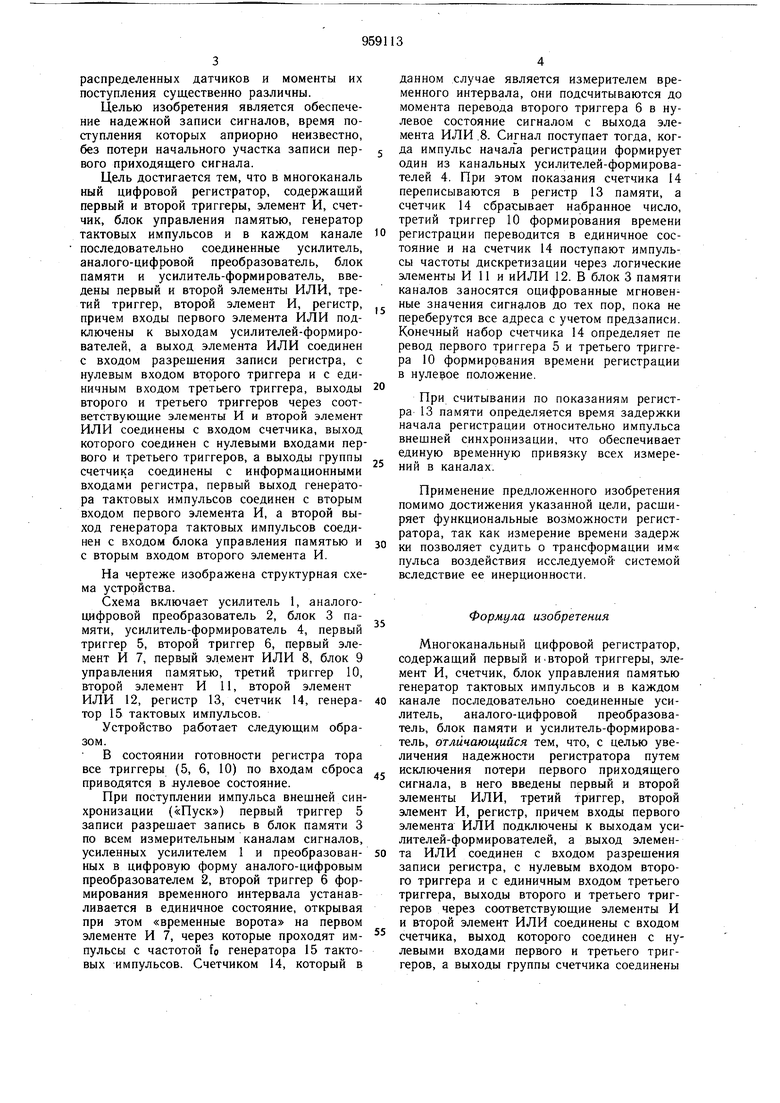

На чертеже изображена структурная схема устройства.

Схема включает усилитель 1, аналогоцифровой преобразователь 2, блок 3 памяти, усилитель-формирователь 4, первый триггер 5, второй триггер 6, первый элемент И 7, первый элемент ИЛИ 8, блок 9 управления памятью, третий триггер 10, второй элемент И 11, второй элемент ИЛИ 12, регистр 13, счетчик 14, генератор 15 тактовых импульсов.

Устройство работает следующим образом.

В состоянии готовности регистра тора все триггеры (5, 6, 10) по входам сброса приводятся в лулевое состояние.

При поступлении импульса внешней синхронизации («Пуск) первый триггер 5 записи разрешает запись в блок памяти 3 по всем измерительным каналам сигналов, усиленных усилителем 1 и преобразованных в цифровую форму аналого-цифровым преобразователем 2, второй триггер 6 формирования временного интервала устанавливается в единичное состояние, открывая при этом «временные ворота на первом элементе И 7, через которые проходят импульсы с частотой f генератора 15 тактовых импульсов. Счетчиком 14, который в

данном случае является измерителем временного интервала, они подсчитываются до момента перевода второго триггера 6 в нулевое состояние сигналом с выхода элемента ИЛИ ,8. Сигнал поступает тогда, когда импульс начала регистрации формирует один из канальных усилителей-формирователей 4. При этом показания счетчика 14 переписываются в регистр 13 памяти, а счетчик 14 сбрасывает набранное число, третий триггер 10 формирования времени регистрации переводится в единичное состояние и на счетчик 14 поступают импульсы частоты дискретизации через логические элементы И 11 и иИЛИ 12. В блок 3 памяти каналов заносятся оцифрованные мгновенные значения сигналов до тех пор, пока не переберутся все адреса с учетом предзаписи. Конечный набор счетчика 14 определяет пе ревод первого триггера 5 и третьего триггера 10 формирования времени регистрации в нулевое положение.

При считывании по показаниям регистра 13 памяти определяется время задержки начала регистрации относительно импульса внешней синхронизации, что обеспечивает единую временную привязку всех измерений в каналах.

Применение предложенного изобретения помимо достижения указанной цели, расширяет функциональные возможности регистратора, так как измерение времени задерж ки позволяет судить о трансформации им« пульса воздействия исследуемой- системой вследствие ее инерционности.

Формула изобретения

Многоканальный цифровой регистратор, содержащий первый и второй триггеры, элемент И, счетчик, блок управления памятью генератор тактовых импульсов и в каждом канале последовательно соединенные усилитель, аналого-цифровой преобразователь, блок памяти и усилитель-формирователь. Отличающийся тем, что, с целью увеличения надежности регистратора путем исключения потери первого приходящего сигнала, в него введены первый и второй элементы ИЛИ, третий триггер, второй элемент И, регистр, причем входы первого элемента ИЛИ подключены к выходам усилителей-формирователей, а выход элемента ИЛИ соединен с входом разрешения записи регистра, с нулевым входом второго триггера и с единичным входом третьего триггера, выходы второго и третьего триггеров через соответствующие элементы И и второй элемент ИЛИ соединены с входом счетчика, выход которого соединен с нулевыми входами первого и третьего триггеров, а выходы группы счетчика соединены

с информационными входами регистра, первый выход генератора тактовых импульсов соединен с вторым входом первого элемента И, а второй выход генератора тактовых импульсов соединен с входом блока управления памятью и с вторым входом второго элемента И.

Источники информации, принятые во внимание при экспертизе

№ 373695, кл. G 04 F 11/08, 1971 (прототип).

Авторы

Даты

1982-09-15—Публикация

1981-02-02—Подача