1

Устройство относится к области вычислительной техники, может быть использовано для задержки во времени как одиночных, так и последовательностей импульсов, в устройствах телеметрической и радиолокационной аппаратуры.

Известна однотактная линия задержки импульсов, по авт. св. № 401004, содержащая последовательно соединенные ячейки, каждая из которых выполнейа на трех логических элементах И-НЕ/ ИЛИ-НЕ, образующих друг с другом триггерные структуры 1 .

Недостатком известной линии является низкая надежность.

Целью настоящего изобретения является повышение надежности одно и двухразрядной линии задержки.

Для этого в однотактную линию задержки импульсов, содержащую последовательно соединенные разряды, каждый из которых выполнен на трех логических элементах И-НЕ/ ИЛИ-НЕ, образующих друг с другом триггерные структуры, выход одного из логических элементов И-НЕ/ ИЛИ-НЕ каждого пред ьщущего разряда соединен с входами двух логических элементов И-НЕ/ ИЛИ-НЕ каждого последующего разряда, а выходы третьего логического элемента И-НЕ/ ИЛИ-НЕ,последующих разрядов соединены с входами одноименных логических .элементов И-НЕ/ ИЛИ-НЕ предыдущего разряда, при этом источник тактовых импульсов подключен к входам логических элементов И-НЕ ИЛИ-НЕ, ВЫХОДЫ которых соединены с входом двух логических элементов. И-НЕ/ ИЛИ-НЕ каждого последующего разряда, в оконечный

каскад введен триггер, при этсм его входы соединены с выходами первого и вторюго логических элементов соответственно, а выход нечетного плеча триггера - с входом третьего элемента ..

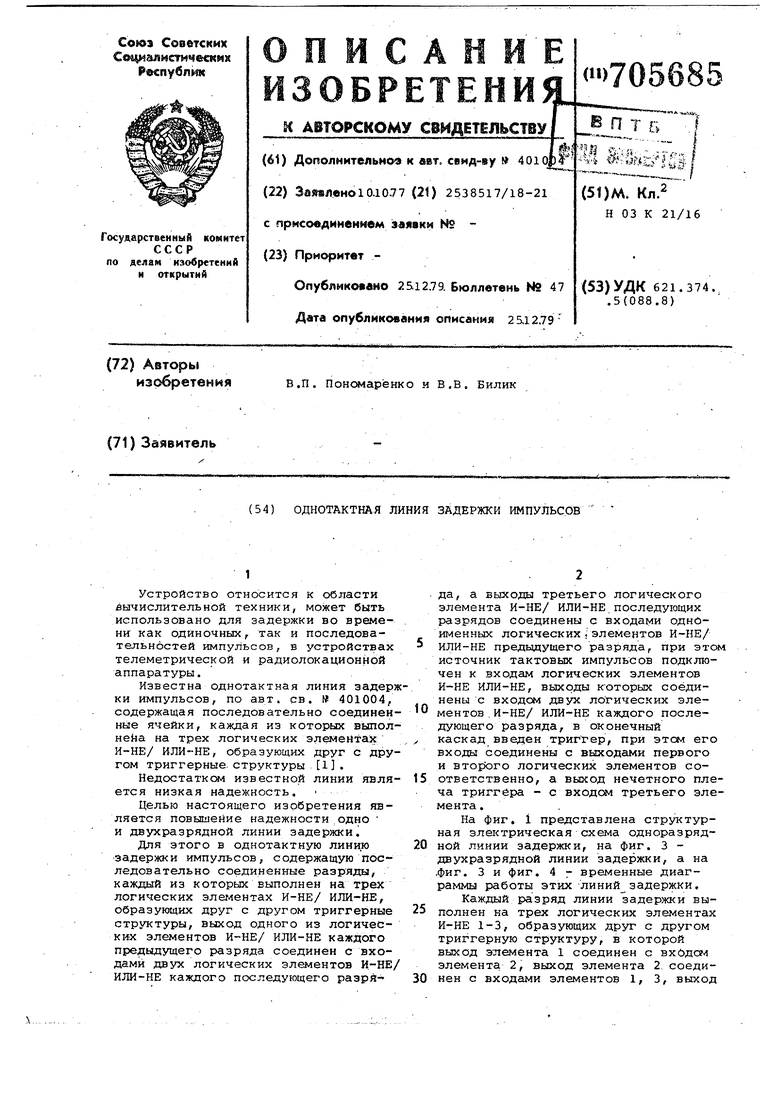

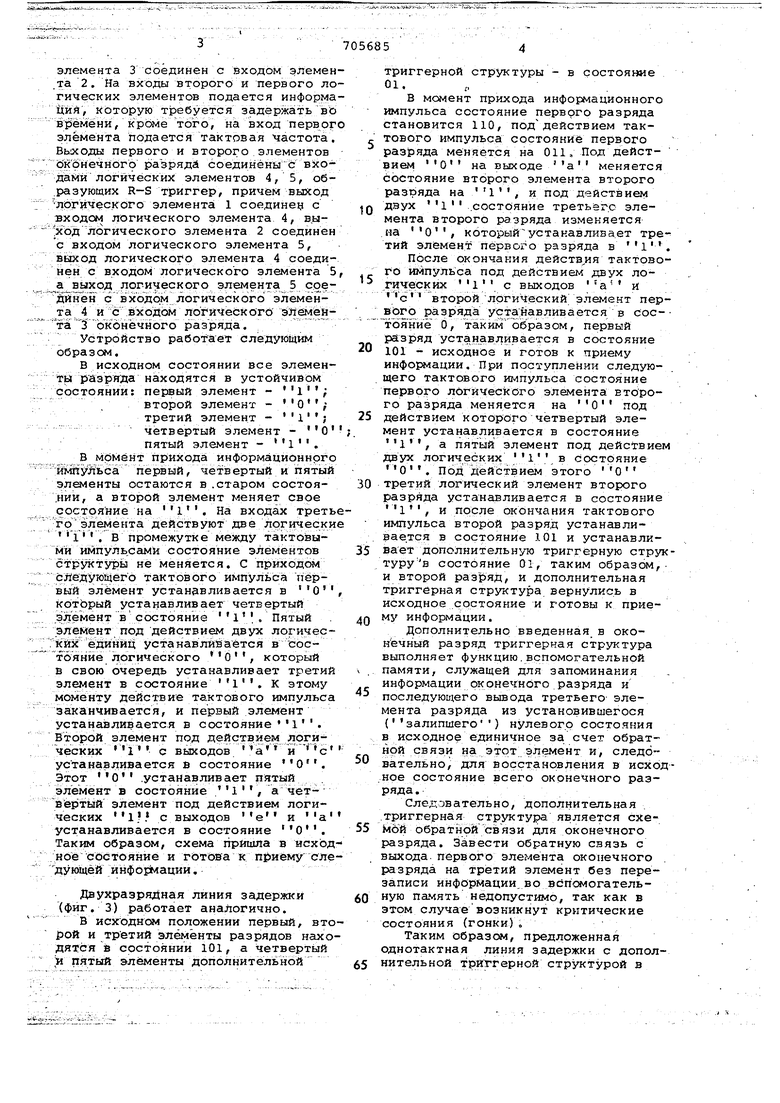

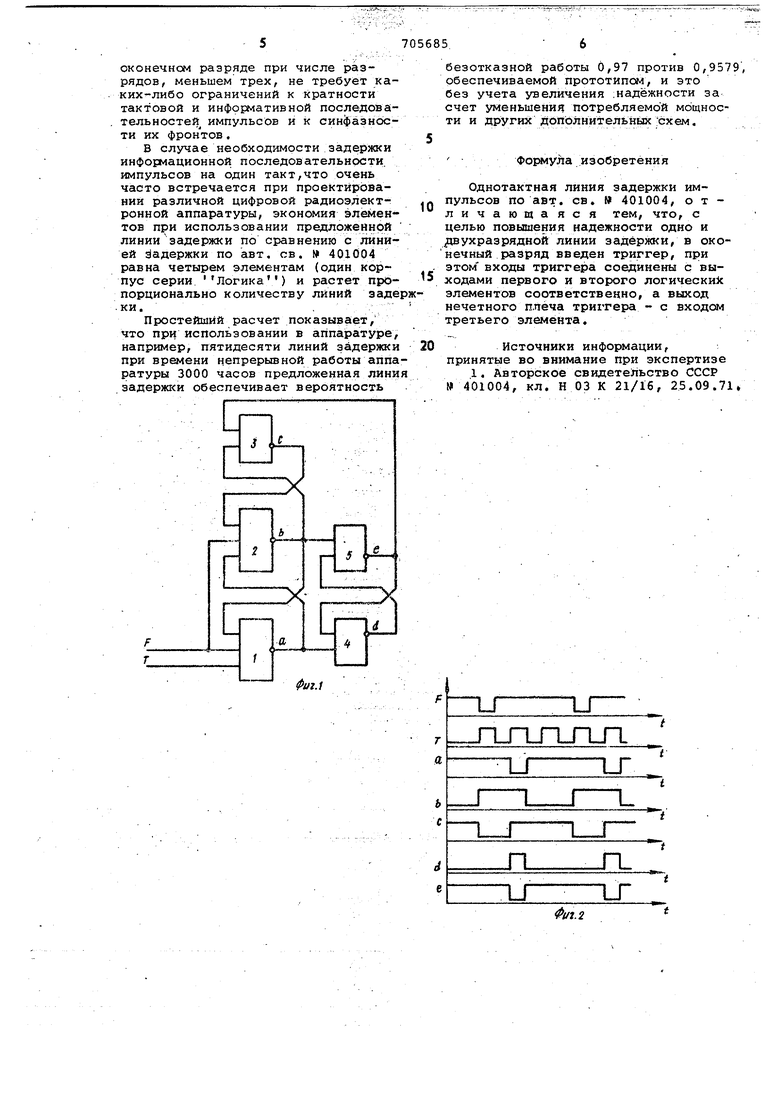

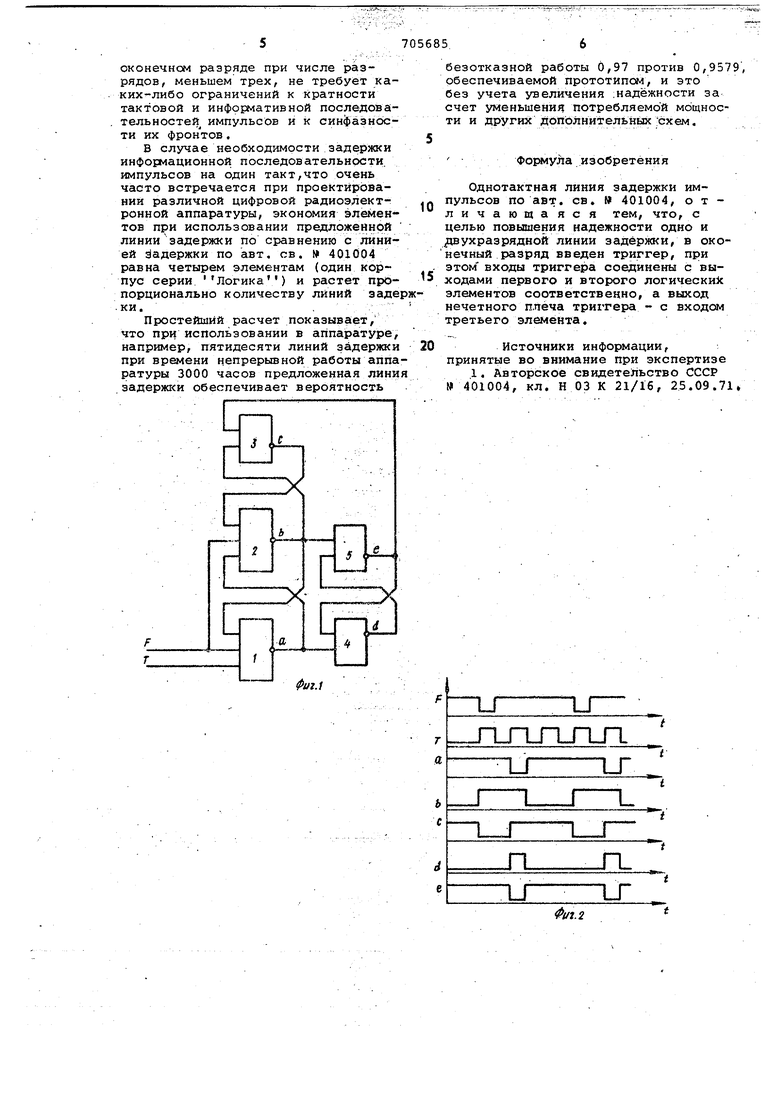

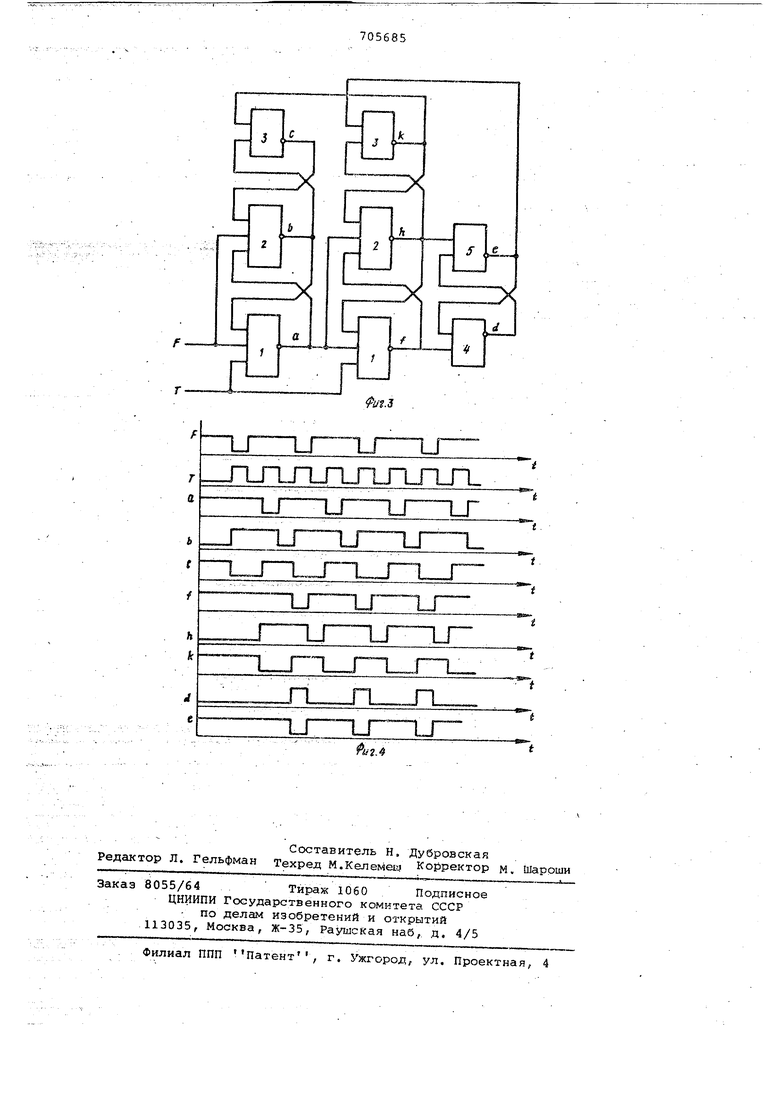

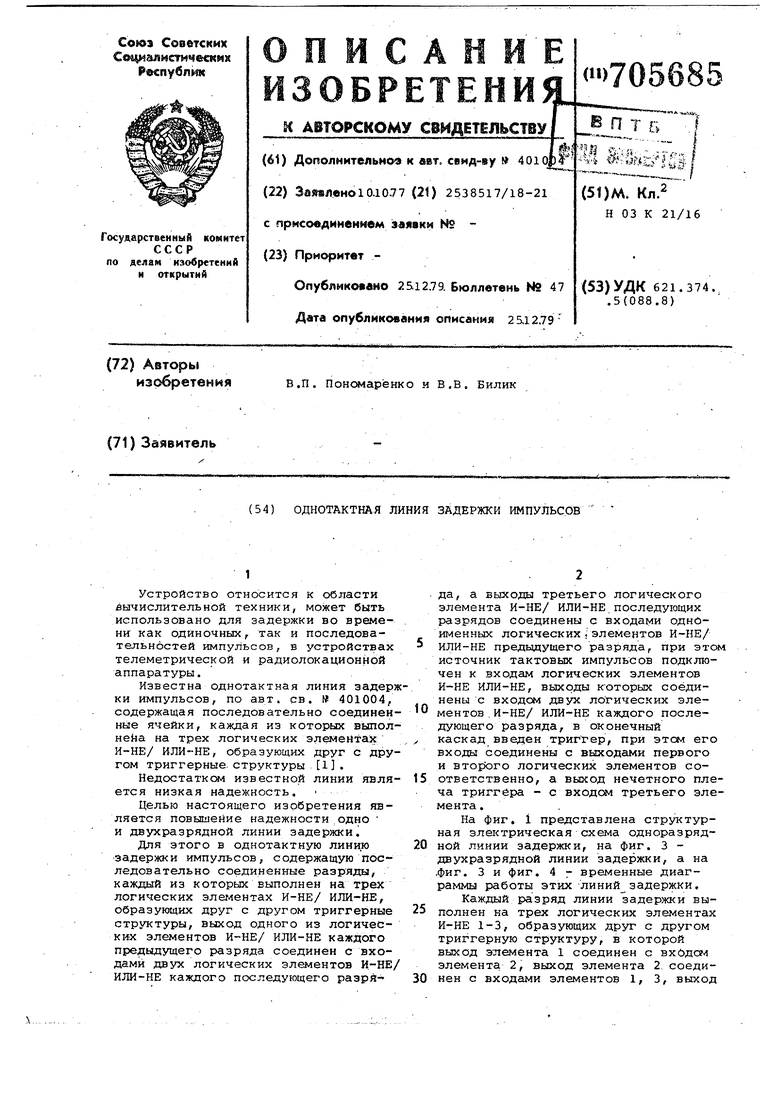

На фиг. i представлена структурная электрическая схема одноразрядной линии задержки, на фиг. 3 двухразрядной линии задержки, а на .фиг. 3 и фиг. 4 - временные диаграммы работы этих линий задержки.

Каждый разряд линии задержки выполнен на трех логических элементах И-НЕ 1-3, образующих друг с другом триггерную структуру, в которой выход элемента 1 соединен с вхОдсм элемента 2, выход элемента 2 соединен с входами элементов 1, 3, выход элемента 3 соединен с входом длемен та 2. На входы второго и первого ло гических элементов подается информа ция/которую требуется задержатьвЪ времени, кроме того, на вход первог элемента подается тактовая частота Вьходы первого и второго элементов окбнечного разряди соединены входами логических элементов 4, 5, образующих R-S триггер, причем выход логического элемента 1 соединен с входом логического элемента 4, выход логического элемента 2 соединен с входом логического элемента 5, ввкод логического элемента 4 соеди йен с входом логического элемента а выход логического элемента 5 с.ое ййнён с входом логического элементЭ 4 и с.входом Л ОГйЧеског6 эИёмей та Токонёчйого разряда, Устройство работэет следуйщим образом, В исходном состоянии все элементу разряда находятся в устойчивом состоянии: первый элемент - 1 . второй элемент - О ; третий элемент - 1 четвертый элемент пятый элемент - 1 В момент прихода информационнс1го :ймйуйьса первый, четв ертый и пятый элементы остаются в.старом состоящий, а второй элемент меняет свое состояние на , На входах треть го элемента действуют две логически , В промежутке между тактовыМи импульс ами с осто я ни е элеме и тов структуры не меняется, С приходом сйёдувдёго так тов ого импульса первый элемент устанавливается в О котЬрый устанавливает четвертый элемент в состояние элемент под действием двух логичес: Лих ёдинйй устанавливается в соскоторыйтояние логического в свою очередь устанавливает третий элемент в состояние . К этому моменту действие тактового импульса заканчивается, и первый элемент устанавливается в состояние . Второй элемент под действ.ием логических i с выходов а и с устанавливается в состояние О, Этот О .устанавливает пятый а четэлемент в состояние вертШ элемент под действием логических 1 . с выходов и -а устанавливается в состояние О Таким образом, схема пришла в исхОд ноё состояние и готова к приему сле дующёй инфо1 лации. Двухразрядная линия задержки (фиг, 3) работает аналогично, В исходнс положении первЕлй, вто рой и третий элементы разрядов нахо дятся IB состоянии 101, а четвертый й пятый элементы дополнительной триггерной структуры - в состояние 01. ,, В момент прихода информационного импульса состояние перврго разряда становится 110, поддействием тактового импульса состояние первого разряда меня1ется на Oil, Под дейстЕ1Ием О на выходе а меняется состояние второго элемента второго разряда на Ч, и под действием двух Ч .состояние третьего элемента второго разряда изменяется на О, к6торый устанавливает третий эл15мент пёрвох-о разряда в . После окончания действ ия тактового дачпульса под действием двух лос выходов а и гических IIвторойлогический элемент первого разряда устанавливается в сое- тояниё О, таким образом, первый разряд устанавливается в состояние 101 - исходное и готов к приему информации. При поступлении следующего тактового шипульса состояние первого логического элемента второго разряда меняется на действием которого четвертый элемент устанавливается в состояние Ч, а пятый элемент под действием двух логических 1 в состояние О . Под Действием этого О третий логический элемент второго разряда устанавливается в состояние Ч, и после окончания тактового импульса второй разряд устанавливается в состояние 101 и устанавливает дополнительную триггерную структуру в состояние 01, таким образом,и второй разряд, и дополнительная триггерная структура вернулись в исходное состояние и готовы к приему информации, Дополнительно введенная в оконечный разряд триггерная структура выполняет функцию.вспомогательной памяти, служащей для запоминания информации оконечного.разряда и последующего вывода третьего- элемента разряда из установившегося {залипшего) нулевого состояния в исходное единичное за счет обратной связи на этот элемент и, следовательно, для восстановления в исходное состояние всего оконечного разряда. Следовательно, дополнительная .триггерная структура является схеМбй обратной связи для оконечного разряда. Завести обратную связь с выхода, первого элемента оконечного разряда на Третий элемент без перезаписи информации во вЬпомогательную память недопустимо, так как в этом случаевозникнут критические состояния (гонки). Таким образом, предложенная однотактная линия задержки с дополнительной триТГерной структурой в оконечном разряде при числе разрядов, меньшем трех, не требует каких-либо ограничений к кратности тактовой и информативной последовательностей импульсов и к синфазнсюти их фронтов. В случае необходимости задержки информационной последовательнрсти. импульсов на один такт,что очень часто встречается при проектировании различной цифровой радиоэлектронной аппаратуры, экономия элементов при использовании предложенной линии задержки по сравнению с линией Задержки по авт. св. 401004 равна четырем элементам (один корпус серии Логика) и растет пропорционально количеству линий заде . ки.. -: Простейший расчет показыва;ет, что при использовании в аппаратуре, например, пятидесяти линий задержки при времени непрерывной работы аппа ратуры 3000 часов предложенная лини задержки обеспечивает вероятность

ФигЛ безотказной работы 0,97 против 0,9579, Обеспечиваемой прототипом, и это без учета увеличения :надёжности за счет уменьшения потребляемой мощности и других дополнительных :схем. Формула изобретения Однотактная линия задержки импульсов по авт. св. 401004, отличающаяся тем, что, с целью повышения надежности одно и цвухразрядной линии задержки, в оконечный разряд введен триггер, при этом входы триггера соединены с выходами первого и второго логический элементов соответственно, а выход нечетного плеча триггера - с входом третьего элемента. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР №401004, кл, Н 03 К 21/16, 25.09.71

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство измерения временных интервалов | 1984 |

|

SU1144062A1 |

| Устройство для коррекции сбойных кодов в кольцевом распределителе | 1979 |

|

SU888125A1 |

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

| Устройство для преобразования двоичного кода во временной интервал | 1986 |

|

SU1363475A1 |

| Устройство для сопряжения каналов ЭВМ с периферийными устройствами | 1990 |

|

SU1732348A1 |

| Нанопрограммное устройство управления | 1983 |

|

SU1136160A1 |

| Устройство управления | 1983 |

|

SU1166108A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| УСТРОЙСТВО РЕГИСТРАЦИИ СТАТИЧЕСКИХ ТЕЛЕВИЗИОННЫХ ИЗОБРАЖЕНИЙ | 1992 |

|

RU2054818C1 |

| Устройство для контроля регистра сдвига | 1978 |

|

SU752487A1 |

Авторы

Даты

1979-12-25—Публикация

1977-10-10—Подача