Изобретение относится к области вычислительной техники и может быть использовано в запоминающих устройствах ЭВМ.

Известны ячейки памяти на транзисторах со структурой металл-диэлектрик-полупроводник, содержащие триггер с перекрестными связями,элементы записи, считывания, опроса и ускоряющие элементы, причем стоки транзисторов элементов записи и затворы транзисторов элементов считывания и опроса подключены к плеча.м триггера, а стоки транзисторов элементов считывания и опроса подключены к выходным клеммам устройства.

Однако ячейки имеют общие ключи как для записи, так и для считывания информации и вследствие этого при осуществлении записи лищь в часть разрядов данного слова, происходит изменение уровней логических «О и «1 и триггер может оказаться в неустойчивом состоянии.

С целью обеспечения маскирования отдельных разрядов слова при записи информации в другие разряды того же слова с сохранением уровней двоичных «1 и «О в предлагаемом устройстве, каждый элемент записи выполнен в виде логического элемента «И, входы которого подсоединены к раздельным щинам «разрешение записи и «запись.

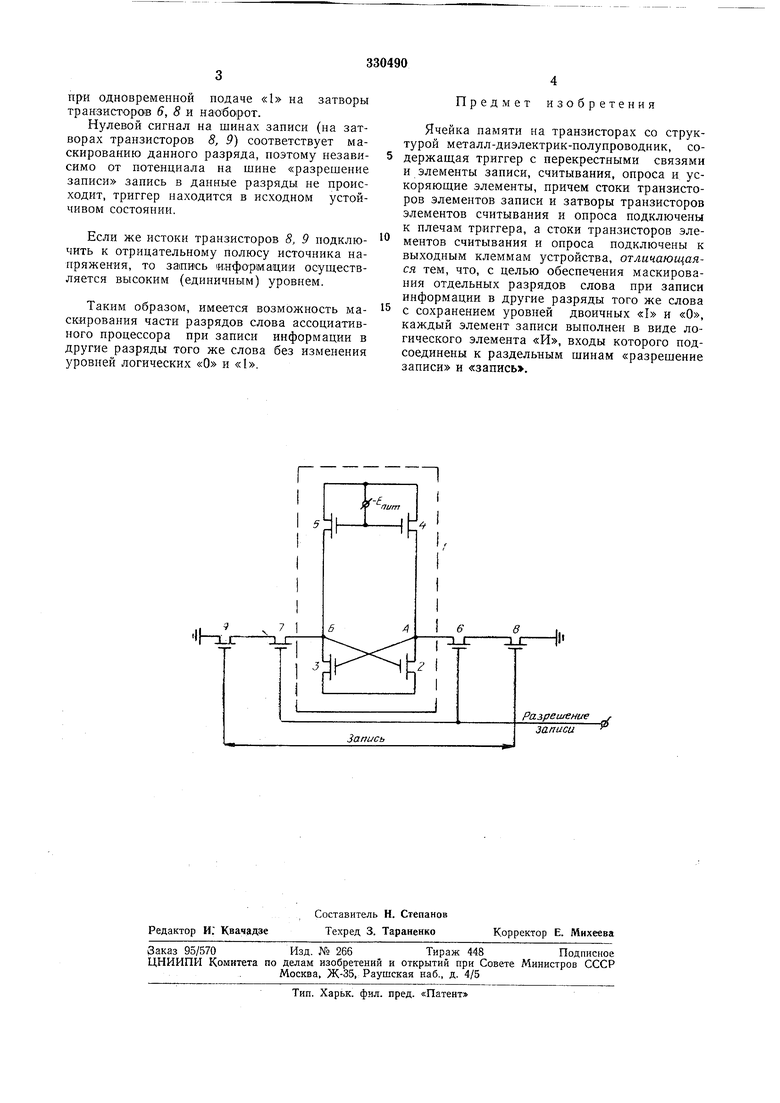

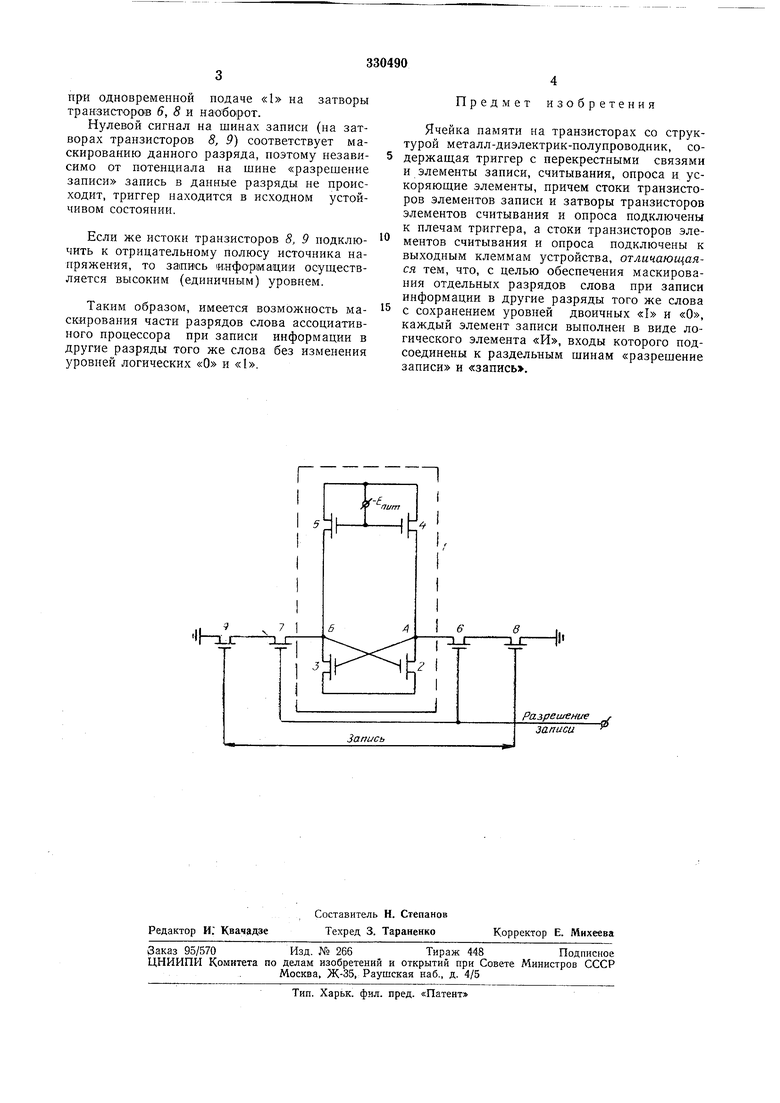

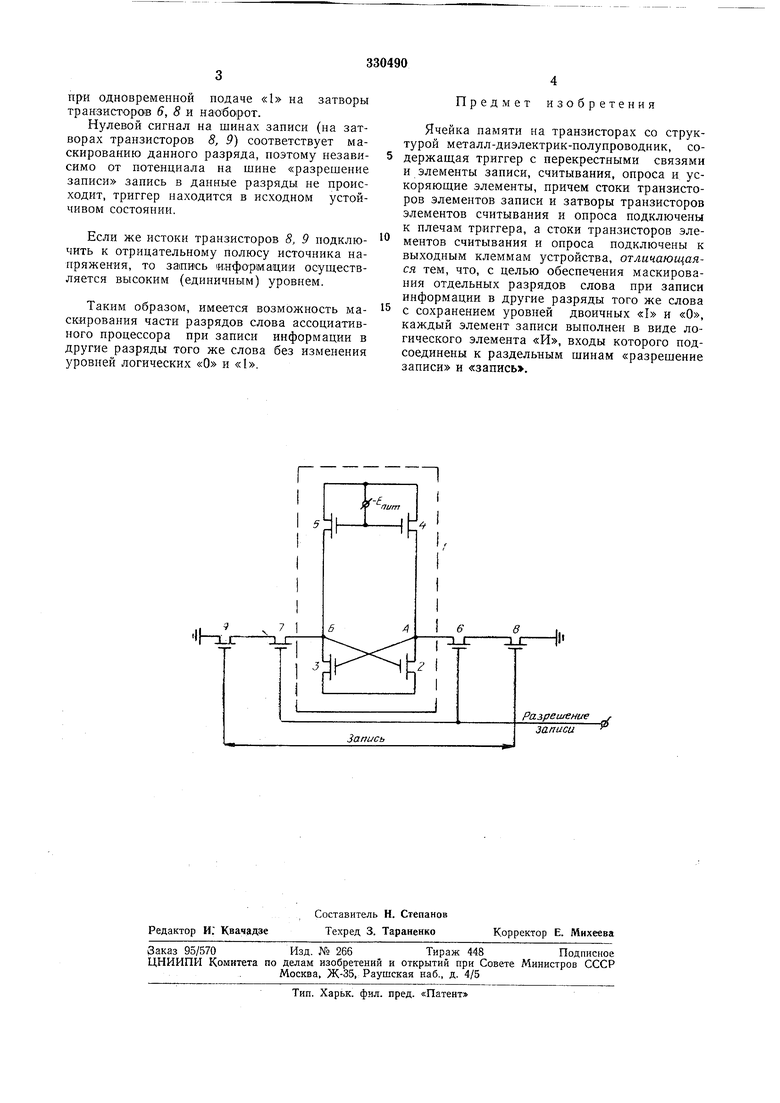

На чертеже приведена функциональная схема предлагаемого устройства.

Устройство содержит триггер /, выполненный на транзисторах 2-5 и элементы записи на транзисторах 6-9. Элементы считывания, опроса и ускоряющие элементы на чертеже не показаны.

Затворы транзисторов б и 7 используются в качестве ключей разрешения записи информации в триггер 1, а транзисторы 5 и Р используются в качестве ключей записи информации в этот триггер. Попарно транзисторы 6, 8 и 7, 9 образуют логические элементы «И для соответствующих плеч триггера /. Устройство работает следующим образом.

В исходном положении триггер / находится в одном из устойчивых состояний. Напряжение на затворах транзисторов 6-9 в этот момент соответствует уровню логического нуля.

Информация записывается только при одновременной подаче логической единицы на щину «разрешение записи и на щину «запись соответствующего плеча триггера.

при одновременной подаче «1 на затворы транзисторов 6, 8 к наоборот.

Нулевой сигнал на шинах записи (на затворах транзисторов 8, 9) соответствует маскированию данного разряда, поэтому независимо от потенциала на шине «разрешение записи запись в данные разряды не происходит, триггер находится в исходном устойчивом состоянии.

Если же истоки транзисторов 8, 9 подключить к отрицательному полюсу источника напряжения, то запись информации осушествляется высоким (единичным) уровнем.

Таким образом, имеется возможность маскирования части разрядов слова ассоциативного процессора при записи информации в другие разряды того же слова без изменения уровней логических «О и «1.

Предмет изобретения

Ячейка памяти на транзисторах со структурой металл-диэлектрик-полупроводник, содержащая триггер с перекрестными связями и элементы записи, считывания, опроса и ускоряющие элементы, причем стоки транзисторов элементов записи и затворы транзисторов элементов считывания и опроса подключены к плечам триггера, а стоки транзисторов элементов считывания и опроса подключены к выходным клеммам устройства, отличающаяся тем, что, с целью обеспечения маскирования отдельных разрядов слова при записи информации в другие разряды того же слова с сохранением уровней двоичных «I и «О, каждый элемент записи выполнен в виде логического элемента «И, входы которого подсоединены к раздельным шинам «разрешение записи и «запись.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативный запоминающий элемент на мдп-транзисторах | 1977 |

|

SU708417A1 |

| Элемент памяти для ассоциативного накопителя | 1976 |

|

SU690565A1 |

| ЗАПОМИНАЮЩИЙ ЭЛЕМЕНТ | 1970 |

|

SU283307A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1795521A1 |

| ПЬЕЗОТРАНСФОРМАТОРНОЕ ЗАПОЛИШАЮЩЕЕ УСТРОЙМТ?|11е0-1ЕЛКГ1:: | 1972 |

|

SU331421A1 |

| ЗАПОМИНАЮЩИЙ ЭЛЕЛ1ЕНТ | 1971 |

|

SU289446A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-СЧИТЫВАНИЯ | 1972 |

|

SU345517A1 |

| ЦЕНТРАЛЬНЫЙ ПРОЦЕССОР МУЛЬТИПРОГРАММНОЙ МУЛЬТИПРОЦЕССОРНОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1971 |

|

SU309363A1 |

| Запоминающее устройство | 1977 |

|

SU720509A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР СЛУЧАЙНЫХПРОЦЕССОВ | 1972 |

|

SU428409A1 |

Авторы

Даты

1972-01-01—Публикация