I

Изобретение относится к области вышслительной техники, а именно к запоминающим устройствам (ЗУ).

Известны запоминающие элементы, в кото.рых поиск информащ1И может осуществляться на основе ограниченного количества функции 2-х переменных и требуется для реализации ассоциатавного поиска значительное количество транзисторов 1 .

Известен также запоминающий элемент, содержащий основной и вспомогательный накопительные конденсаторы, транзистор считывания, адресный транзистор, транзистор записи, запоминающий транзистор и щины: адресную разрядную, считывания и записи, маскирования записи 2.

Этот элемент памяти является наиболее близким техническим рещением к предлагаемому.

Недостаток известного злемента памяти состоит в том, что он предназначен только для работы в составе оперативного ЗУ, выполняя функ7&1ю записи, хранения и считывания информации.

Целью изобретения является расЩирениё Ъбласти применения Галемента памяти за t счет осуществления поиска информации на основе произвольной функции двух переменных.

Поставленная цель достигается тем, что в элемент памяти введен второй запоминающий транзистор, затвор которого соединен с истоком ajqjecHoro транзистора, сток - с щиной сравнения, исток - с одной и щин опроса, исток первого запоминающего траншстора и другая обкладка первого конденсатора соедагаешл с шиной опроса.

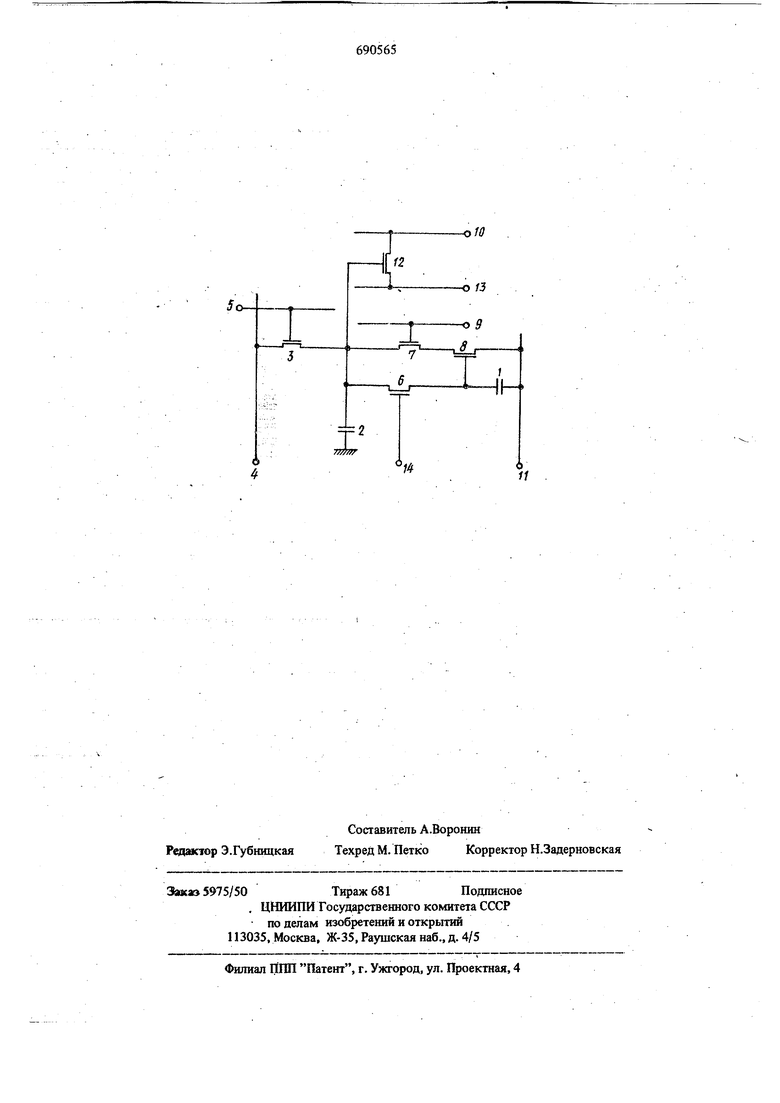

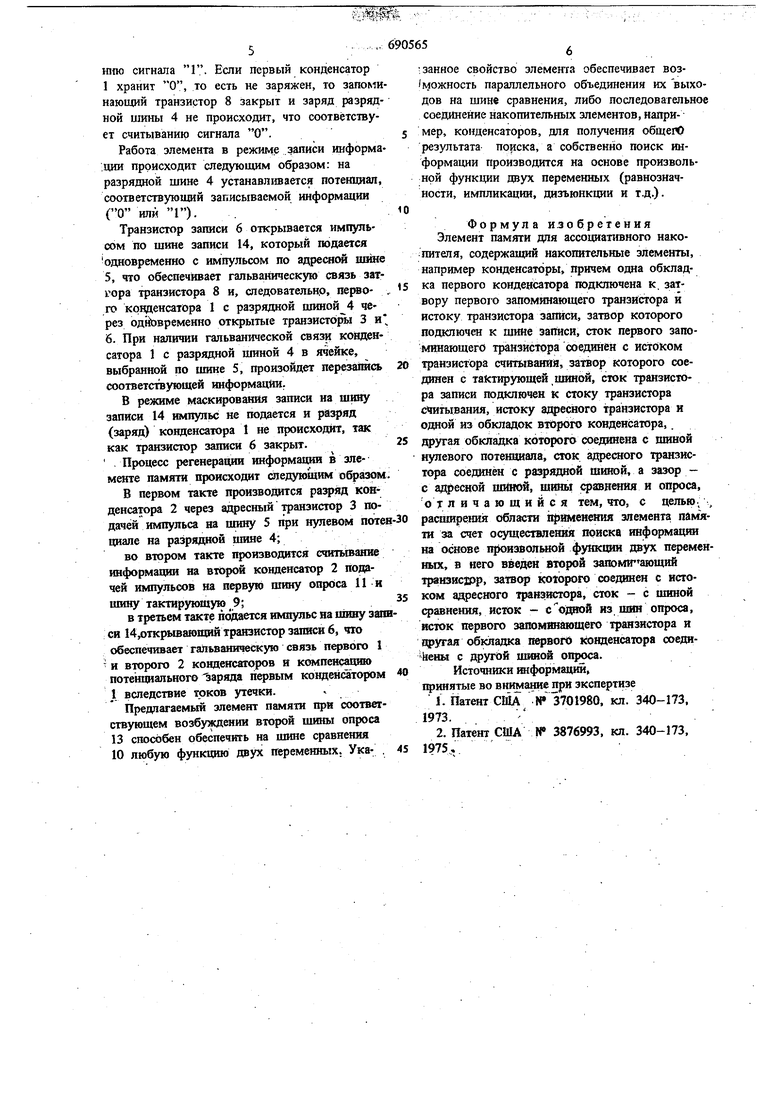

На чертеже изображена схема элемента паЬ4яти.Элемент памяти содержит первый конденсатор - 1; второй ко1Здшсатор - 2; адресный транзистор - 3; разрядную шину - 4; ащзесную шину - 5; транзистор записи - 6; транзистор считывания - 7; первый запоминающий транзистор - 8; тактирующую зону 9; шину сравнения - 10; первую шину опроса - 11; второй запоминающий транзистор - 12; вторую цпшу опроса - 13 и щину записи 14.

Элемент памятл работает следующим образом. В режиме поиска 1 в первом такте на адресную шину 5 подается импульсный сигнал, открывающий адресный транзистор 3, а на разрядную шину 4 сигнал логической 1, представленный потенциалом, который заряжает втброй конденсатор 2, связанный с затвором второго запоминающего транзистора 12, через открытый сигналом по адресной шине 5 адресный транзистор 3 до уров|ня логической единицы. Одновременно производится заряд паразитной емкости 1апйаы сраднения 10 анешними источниками до уровня логической 1 при наличии импульса на шине 13, блокирующему сквозной ток через транзистор 12 в процессе заряда. Во втором такте на тактирзпющую нгану 9 подается , открываюидай транзистор считывания 7, а на первую шину опроса 11 подается нулевой потенциал. В случае хранения 1 второй конденсатор 2 ргиряжается через открытые транзисторы считывания 7 и перяый запоминающий транзистор 8 до уровня логического О, импульс с ишны 13 енимается, а заряд на шине сравншия 10 сохраняется, так как второй запоминающий транзистор 12 оказываетсй закрытым, что соответствует сигналу совпадения при поиске 1. В случае хршення О второй конденсатор 2 и вход транзистора 12 сохраняют: потенциал логической 1 что обеспечивает разряд паразитной емкости поош сравнения 10 до уровня HoriPtecKoro О через открытый второй запоминающий транзистор 12 после снятия импульса с шины 13 и соответствует сигналу несовпадения при поис1 е 1.

В режиме поиска О в первом такте иа разрядную шину 4 подается сигнал логического О, представленного нулевым потенциалом, который разряжает второй конденсатор 2 до уровня логического О через .адресный транзистор 3 на затвор которого подается импульсный сигнал, открьгеающий адресный затвор 3.

Во втором такте на тактирующую тину 9 подается импульс, открывающий транзистор считывания 7, а на первую шину опроса 11 импульс, опрашивающий состояние первого конденсатора 1.

Если первый ко1вденсатор 1 хранит логическую I, то есть заряжен; транзистор считывания 7 открыт к на входе второго запоминающего транзистора 12 устанавливается сигнал логической 1, так как второй конденсатор 2 заряжается через транзистор считывания 7 и первый запоминающий транзис

тор 8 импульсов опроса, и шина сравнения 10 разряжается до уровня логического О через открытый второй запоминающий транзистор 12 после окончания импульса на второй шине опроса 13, что соответствует сигналу несовпадения при поиске О.

В случае маскирования при поиске в первом такте подается потенциал О на разрядную ишну 4. и производится разряд второго конденсатора 2 через адресный транзистор 3, открытый импульсом на адресной щине 5,а также предварительный заряд шины сравнения 10, во втором уакте импульс onpdca на первую ишну опроса 11 не подается, что и обеспечивает сохранение сигнала О на входе транзистора 12, а также потенциала логической 1 шины сравнения 10, соответствующего совпадения при поиске О и 1. Таким образом, режим маскирования при поиске отличается от режима поиска О блокирбванием импульса опроса по первой шине опроса 11 во втором такте.

Таким образом, на затворе транзистора 12 в процессе поиска устанавливается значение результата сравнения хранимой в запоминающем злементе информации с внешней информ цией, поступающей в ассоциативное запоминающее устройство (АЗУ) для операции поиска. В случае совпадения всех разрядов какого-либо слова АЗУ с внешним словом на затворщс запоминающих транзисторов 12 всех злементов памяти, образующих слово, устанавливается уровень логического О как резуль тат сравнения в каждом отдельном разряде. Шина сравнения 10 зтих слов, образованная объеданением стоков транзисторов 12, после |снятия 1шпульса предварительного заряда с |щины 13, остается заряженной (в состоянии логической 1), так как транзисторы 12. окажутся закрытыми. На шнне сравнетая 10 нулевой потенциал будет устанавливаться только в случае несовпадения информации хотя бы одной ячейки данного слова АЗУ с соответствующим разрадом входного слова, что и требуется для функционирования АЗУ.

Работа злемента в режиме считывания информации происходит следующим образом.

В первом такте на разрядной шине 4 устшавлнвается нулевой потенциал. Во втором такте подаются управляющие имПульсы на адресную щину 5, первую шину опроса 11, тактирующую шину 9. Если первый конденсатор хранит 1, то есть заряжен, первый запоминающий транзистор 8 открыт и происходит заряд разрядной шины 4 через открытые транзисторы считывания 7 и запоминающий транзистор 8 импульсом опроса первой цшны опроса II, что соответствует считываН1ПО сигнала 1. Если первый конденсатор 1 хранит О, то есть не заряжен, то запоми нающий транзистор 8 закрыт и заряд разрядной шины 4 не происходит, что соответствует считыванию сигнала О. Работа элемента в режимр записи информа ,щш происходит следующим образом: на разрядной шине 4 устанавливается потенциал, соответствующий записываемой информации (О или 1).. Транзистор записи 6 открывается импульсом по шине записи 14, который подается одновременно с импульсом по адресной цогае 5,что обеспечивает гальваническую связь затvopa транзистора 8 и, следовательир, пе{шого крвдеисатора 1 с разрядной шиной 4 через одйовременно открытые транзистЬ рт) 3 и 6.При наличии гальванической связи конденсатора 1 с разрядной шиной 4 в ячейке, выбранной по шине 5, произойдет перезапись соответствующей информации. В режиме маскирования записи на Щ1Шу записи 14 импульс не подается и разряд (заряд) конденсатора 1 не происходат, так как транзистор записи 6 закрыт. .Процесс регенерации информации в элементе памяпги происходит (яедующим образом В первом такте производится разряд конденсатора 2 через адресный транзистор 3 подачей импульса на шину 5 при нулевом поте циале на разрядной цпше 4; во втором такте производится считывание информации на второй конденсатор 2 подачей импульсов на первую шину опроса И н нпшу тактируиицую 9; в третьем такте подается импульс на ипшу зап си 14,открьшающий транзистор записи 6, что обеспечивает гальваническую связь первого 1 и второго 2 конденсаторов и компенсшию потенциального заряда первьпи конденсатором 1 вследствие токов утечки. Предлагаемый элемент памяти прн соответствующем возбуждении второй шины опроса 13 способен обеспечить на щине сравнения 10 любую функцию двух переменньтх. Ука- . :3анное свойство элемента обеспечивает возможность параллельного объединения их выходов на шине сравнения, либо последовательное соединеИие накопительных элементов, натфимер, конденсаторов, доя получения общего результата по|1ска, а собственно поиск информации производится на основе произвольной функции двух переменных (равнозначности, импликации, дизъюнкции и т.д.). Формула изобретения Элемент памяти для ассоциат1шного накопителя, содержащий накопительные злементы, например конденсаторы, причем одна обкладка первого конденсатора тодключеиа к, затвору первого запомиишощего транзистора и истоку транзистора зштси, затвор которого подключен к шине записи, сток первого запоминающего транзистора соединен с истоком транзистора считывания, затвор которого соединен с тakтиpyюIцeй щиной, сток транзистора записи подключен к стоку транзистора считывания, истоку афесяого транзистора и одаой из обкладок второго конденсатора, другая обкладка которого соединена с шиной нулевого потенциала, сток ащ есного транзистора соединён с разрядной шиной, а зазор с адресной шиной, шшшг сравнения н опроса, от личающийся тем, что, с целью., расширения области фйменения элемента памяти за счет осуществления поиска информации на основе )нзволыюй функции двух переменньа, в него введен второй запомгающий транзисзрр, затвор которого соединен с нстоком адресного 7ранз1{стора, сток - с шнной равнения, исток - сводной нз шин опроса, исток первого запомшшощего транзистора н оругая обкладка первого конденсатора соедиЬены с ццшой опроса. Источники шформащш, принятые во внимание при экспертизе J. Патент США N 1701980, кл. 340-173, 1973.2. Патент США К 3876993, кл. 340-173, 1975,

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативный запоминающийэлЕМЕНТ | 1979 |

|

SU805412A1 |

| Полупроводниковая ячейка памяти | 1976 |

|

SU723680A1 |

| Элемент памяти | 1979 |

|

SU788175A1 |

| Ассоциативная ячейка памяти | 1976 |

|

SU605268A1 |

| Ячейка памяти | 1977 |

|

SU693437A1 |

| Устройство для считывания информации из блоков памяти | 1977 |

|

SU746718A1 |

| Ячейка памяти на мдп-транзисторах | 1975 |

|

SU533988A1 |

| Устройство для считывания информации из ассоциативного запоминающего блока | 1974 |

|

SU497636A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Ассоциативный запоминающий элемент на мдп-транзисторах | 1975 |

|

SU542243A1 |

Авторы

Даты

1979-10-05—Публикация

1976-09-27—Подача