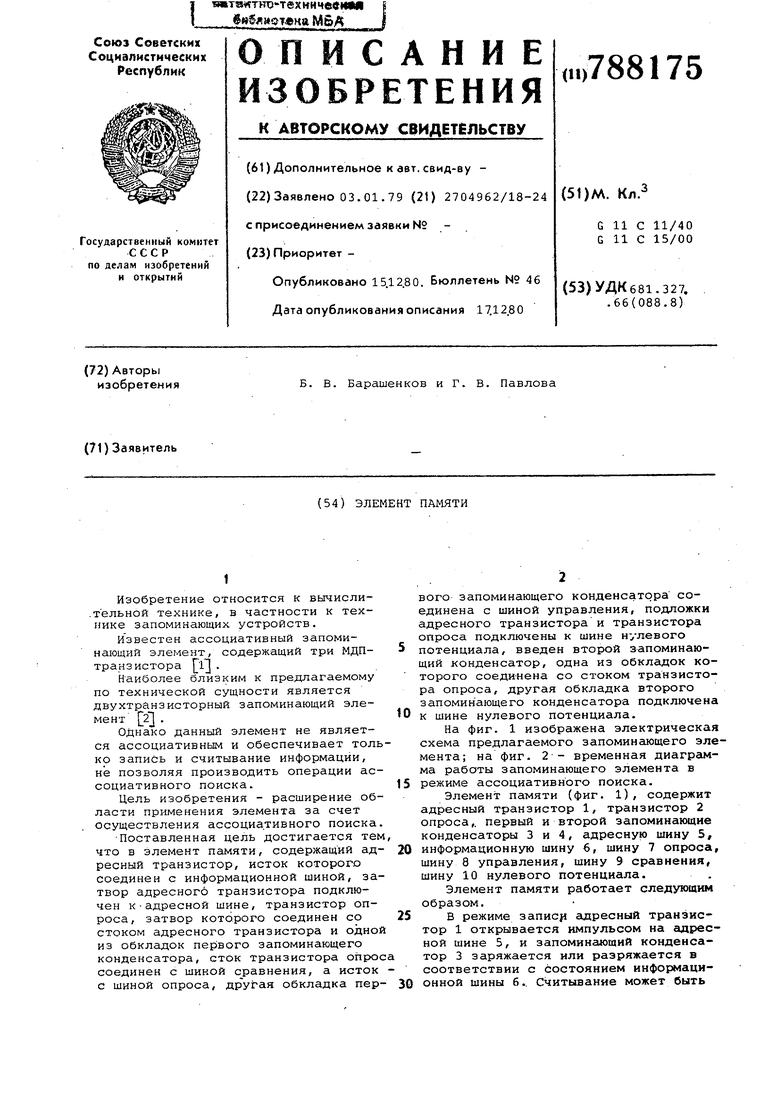

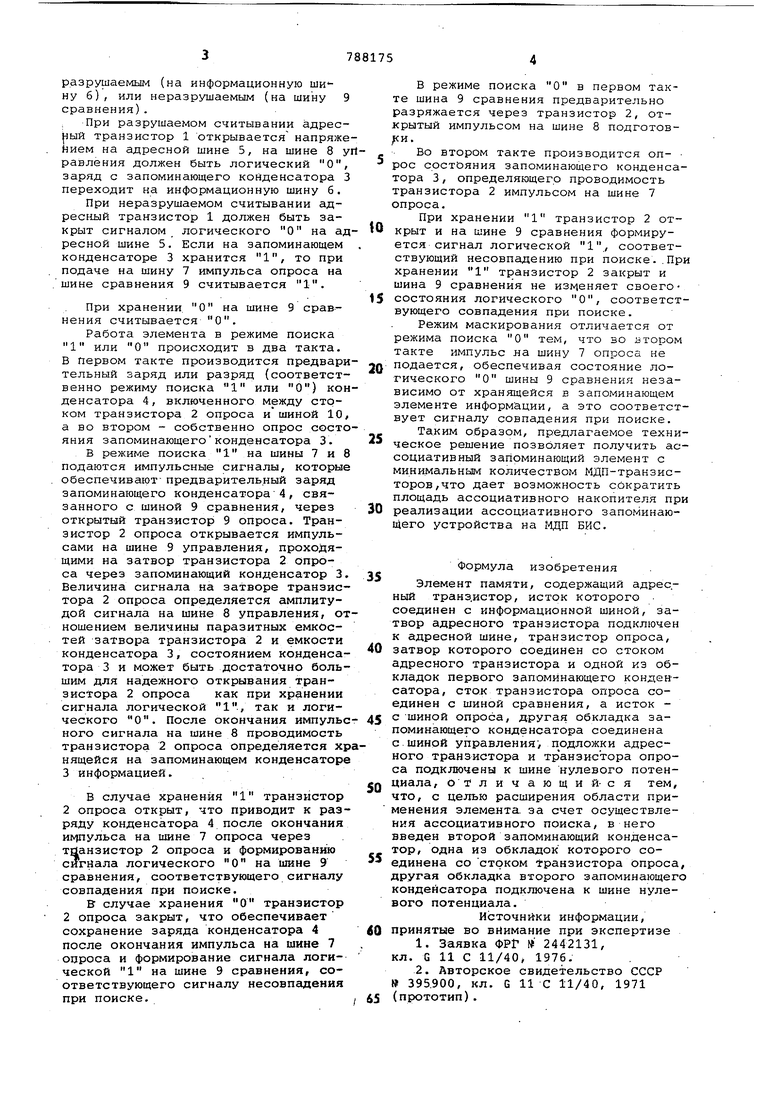

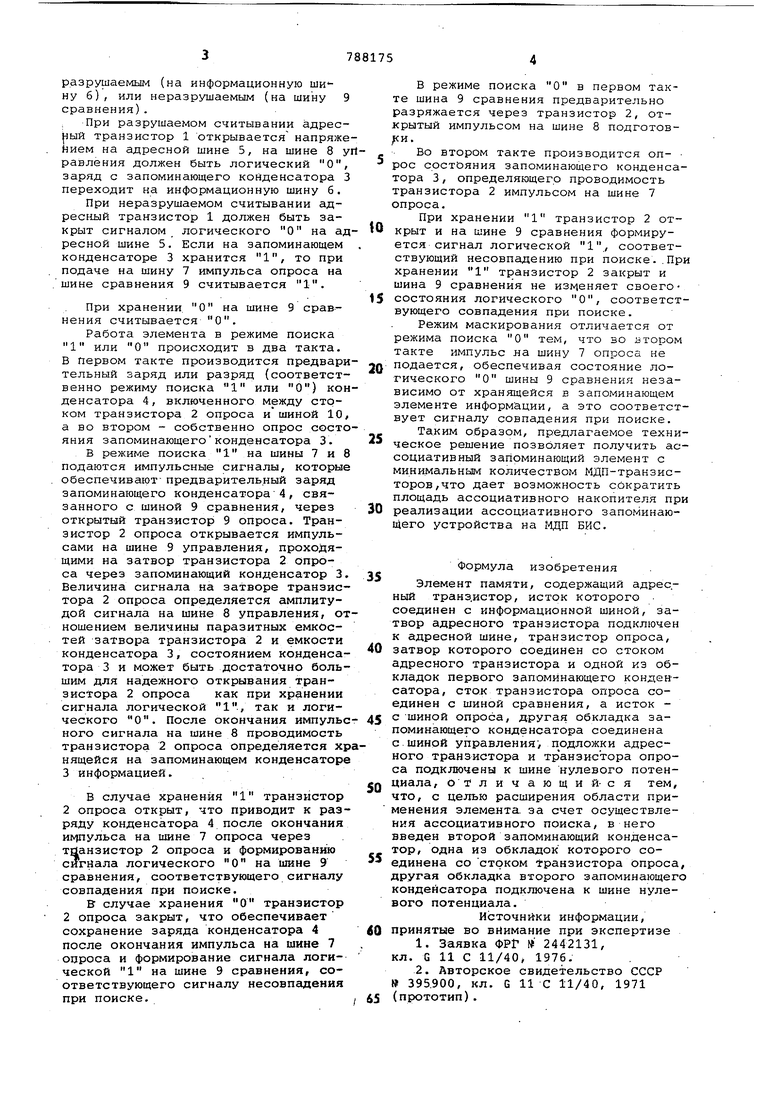

Изобретение относится к вычисли.тельной технике, в частности к технике запоминающих устройств. Известен ассоциативный запоминающий элемент, содержащий три МДПтранзистора 1 . Наиболее близким к предлагаемому по технической сущности является двухтранзисторный запоминающий элемент 2 . Ойнако данный элемент не является ассоциатиБНЕлм и обеспечивает толь ко запись и считывание информации, не позволяя производить операции ассоциативного поиска. Цель изобретения - расширение области применения элемента за счет Осуществления ассоциативного поиска -Поставленная цель достигается тем что в элемент памяти, содержащий адресный транзистор, исток которого соединен с информационной шиной, за твор адресного транзистора подключен кадресной шине, транзистор опроса, затвор которого соединен со стоком адресного транзистора и одно из обкладок первого запоминающего конденсатора, сток транзистора опро соединен с шиной сравнения, а исток с ШИНОЙ опроса, другая обкладка пер вого запоминающего конденсатора соединена с шиной управления, подложки адресного транзистора и транзистора опроса подключены к шине нулевого потенциала, введен второй запоминающий конденсатор, одна из обкладок которого соеди-нена со стоком транзистора опроса, другая обкладка второго запоминающего конденсатора подключена к шине нулевого потенциала. На фиг. 1 изображена электрическая схема предлагаемого запоминающего элемента; на фиг. 2 - временная диагргилма работы запоминающего элемента в режиме ассоциативного поиска. Элемент памяти (фиг. 1), содержит адресный транзистор 1, транзистор 2 опроса,, первый и второй запоминающие конденсаторы 3 и 4, адресную шину 3, информационную шину 6, шину 7 опроса, шину 8 управления, шину 9 сравиения, шину 10 нулевого потенциала. Элемент памяти работает следующим образом. В режиме записр адресный транзистор 1 открывается импульсом на адресной шине 5, и запомингиощий кондеисатор 3 заряжается или разряжается в соответствии с состоянием информационной шины 6. Считывание может быть разрушаемым (на информационную 6), или неразрушаемым (на шину 9 сравнения). При разрушаемом считывании адрес|1ый транзистор 1 открывается напряже нием на адресной шине 5, на шине 8 y равления должен быть логический О заряд с запоминающего конденсатора 3 переходит на информационную шину 6. При неразрушаемом считывании адресЕ1ый транзистор 1 должен быть зана ад крыт сигналом логического ресной шине 5. Если на запоминающем конденсаторе 3 хранится 1, то при подаче на шину 7 импульса опроса на шине сравнения 9 считывается 1. При хранении О на шине 9 срав-нения считывается О. Работа элемента в режиме поиска 1 или О происходит в два такта, В первом такте производится предвари тельный заряд или разряд (соответственно режиму поиска 1 или О) кон денсатора 4, включенного между стоком транзистора 2 опроса и шиной 10 а во втором - собственно опрос состо яния запоминающегоконденсатора 3. В режиме поиска 1 на шины 7 и 8 подаются импульсные сигналы, которые обеспечиваютпредварительный заряд запоминающего конденсатора 4, связанного с шиной 9 сравнения, через открытый транзистор 9 опроса. Транзистор 2 опроса открывается импульсами на шине 9 управления, проходящими на затвор транзистора 2 опроса через запоминающий конденсатор 3 Величина сигнала на затворе транзис тора 2 опроса определяется амплитудой сигнала на шине 8 управления, о ношением величины паразитных емкостей затвора транзистора 2 и емкости конденсатора 3, состоянием конденса тора 3 и может быть достаточно боль шим для надежного открывания транзистора 2 опроса как при хранении сигнала логической 1, так и логического О. После окончания импуль ного сигнала на шине 8 проводимость транзистора 2 опроса определяется х нящейся на запоминающем конденсатор 3 информацией. В случае хранения 1 транзистор 2 опроса открыт, что приводит к раз ряду конденсатора 4 после окончания импульса на шине 7 опроса через тйанзистор 2 опроса и формированию сигнала логического О на шине 9 сравнения, соответствующего сигналу совпадения при поиске. В случае хранения О транзистор 2 опроса закрыт, что обеспечивает сохранение заряда конденсатора 4 после окончания импульса на шине 7 опроса и формирование сигнала логической 1 на шине 9 сравнения, соответствующего сигналу несовпадения при поиске. в режиме поиска О в первом такте шина 9 сравнения предварительно разряжается через транзистор 2, открытый импульсом на шине 8 подготов; и. Во втором такте производится оп- рос состояния запоминающего конденсатора 3, определяющего проводимость транзистора 2 импульсом на шине 7 опроса. При хранении 1 транзистор 2 открыт и на шине 9 сравнения формируется сигнал логической 1., соответствующий несовпадению при поиске..При хранении 1 транзистор 2 закрыт и шина 9 сравнения не изменяет своегосостояния логического О, соответствующего совпадения при поиске. Режим маскирования отличается от режима поиска О тем, что зо втором такте импульс на шину 7 опроса не подается, обеспечивая состояние логического О шины 9 сравнения независимо от хранящейся в запоминающем элементе информации, а это соответствует сигналу совпадения при поиске. Таким образом, предлагаемое техническое решение позволяет получить ассоциативный запоминающий элемент с минимальным количеством МДП-транзисторов,что дает возможность сократить площадь ассоциативного накопителя при реализации ассоциативного запоминающего устройства на 1адп БКС. Формула изобретения Элемент памяти, содержащий адрес.ный транз.истор, исток которого соединен с информационной шиной, затвор адресного транзистора подключен к адресной шине, транзистор опроса, затвор которого соединен со стоком адресного транзистора и одной из обкладок первого запоминающего конденсатора, сток транзистора опроса соединен с шиной сравнения, а исток с шиной опроса, другая обкладка запоминающего конденсатора соединена с. шиной управления , подложки адресного транзистора и транзистора опроса подключены к шине нулевого потенциала, отличающий-ся тем, что, с целью расширения области применения элемента, за счет осуществления ассоциативного поиска, в него введен второй запоминающий конденсатор, одна из обкладок которого соединена со стоком транзистора опроса, другая обкладка второго запоминающего конденсатора подключена к шине нулевого потенциала. Источники информации, принятые во внимание при экспертизе 1.Заявка ФРГ № 2442131, кл. G 11 С 11/40, 1976. 2.Авторское свидетельство СССР 395.900, кл. G 11 С 11/40, 1971 (прототип).

5 О-о

€

W

| название | год | авторы | номер документа |

|---|---|---|---|

| Полупроводниковая ячейка памяти | 1976 |

|

SU723680A1 |

| Элемент памяти для ассоциативного накопителя | 1976 |

|

SU690565A1 |

| Ячейка памяти | 1977 |

|

SU693437A1 |

| Ассоциативный запоминающийэлЕМЕНТ | 1979 |

|

SU805412A1 |

| Ассоциативная ячейка памяти | 1976 |

|

SU605268A1 |

| Ассоциативный запоминающий элемент на мдп-транзисторах | 1975 |

|

SU542243A1 |

| Устройство для считывания информации из ассоциативного запоминающего блока | 1974 |

|

SU497636A1 |

| Ячейка памяти на мдп-транзисторах | 1975 |

|

SU533988A1 |

| Устройство для считывания информации из блоков памяти | 1977 |

|

SU746718A1 |

| Ячейка памяти с внутренней регенерацией | 1984 |

|

SU1274001A1 |

bS фиг.1

Авторы

Даты

1980-12-15—Публикация

1979-01-03—Подача