1

Изобретение относится к запоминающим устройствам.

Известен ассоциативный запоминающий элемент, выполненный на. МДП-транзисторах статического типа с возможностью маскирования при записи информации f 1 .

Недостаток его в том, что он содержит значительное количество транзксторов.

Наиболее близким .ехническим решением к изобретению является ассоциативный запоминающий элемент,содержащий основной и вспомогательный накопительные конденсаторы, транзистор считывания, транзистор записи запоминающий транзистор, адресный транзистор,шины разрядную, адресную, шШу сравнения, выходной транзистор, ьину опроса словарную, шину опроса разрядную 2.

Недостатком ассоциативного элемента является пониженное быстродействие при операциях ассоциативного поиска вследствие наличия в контуре разряда вспомогательного конденсатора двух последовательно включенных транзисторов и при считывании информации на разрядную шину - трех транзисторов.

Цель изобретения - повышение быстродействия при операциях считывания и ассоциативного поиска.

Поставленная цель достигается тем, что в ассоциативном запоминающем элементе, содержащем адресный и выходной транзисторы и транзисторы записи и подготовки, конденсатор, конденсатор переменной ер-ичости, разoрядную шину, шину подготовки, адресную шину, шину нулевого потенциала, шины сравнения, опроса и записи, причем стоки адресного транзистора и транзистора записи сое5динены с затвором выходного транзйстора, сток которого соединен с шиной сравнения, исток - с шиной опроса, исток транзистора записи соединен с затвором транзистора под0готовки, исток которого подклк ен к шине подготовки, исток адресного транзистора соединен с разрядной шиной, затворы адресного транзистора и транзистора записи подключены со5ответственно к адресной шине и шине записи, конденсатор включен между стоком транзистора записи, и шиной нулевого потенциала, сток транзистора подготовки соединен с затпором

0 выходного транзистора, а коилонг-О

тор переменной емкости включен между истоком выходного транзистора и затвором транзистора подготовки.

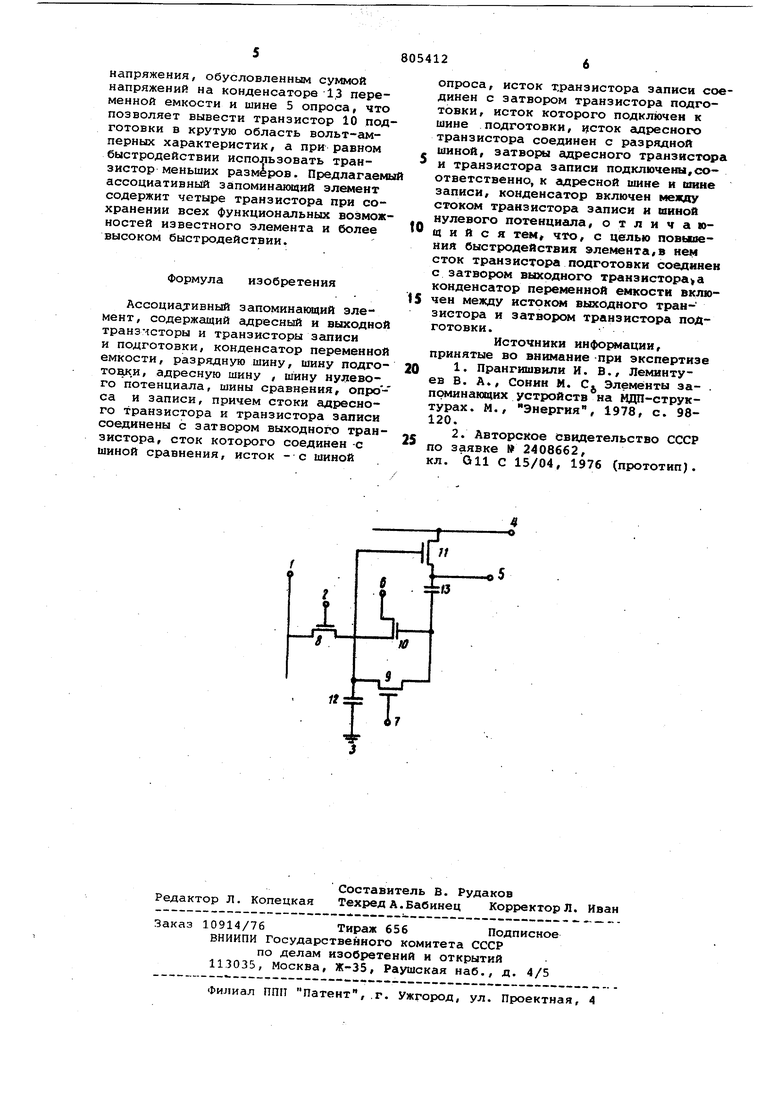

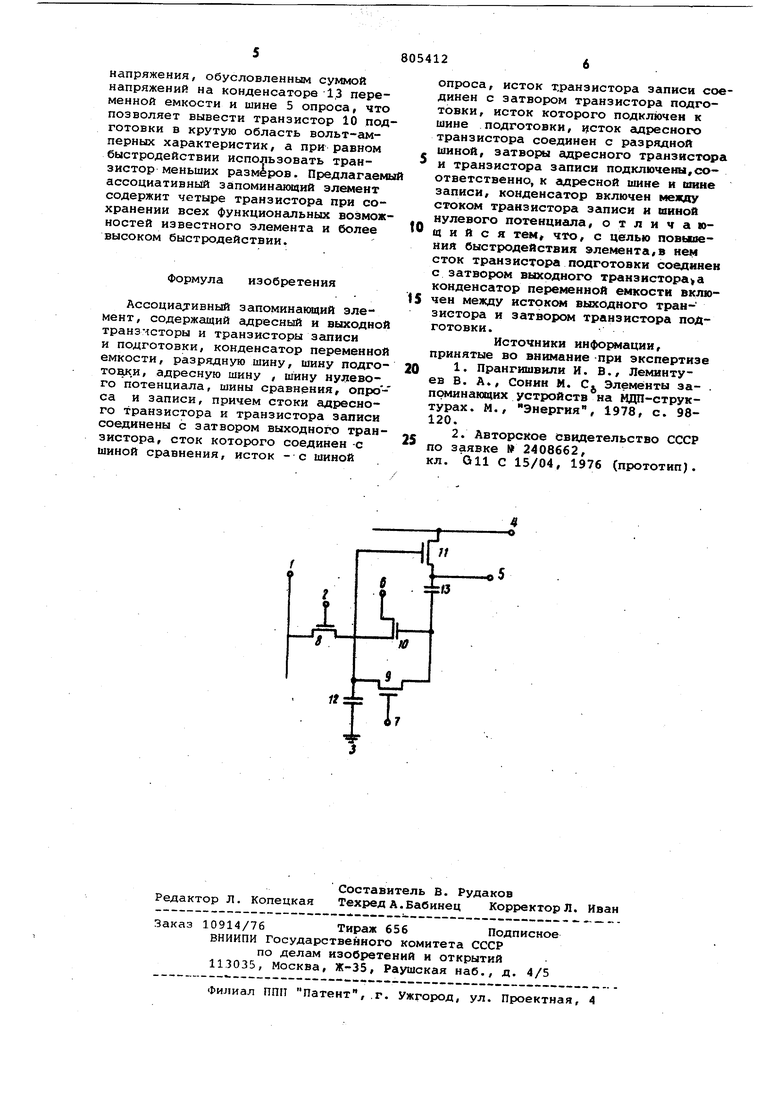

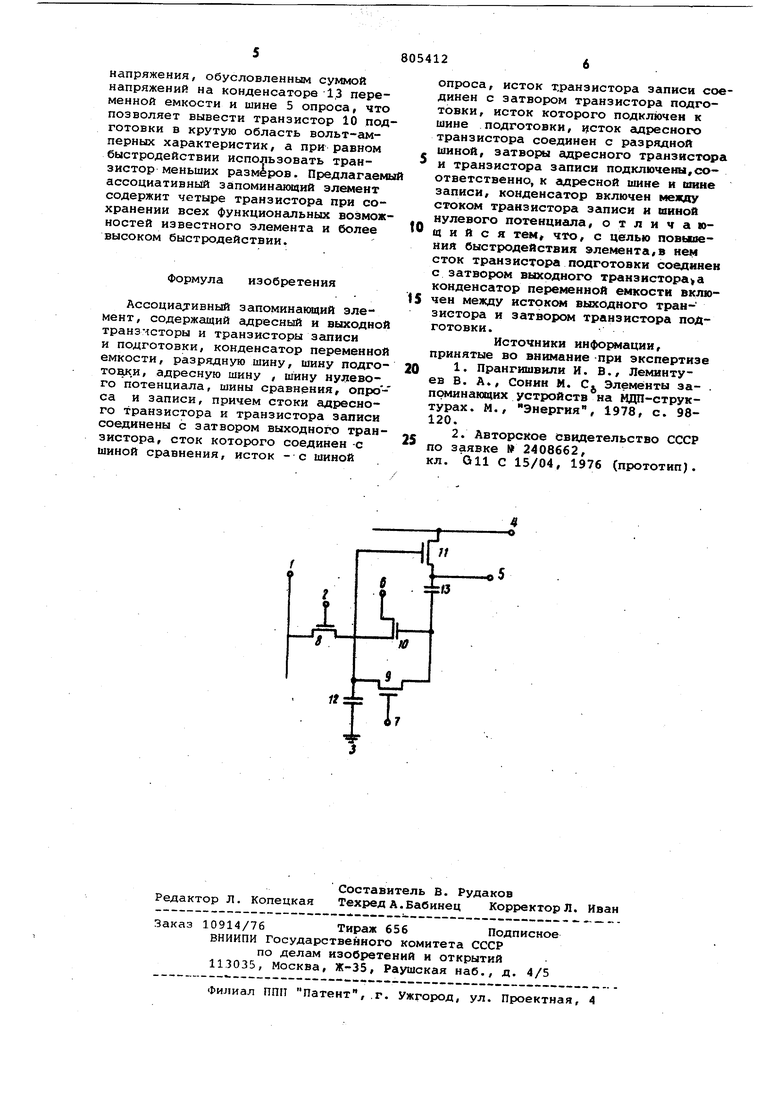

На чертеже изображена принципиальная схема ассоциативного запоминающего элемента.

Элемент содержит разрядную шину 1 адресную шину 2, шину 3 нулевого потенциала, шину 4 сравнения, шину 5 опроса, шину подготовки 6, шину 7 записи, адресный транзистор 8, транзистор 9 записи, транзистор 10 подготовки, выходной транзистор 11, конденсатор 12, конденсатор 13 переменной емкости. В ассоциативном запоми.нающем элементе стоки транзистора 8 адресного и записи 9 соединены с затвором выходного транзистора 11, сток которого соединен с шиной 4 сравнения,исток соединен с шиной 5 опроса. Исток транзистора 9 записи соединен с затвором транзистора 10 подготовки, исток которого соединен с шиной 6 подготовки. Исток адресного транзистора 8 -соединен с разрядной шиной 1, затворы транзисторов адресного 8 и записи 9 соединены, соответственно, с адресной шиной 2 и шиной 7 записи, сток транзистора 10 подготовки соединен с затвором выходного транзистора 11,а конденсатор 13 переменной емкости включен между истоком выходного транзистора 11 и затвором транзистора 10 подготовки.

Элемент работает следующим образом.

В режиме поиска О в первом такте производится предварительный разряд конденсатора 12 через адресный транзистор 8, открытый управляющим сигналом по адресной шине 2 при нулевом потенциале разрядной шины 1 и шкны 6 подготовки и высоком потенциале шины 5 опроса. Во втором такте производится опрос состояния конденсатора 13 переменной емкости подачей импульса по шине 5 опроса и шине б подготовки при закрытом адресном транзисторе 8, и потенциал затвора транзистора 10 подготовки остается нулевым, выходной транзистор -11 закрыт,, обеспечивая отсутствие проводимости мехаду шиной 4 сравнения и шиной 5 опроса, что соответствует совпадению при поиске О.

В случае хранения 1 потенциал затвора выходного транзистора 11 прижимает значение логической 1 вследствие заряда конденсатора 12 импульсом по шине 6 подготовки через открытый по затвору сигналом 1 транзистор 10 подготовки, обеспечива открытое состояние выходного транзистора 11 и наличие проводимости между шинами сравнения и опроса 5, xi-rn соответствует сигналу совпащения

при поиске О. В режиме 1 в первом такте производится предварительный заряд конденсатора 12 через адресный транзистор 8, открытый управляющим сигналом по адресной шине 2 при.высоком потенциале шины 1 и шины б подготовки 5 опроса. Во втором такте потенциалы адресной шины 2 и шины 6 подготовки устанавливаются нулевыми. В случае хранения 1 транзистор 10 подготовки открыт и разряжает конденсатор 12,до потенциала О, обеспечивая закрытое состояние выходного транзистора 11, соответствующее сигналу совпадения при поиске 1.

В случае хранения О разряда конденсатора 12 не происходит, выходной транзистор 11 открыт, что соответствует сигналу несовпадения при поиске 1. Операция маскирования при поиске выполняется аналогично поиску О, но во втором такте потенциал шины б подготовки остается нулевым, что обеспечивает закрытое состояние выходного TpaHSCHToisa 11, соответствующее сигналу совпадения, при поиске независимо от хранимой в запоминающем- элементе информации. В режиме записи потенциал шины 5 опроса устанавливается нулевым и производится подключение конденсатора 13 переменной емкости к шине 1 с потенциалом логического О или 1 через транзистор 8 адресный и транзистор 9 записи, открытые по шинам адресной 2 и записи 7. Для маскирования при записи достаточно подать нулевой потенциал на шину 7 записи.

Считывание информации производитс на разрядную шину 1 и конденсатор 14 через адресный транзистор 8 и транзистор 10 подготовки при высоком потенциале шины 5 опроса и шины бподготовки. Предварительно при нулевом потенциале указанных шин производится разряд конденсатора 12 через адресный транзистор8, если операция считывания предшествовала операции поиска. Внутренняя регенерация обеспечивается подключением к конденсатору 13 переменной емкости конденсатора 12 через открытый транзистор записи при нулевом потенциале шины 5 опроса после считывания информации на конденсатор 12 при закрытом адреоном транзисторе 8.

В предлагаемом ассоциативном запоминающем элементе разряд -и заряд конденсатора 12 в процессе выполнения

60 основных операций происходят с меньшей -постоянной времени, чем в известном, так как контур разряда конденсатора содержит только один транзистор 10 подготовки, который открывается по затвору высоким уровнем напряжения, обусловленным суммой напряжений на конденсаторе 1,3 переменной емкости и шине 5 опроса, что позволяет вывести транзистор 10 под готовки в крутую область вольт-амперных характеристик, а при равном быстродействии использовать транзистор меньших размеров. Предлагаем ассоциативный запоминающий элемент содержит четыре транзистора при сохранении всех функциональных возмож ностей известного элемента и более высоком быстродействии. Формула изобретения Ассоциативный запоминающий элемент, содержащий адресный и выходно транзисторы и транзисторы записи и подготовки, конденсатор переменно емкости, разрядную шину, шину подго товк.и, адресную шину , шину нулевого потенциала, шины сравнения, опро са и записи, причем стоки адресного транзистора и транзистора записи соединены с затвором выходного тран зистора, сток которого соединен -с шиной сравнения, исток - с шиной опроса, исток транзистора записи соединен с затвором транзистора подготовки, исток которого подключен к шине подготовки, исток адресного транзистора соединен с разрядной шиной, затворы адресного транзистора и транзистора записи подключены,соответственно, к адресной шине и шине записи, конденсатор включен между стоком транзистора записи и шиной нулевого потенциала, отличающийся тем, что, с целью повышения быстродействия элемента,в нем сток транзистора подготовки соединен с затвором выходного транзистора а конденсатор переменной емкости включен между истоком выходного транзистора и затвором транзистора подготовки. Источники информации, принятые во внимание -при экспертизе 1.Прангишвили И. В., Леминтуев В. А., Сонии М. С Элементы за- . поминающих устройств на МДП-структурах. М., Энергия, 1978, с. 98120. 2.Авторское свидетельство СССР по заявке № 2408662, кл. G11 С 15/04, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Элемент памяти для ассоциативного накопителя | 1976 |

|

SU690565A1 |

| Полупроводниковая ячейка памяти | 1976 |

|

SU723680A1 |

| Ячейка памяти | 1977 |

|

SU693437A1 |

| Устройство для считывания информации из блоков памяти | 1977 |

|

SU746718A1 |

| Элемент памяти | 1979 |

|

SU788175A1 |

| Ассоциативный запоминающий элемент на мдп-транзисторах | 1975 |

|

SU542243A1 |

| Устройство для считывания информации из ассоциативного запоминающего блока | 1974 |

|

SU497636A1 |

| Ассоциативный запоминающий элемент | 1978 |

|

SU675452A1 |

| Ассоциативная ячейка памяти | 1976 |

|

SU605268A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

Авторы

Даты

1981-02-15—Публикация

1979-04-16—Подача