1

Изобретение относится к контрольно-измерительной технике, в частности к. технике контроля и диагностики логических схем.

Известны промышленные контрольноизмерительные устройства, позволяюдие измерять статические и динамические параметры логических схем 1 Одно из таких устройств содержит преобразователи уровней, блок управления, регистр записи, дешифратор,, коммутационный регистр и управляется от мини ЭВМ. Команды от ЭВМ через преобразрватели уровней поступают на блок, управления, который управляет Коммутационным регистром и обменом информации между ЭВМ и устройством. Данные из ЭВМ поступают в регистр записи и через дешифратор записываются в коммутационный регистр.

Однако контрольно-измерительное устройство данного типа не приспособлено для диагностики неисправностей в логических схемах из-за механических переключателей, через которые подаются напряжения на логические схемы, что в свою очередь не позволяет диагнозироватБ логические схемы с памятью, а кроме того, резко снижает скорость испытаний.

Указанные недостатки устранены в специа.глзированных контроль но-диагностических устройствах, имеющих электронные ключи вместо механических.

Наиболее близким техническим решением к изобретению является система контроля логических схем, содержащая управляющую вы хислитель.нута

0 машину, выход которой через преобразователи уровней сигналов подключен к первому входу первого регистра и входу блока управления, соединенного первым выходом через второй ре5гистр с входом KOMj yTaTopa, а вторым выходом с первым входом блока считывания и вторым входом первого регистра 2 , В этой системе не предусмотрена возможность контроля и диагнос0тики логических схем с неисправностями, вызывающими промежуточный уровень напряжения на выходе испытываемой схемы между логическими О и 1 .При наличии таких нер справнос5тёй система с вероятностью 0,5 не обнаруживает их, сле.довательно, результаты контроля и диагностики получаются недостоверными и неточными.

Цель изобретения - повышение дос0товерности результатов контроля.

Это достигается тем, что система дополнительно содержит дешифратор, блок анализа и блок компараторов, вход которого подключен к выходу коммутатора, а выход - к второму входу блока считывания, соединенного выходом с входом блока анализа, выход которого через преобразователи.уровней сигналов подсоединен к входу уп равляющей вычислительной машины/ причем вход дешифратора подключен к выходу первого регистра, а выход - к одному из входов второго регистра и к третьему входу блока считывания.

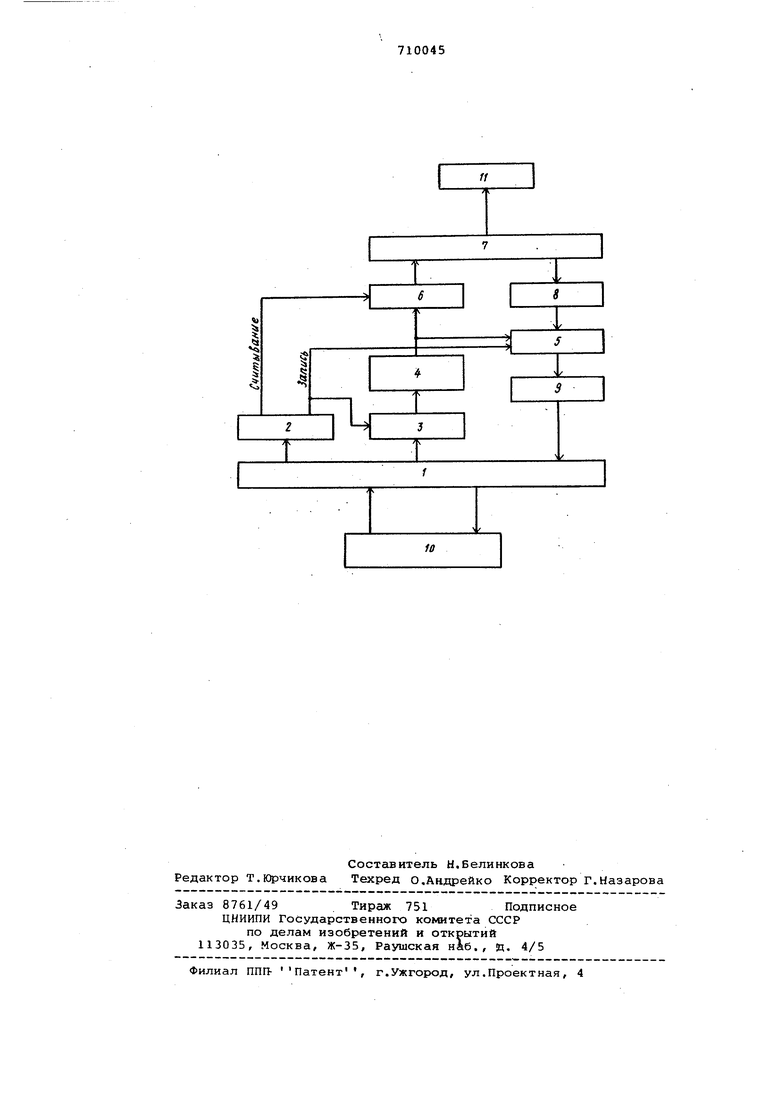

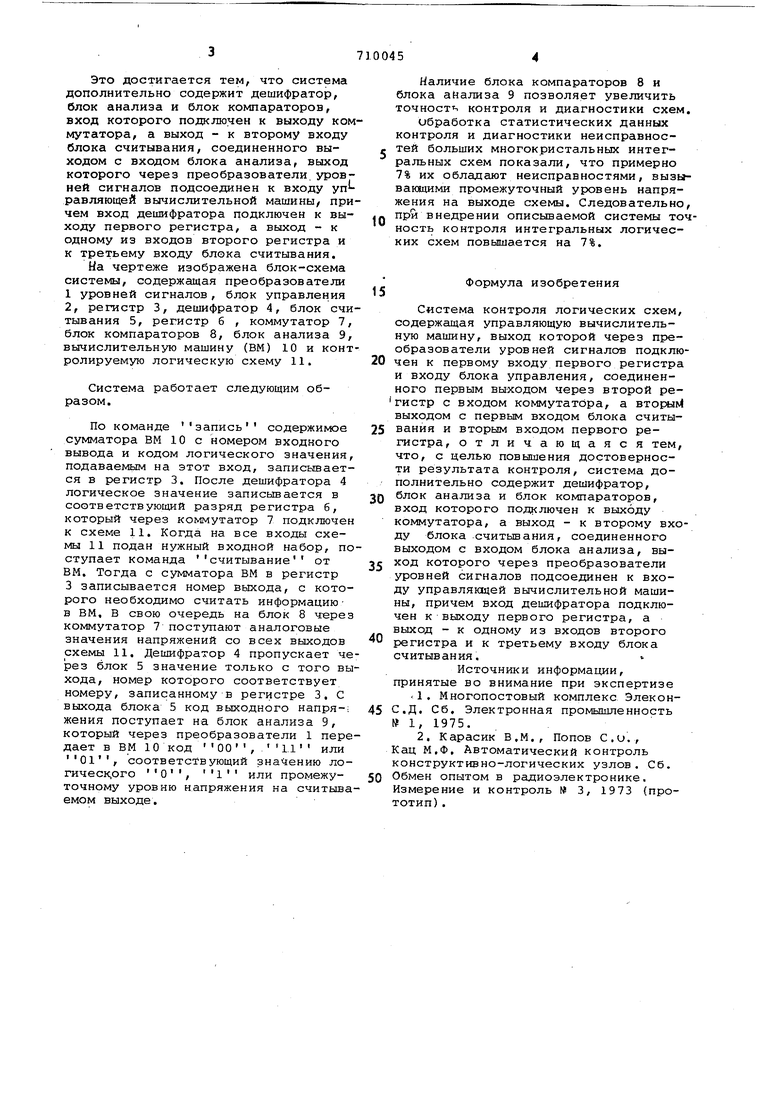

На чертеже изображена блок-схема системы, содержащая преобразователи 1 уровней сигналов, блок управления 2, регистр 3, дешифратор 4, блок считывания 5, регистр 6 , коммутатор 7, блок компараторов 8, блок анализа 9, вычислительную машину (ВМ) 10 и контролируемую логическую схему 11.

Система работает следующим образом.

По команде запись содержимое сумматора ВМ 10 с номером входного вывода и кодом логического значения, подаваемым на этот вход, записьшается в регистр 3. После дешифратора 4 логическое значение записывается в соответствующий разряд регистра 6, который через коммутатор 7 подключен к схеме 11. Когда на все входы схемы 1 1 подан нужный входной набор, поступает команда считывание от ВМ. Тогда с сумматора ВМ в регистр 3 записывается номер выхода, с которого необходимо считать информациюв ВМ. В свою очередь на блок 8 через коммутатор 7 поступают аналоговые значения напряжений со всех выходов схемы 11. Дещифратор 4 пропускает через блок 5 значение только с того выхода, номер которого соответствует номеру, записанному в регистре 3. С выхода блока 5 код выходного напря-: жения поступает на блок анализа 9, который через преобразователи 1 пере00

дает в ВМ 10 код

II

или

01, соответствующий зна 1ению логическ,ого О , ч или промежуточному уровню напряжения на считываемом выходе.

Наличие блока компараторов 8 и блока анализа 9 позволяет увеличить точность контроля и диагностики схем.

обработка статистических данных контроля и диагностики неисправностей больших многокристальных интегральных схем показали, что примерно 7% их обладают неисправностями, вызываняцими промежуточный урювень напряжения на выходе схемы. Следовательно, при внедрении описываемой системы точность контроля интегральных логических схем повышается на 7%.

Формула изобретения

Система контроля логических схем, содержащая управляющую вычислительную машину, выход которой через преобразователи уровней сигналов подключен к первому входу первого регистра и входу блока управления, соединенного первым выходом через второй регистр с входом коммутатора, а вторыМ выходом с первым входом блока считывания и вторым входом первого регистра, отличающаяся тем, что, с целью повышения достоверности результата контроля, система дополнительно содержит дешифратор,

блок анализа и блок компараторов, вход которого подключен к выходу коммутатора, а выход - к второму входу блока считывания, соединенного выходом с входом блока анализа, выход которого через преобразователи уровней сигналов подсоединен к вхоДУ управляквдей вычислительной машины, причем вход дешифратора подключен к выходу первого регистра, а выход - к одному из входов второго

регистра и к третьему входу блока считывания.

Источники информации, принятые во внимание при экспертизе 1. Многопостовый комплекс ЭлеконС.Д. Сб. Электронная промышленность № 1, 1975.

2. Карасик В.М., Попов С.и., Кац М.Ф. Автоматический контроль конструктивно-логических узлов. Сб.

Обмен опытом в радиоэлектронике.

Измерение и контроль № 3, 1973 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух вычислительных машин | 1985 |

|

SU1315987A1 |

| Устройство для диагностики логических блоков | 1983 |

|

SU1095182A1 |

| Устройство для диагностики блоков электронных вычислительных машин | 1978 |

|

SU746556A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1980 |

|

SU907556A1 |

| Устройство для сопряжения с ЭВМ | 1981 |

|

SU1053095A1 |

| Устройство для сопряжения разнотипных вычислительных машин | 1984 |

|

SU1257651A1 |

| Система для контроля и диагностики цифровых узлов | 1980 |

|

SU911531A1 |

| Устройство для контроля логических схем | 1981 |

|

SU1013956A2 |

| УСТРОЙСТВО ДЛЯ СЪЕМА, РЕГИСТРАЦИИ И АНАЛИЗА ЭЛЕКТРОФИЗИОЛОГИЧЕСКИХ СИГНАЛОВ И БЛОК ЗАЩИТЫ ОТ АВАРИЙНЫХ ТОКОВ ПАЦИЕНТА | 1995 |

|

RU2102004C1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

Авторы

Даты

1980-01-15—Публикация

1977-10-26—Подача