(54)- УСТРОЙСТВО ДЛЯ ДИАГНОСТИКИ БЛОКОВ ЭЛЕКТРОННЫХ ВЫЧИСЛИТЕЛЬНЫХ МА1ШН

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU947863A1 |

| Устройство для диагностики блоков электронных вычислительных машин | 1976 |

|

SU650080A1 |

| Устройство для контроля и диагностики цифровых узлов | 1980 |

|

SU896627A1 |

| Устройство для диагностики логических блоков | 1983 |

|

SU1095182A1 |

| Устройство для диагностики логических блоков | 1988 |

|

SU1672452A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Устройство для контроля блоков полупроводниковой памяти | 1979 |

|

SU875469A2 |

| Устройство для диагностики двухмашинного вычислительного комплекса | 1980 |

|

SU959086A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

1

Изобретение относится к вычислительной технике и может быть использовано для обнаружения и локализации неисправностей электронных вычислительных машин (ЭВМ).

Известно устройство для диагностики ЭВМ, содержащее накопитель диагностических тестов, входной регистр, блок управления, преобразователь параллельного кода в последовательный, регистр обмена,блок сравнения, буферный блок памяти l . Это устройство не обеспечивает локализации неисправности сточностью до ИС.

Наиболее близким техническим решением к изобретению является устройство для диагностики блоков электронных вычислительных машин,содержащее последовательно соединенные накопитель тестов, выходной регистр и буферный блок памяти, управляющий вход которого и управляющие входы выходного регистра, регистра тестов, входного регистра и регистра резуль-тата подключены соответственно к первому, второму, третьему, четвертому и пятому выходам блока управления, соединенного входом с выходом накопителя тестов, а выход регистра

2

результата подключен к одному из информационных входов выходного регистра 2 .

Это устройство является сложным, что определяется большим объемом хранимой в накопителе тестовой информации: кроме самих тестовых наборов в накопителе хранятся коды операций опроса выходов проверйе10ого блока, операций сравнения с эталоном, эталонная и другая служебная информация, занимающие примерно 50% объема накопителя.Остальные 50% объема занимают сами тесто15вые наборы. При большом количестве блоков ЭВМ высокой производительности объем накопителя уже может стать фактором, затрудняющим использование устройства.

2(1

Целью изобретения является упрощение устройства за счет сокращения объема тестовой информации, записанной на магнитном носителе.

Это достигается тем. что в уст25ройство введены блок контроля и регистр контрольного кода, информационный вход которого соединен с выходом входного регистра, выход через блок преобразователей кода с 30 информационным входом блока контроля, a управляющий вход - с шестым выходом блока управления, седьмой выход которого подключен к управляющему входу блока контроля,соединенного выходом с информационным входом регистра результата, а также тем, что блок преобразователей кода содержит преобразователи кода, первые входы которых являются первыми входами блока, и преобразователь контрольного кода, первые входы которого являются вторыми входами блока, причем выходы преобразователей кода и контрольного кода являются.выходами блока, а вфорые входы подсоединены к выходу дешифратора, подключенного входом через счетчик к выходу генератора импульсов, и тем , что блок контроля содержит последовательно соединенные сумматор по модулю два входы которого являются информационным входом блока, vf триггер, синхронизирующий вход которого является управляющим входом блока.

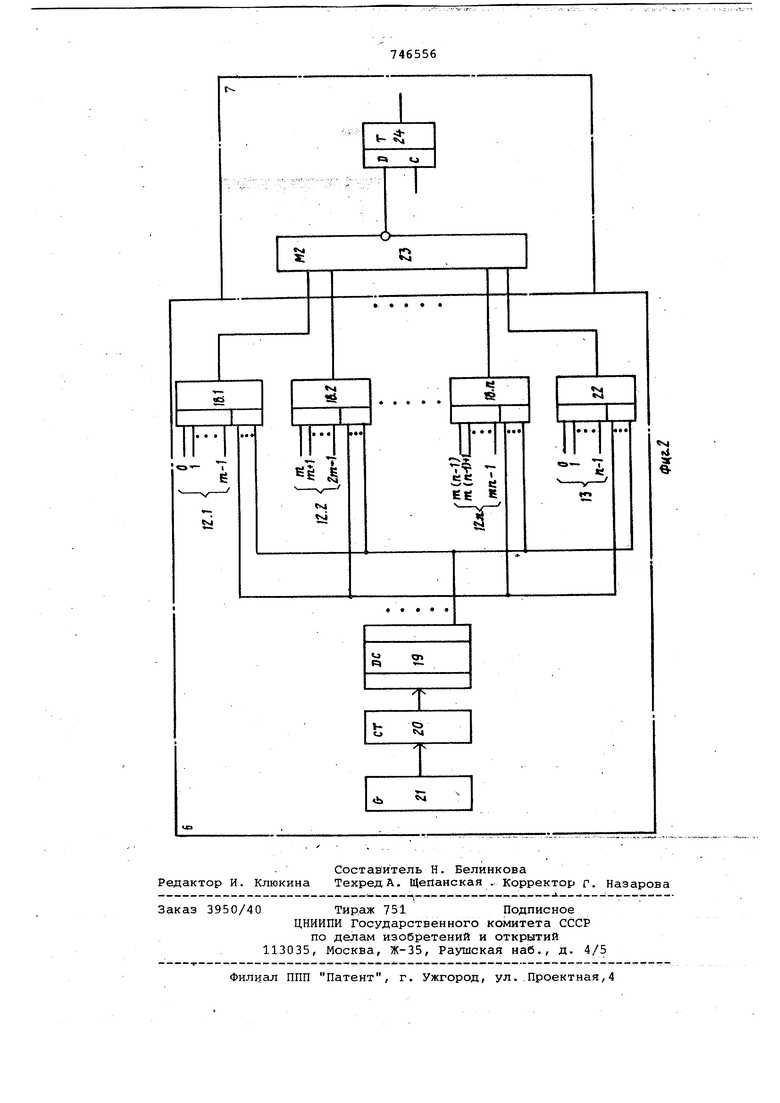

На фиг. 1 изображена структурная схема устройства; на фиг.2 - схемы блока .преобразователей кода и блока контроля. ;

Устройство включает накопитель 1 тестов, входной регистр 2, блок 3 управления, регистр 4 тестов, регистр 5 контрольного кода, блок 6 преобразователей кода, блок 7 контроля, регистр 8 результата, выходной регистр 9, буферный блой 10 па1мяти .и диагностируемый блок 11, входы 12Н-12.П и 13 и выходы 14 и 15 блока 6, входы 16 и 17 регистра 9.

В состав блока 6 (см.фиг.2) входят преобразователи 18.1-l8.nкода, включающие m рязрядов (от О до т-1). Управляющие входы преобразователей IS.l-lS.n соединены с выходами дешифратора 19, входами соединенного с выходами счетчика 20, входы которого соединены с выхоами генератора 21 импульсов. В блок 6 также входит преобразователь 22 онтрольного кода, а в блок 7 - сумматор 23 по модулю два и триггер 24.. .

Работу устройства можно свести к выполнению следующей послвдовательности операций:

. установка регистра 4 из накопителя 1 для подачи входных тестоых последовательностей на блок 11 огласно программе контроля; установка в регистре 5 соответствующего жидаемой на выходе регистра 4 инормации, анализ в блоке 7 инфорации с выхода регистров 4 и 5; наопление результата, полученного а множестве тестов, в блоке 10; пределение неисправных интегральНих схем ПО ецравоЧНйвгУ в сбЬТвбТтвии с полученным кодом; переход к ледующему циклу диагностики, т.е.

746556

подтверждение правильности локализации неисправности путем останова процесса диагностики на первом тесте обнаружившем неисправность, и уточнение локализации с помощью специального индикаторного щупа и справочника эталонных значений в схеме диагностируемого блока.

При подключении выводов диагностируемого блока 11 к разъему устройства и запуска данные из накопителя 1 через регистр 2 поступают в регистр 4, в результате на входе блока 11 устанавливается необходимая тестовая последовательность, после чего согласно программе контроля из накопителя 1 в регистре 5 устанавливается контрольный код ожидаемой на выходе регистра 4 информации. Анализ правильности состояния блока 11 для данного тестового набора осуществляется в блоке 7, точнее,схемой сложения по модулю К.

Для пояснения сущности процесса анализа результатов рассмотрим работу схемы, приведенной на фиг.2,где в схеме контроля использован сумматор 23. В момент времени О,определяемый состоянием О счетчика 20, на выходы преобразователей 1В.118.п поступают значения битов О,т, 2m...m(n-l)+1 регистра 4, а на выходе преобразователя 22 - значение нулевого разряда контрольного кода из регистра 5, Таким образом, на вход сумматора 23 в момент времени О поступает информация вместе с контрольным битом, сумма которых по модулю два на выходе равна нулю при отсутствии неисправностей в .блоке 11. Единичное значение выхода сумматора 23 свидетельствует о наличии ошибки в диагностируемом блоке. Аналогично, в момент времени 1, определяемый состоянием 1 счетчика 20, на выходы преобразователей 18.1-18.п поступают значения битов 1,т+1,2т+1...m(п-1)+1 регистра 4, а на выход преобразователя 22 - значение первого разряда контрольного кода из регистра 5. Вышесказанное относится также к остальным битам информации на выхода преобразователей 18.д-18.п и контрольным битам на выходе преобразователя 22. состояние сумматора 23 фиксируется триггером 24 и передается в регистр 8 результата, который может работать в двух режимах: сдвигателя и счетчика..

При синтезе тестов для блоков и устройств методов активизации одномерного пути обычно активизируется один выход блока. Все остальные принимают безразличное состояние.

В предложенном устройстве все выходьа блока, имекщие безразличное состояние, маскируются благодаря установке в нулевое состояние соответствующих нм выходов регистра 4, В результате этого изменение выходного сигнала, проверяемого на конкретном входном наборе, приводит к изменению четности сигналов в группе, что и обнаруживает схема контроля. .

В режиме сдвигателя состояние триггера 24 по управляющему сигналу поступающему из блока 3, сдвигается вправо. После заполнения регистр 8 его содержимое записывается в блок 10 как составная часть кода неисправности. Этот процесс продолжается до полного формирования кода нисправности, после чего происходит останов устройства. По окончании проверки под неисправности считывается из блока 10 и по диагностическому справочнику определяются неисправности ИС.

Для подтверждения правильности локализации неисправности путем останова процесса диагностики на .первом тесте, обнаружившем неисправность, регистр 8 переводится в режим счетчика считывания по сигналу управления из блока 3 и повторном пуске производит считывание количества тестовых последовательностей до останова устройства. Номер теста .определяет входной набор и эталонную информацию в диагностируемом блоке, приведенную в справочнике.

Отсутствие специального коммутатора для управления подачей тестовой информации на выводы испытуемог блока обусловлено использованием в данном устройстве диагностики нового способа проверки логических устройств на ЭСЛ-схемах, при которо на выходные контакты испытуемых cxe блока 11, которые образуют с выходами соответствующих им разрядов регистра 4 монтажные элементы И,подается низкий логический уровень (логическая единица) при помощи тестовой информации, записанной на магнитномносителе.

При предлагаемой организации устройства для контроля блоков на ЭВМ примерно на 50% сокращается объем накопителя тестов, несколько упрощается структурная схема устройства за счет исключения блока сравнения и его связей.

Формула изобретения,

машин, содержащее последовательно соединенные йайопитёлЁ тестов , вхбд - ной регистр, регистр тестов, блок преобразователей кода, выходной регистр и буферный блок памяти,управляющий вход которого и управляющие щсоды выходного регистра,регистра тестов, входного регистра и регистра результата подключены соответственно к первому, второму, третьему, четвертому и пятому выходам блока управления, соединенного входом с выходом накопителя тестов, а выход регистра результата подключен к одному из информационных входов выХоднбгЬ рГегист15С в тл й-

5 чающееся тем, что, с целью упрощения устройства, введены блок контроля и регистр контрольного кода, информационный вход которого соединен с выходом входного

б регистра, а выход - через блок преобразователей кода с.информационным входомблока контроля, а управляющий вход - с шестым выходом блока управления, седьмой выход которого

5 подключен к управляющемувходу блока контроля, соединенного выходом с информационным входом регистра результата. .

первые входы которого являются вторыми входами блока, причем выходы преобразователей кода и контрольного кода являются выходами блока, а вторые входы подсоединенык выходу дешифратора, подключенного входом через счетчик к выходу генератора импульсов .

Источники информации, принятые во внимание при экспертизе

по заявке № 2406048/18-24, кл. G Об F 15/46, 1976.

746556

ar

1C

S

vby

1 ib

к

Авторы

Даты

1980-07-05—Публикация

1978-02-22—Подача