первого дешифратора соединен с третьим входом второго коммутатора, пятый выход блока синхронизации соединен с входом делителя частоты, первый выход которого через распределитель соединен с входом второго узла элементов ИЛИ, второй и третий выходы делителя частоты соединены с вторым входом второго регистра и третьим входом третьего коммутатора, выходы которого соединены с входами второго и третьего элементов И и третьего счетчика, третий выход второго дешифратора соединен с входом второго компаратора и через второй элемент И - с входом четвертого коммутатора, первый выход котррого через второй компаратор соединен с первым выходом устройства, четвертый

выход второго дешифратора через третий счетчик соединен с вторым входом второй памяти и вторым входом второго дешифратора, пятый выход которого соединен с вторым входом блока ввода, третий выход которого соединен с первым входом триггера, выход которого соединен с третьим входом второй памяти и через третий элемент И - с четвертым входом второй памяти, выход которой соединен с входом третьего компаратора, второй выход четвертого коммутатора через третий компаратор соединен с вторым выходом устройства, шестой выход второго дешифратора соединен с вторым входом триггера, выход второй памяти соединен с третьим входом блока сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессорное устройство для моделирования систем массового обслуживания | 1984 |

|

SU1196886A1 |

| Микропрограммное устройство формирования тестовой последовательности | 1984 |

|

SU1267425A1 |

| Устройство для ввода и вывода динамически изменяющейся информации | 1982 |

|

SU1115043A1 |

| Устройство для регистрации однократныхпРОцЕССОВ | 1978 |

|

SU842936A1 |

| Генератор случайных процессов | 1979 |

|

SU849464A2 |

| Устройство для регистрации режимов работы двигателя | 1983 |

|

SU1117670A1 |

| Устройство для управления тепловым процессом вулканизации изделий | 1989 |

|

SU1647538A1 |

| Устройство таймеров | 1983 |

|

SU1163309A1 |

| Устройство для сопряжения управляющей вычислительной машины с периферийными устройствами | 1983 |

|

SU1201841A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ТЕЛЕФОННЫМИ ЛИНИЯМИ СВЯЗИ | 1992 |

|

RU2006927C1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ СХЕМ, содержащее первый регистр, первый входкоторого соединен с первым входом устройства, второй вход которого соединен с первым входом блока синхронизации, второй вход которого соединен с выходом генератора тактовых импульсов, третий вход устройства соединен с первым входом блока ввода, первый выход блока синхронизации соединен с вторым входом первого регистра, выход которого соединен с первым входом первой памяти, выход которой соединен с входом первого коммутатора, первый выход которого через, преобразователь параллельного кода в последовательный соединен с первым -входом генератора знаков, второй выход первого коммутатора соединен с первым входом блока формирования временной диаграммы, выход которого соединен с первым входом второго коммутатора, регистр режима, выход которого соединен с первым входом первого дешифратора, второй вход которого через блок задержки соединен с вторым выходом блока синхронизации, третий выход которого соединен с первым входом первого счетчика, второй вход которого и первый вход первого элемен-та ИЛИ соединены .с первым выходом перв.ого дешифратора, второй выход которого соединен с вторым входом первого элемента ИЛИ, .выход которого соединен с вторым входом первой памяти, распределитель, выход которого соединен с вторыми входами генератора знаков и блока выработки временной диаграмкы, третий выход первого дешифратора соединен с первым входом второго дешифратора, первый выход которого соединен с первым входом блока сравнения, второй выход второго дешифратора соединен с первым входом третьего коммутатора, второй вход которого соединен с первым выходом блока ввода, второй выход которого соединен с первым входом второй памяти,- блок индикации, отличающееся . тем, что, с целью повышения коэфW .фициента использования оборудования,, в него введены три компаратора, коммутатор, делитель частоты, два счет-. ,чика, регистр, триггер, два узла 5 элементов ИЛИ, Узел элементов И, три .элемента И, причем, выход первого регистра через первый компаратор соединен с входом блока задержки, .четвертый выход блока синхррниэации и второй выход первого дешифратора через второй счетчик соедиСА нены с входом первого узла элементов ИЛИ, через который выход перво UD го счетчика соединен с третьим входом первой памяти, выход которой соединен с вторым входом блока сравнения, выход которого через первый элемент И соединен с первым входом узла элементов И, выход которого через второй узел элементов ИЛИ соединен с входом блока индикации, выход генератора знаков соединен с вторым входом второго коммутатора, выход которого соединен с первым входом второго регистра, выход которого соедияен с вторым входом узла элементов И, третий выход первого дешифратора соединен с входом первого элемента И, четвертый выход

1

Изобретение относится к вычислительной технике и может быть использовано для поиска неисправностей цифровых вычислительных узлов.

Известно устройство для контроля логических схем, содержащее регистр цифровой компаратор, блок задержки, блоки управления, блок памяти, блок индикации, блок синхронизации, генератор импульсов, преобразователь кодов, блок выработки временной диаграммы, блок выработки знаковой информации 11 3

Недостатком этого устройства является невозможность сравнения эталонных данных с действительными сигналами исследуемого объекта.

Наиболее близким к предлагаемому является устройство, содержащее регистр, блок синхронизации, генератор тактовых импульсов, блок ввода две памяти, три коммутатора, блок формирования временной диаграммы, регистр режимов, два дешифратора, блок задержки, счетчик, элемент ИЛИ, распределитель, блок сравнения, блок индикации, преобразователь кодов,-генератор знаков 2J.

Недостатком известного устройства является то, что оно предназна- . чено для контроля и диагностики только устройства в целом, в его рабочем режиме. Контроль и диагностика отдельных, автономных, типовых элементов замена (ТЭЗ) , узлов и. блоков невозможны без использования дополнительных приборов. Под автономными понимаются ТЭЗ, вынесенные , (отдельные, изолированные) за пределы системы и работающие, только в комплексе с .Другими ТЭЗ. иди

самостоятельно под управлением программного обеспечения, а также .узлы и блоки, которые Конструктивно могут быть отделены от ЭВМ в процессе изготовления, профилактики или ремонта. Кроме того, устройство не позволяет налаживать отдельные готовые узлы и блоки вновь разрабатываемых цифровых схем до тех пор, 0 пока не будут закончены все узлы

и блоки, входящие в разрабатываемое устройство, а также не отлажено его программное обеспечение. Эти недостатки требуют больших затрат времени на поиск неисправностей, а следовательно больших затрат на этапе контроля и диагностики цифровых схем. . о

Целью изобретения является повыQ шение коэффициента использования оборудования.

Для достижения поставленной цели в устройство для контроля логических схем, Содержащее первый 5 регистр, первый вход которого соединен Спервым входом устройства, , второй вход которого соединен с первым входом блока синхронизации, второй вход которого соединен с выходом генератора тактовых импульсов,

третий вход устройства соединен с

первым входом блока ввода, первый выход блока синхронизации соединен с вторым входом первого регистра, выход которого соединён с первым

5 входом первой памяти,.выход которой соединен с входом первого коммутатора, первый выход которого через преобразователь параллельного кода в последовательный соединен с первым входом генератора знаков, второй выход первого коммутатора соединен с первым входом блока формирования временной диаграммы, выход которого соединен с первым входом второго коммутатора, регистр режима, выход которого соединен с первым входом первого дешифратора, второй вход которого через блок эадержки соединен с вторым выходом блока синхронизации, третий выход которого соединен с первым входом первого счетчика, второй вход, которого и первый вход первого элемента ИЛИ -соединены с первым выходом первого дешифратора, второй выход которого соединен с вторым входом первого элемента ИЛИ, выход которого соединен с вторым входом перврй памяти, распределитель, выход которого соединен с вторыми входамигенератора знаков и блока выработки временной диаграмг г, третий выход первого дешифратора соединен с первым входом второго дешифратора, первый выход которого соединен с первым входом блока сравнения, второй выход второго дешифратора соединен с первым входом третьего коммутатора, второй вход которого соединен с первым выходом блока ввода, второй выход которого соединен с первым входом второй памяти, блок индикации, введены три компаратора, коммутатор, делитель частоты, два.счетчика, регистр, триггер, два узла элементов ИЛИ, узел элементов И, три элемента И, причем, выход первого регистра через первый компаратор соединен с входом блока задержки, четвертый выход блока синхронизации и второй выход первого дешифратора .через второй счетчик соединены с входом первого узла элементов ИЛИ, через который выход первого счетчика соединен с третьим входом . памяти, выход которой соединен с вторым входом блока сравнения, выход которого через первый элемент И сое- :динен с первым входом узла элементов И, выход которого через второй узел элементов ИЛИ соединен с входом блокаиндикации, выход генератора знаков соединен с вторым входом второго коммутатора, выход которого соединен с первым входом второго регистра, выход которого соединён с BToptJM входом-У зла элементов И, третий выход первого дешифратора соединен с входом первого элемента И, четвертый выход первого дешифратора соединен с третьим входом второго коммутатора, пятый выход , блока синхронизации соединен с входом делителя частоты, первый выход которого через распределитель сое-; динен с входом второго узла элементов ИЛИ, второй и третий выходы делителя частоты соединены с вторым входом.второго регистра и третьим входом третьего коммутатора, выходы которого соединены с входами второго и третьегоэлементов И и третьего счетчика, третий выход

второго дешифратора соединен с входом второго компаратора и через второй элемент И - с входом четвертого коммутатора, первый выход которого через второй компаратор соединен с первым выходом устройства, четвертый выход второго дешифратора через третий счетчик соединен с вторьм входом второй памяти и вторым входом второго дешифратора, пятый

выход которого соединен с вторым входом блока ввода, третий выход которого соединен с первым входом триггера, выход которого соединен с третьим входом второй памяти и

через третий элемент И - с четвертым входом второй памяти, выход которой соединен с входом третьего компаратора, второй выход четвертого коммутатора через третий ксэмпаратор

соединен с вторым выходом устройства, шестой выход второго дешифратора соединен с вторым входом триггера, выход второй памяти соединен с третьим входом блока сравнения.

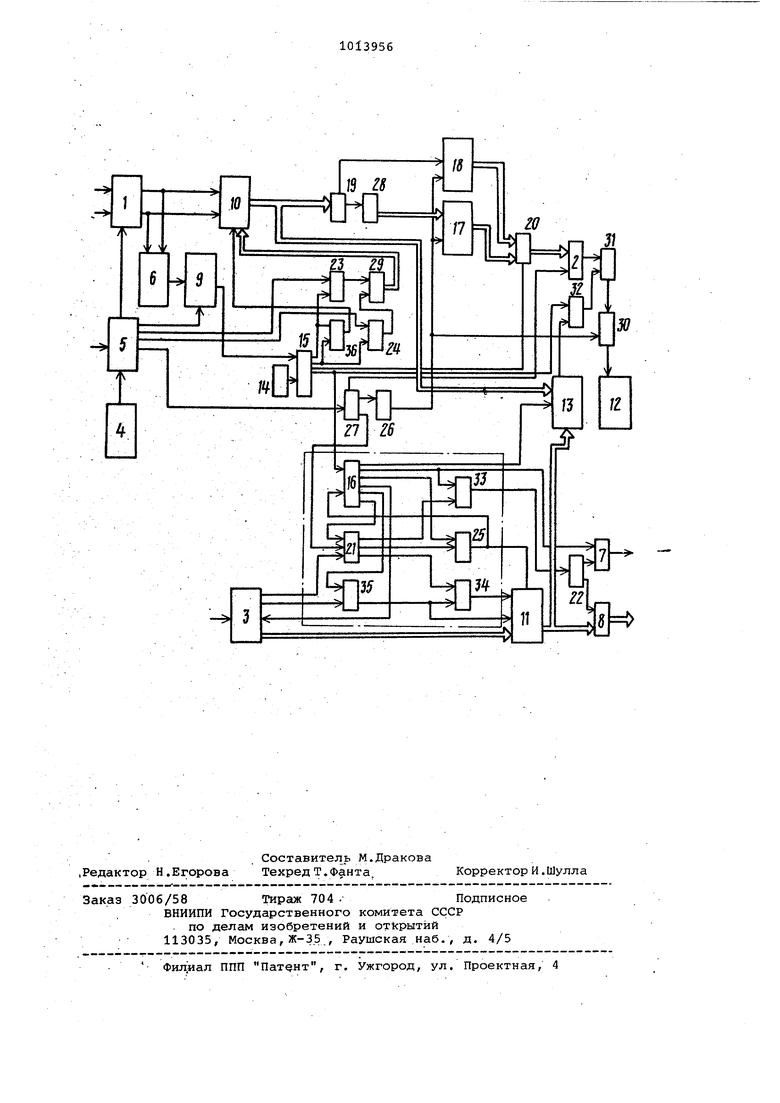

На чертеже приведена структурная схема устройства.

Устройство для контроля логических схем содержит регистры 1 и 2, блок 3 ввода, генератор 4 тактовых импульсов, блок 5 синхронизсщии,

компараторы 6-8, блок 9 задержки, памяти 10 и 11, блок 12 индикации, блок 13 сравнения, регистр 14 режима, дешифраторы 15 и 16, генератор 17 знаков, блок 18 формирования временной диаграммы, коммутаторы 19-22, счетчики 23-25, распределитель 26, делитель 27 частоты, преобразователь 28 параллельного кода в последовательный, ;узлы 29 и ЭХ) элементов ИЛИ, узел 31 элементов 4, элементы И 32-34, триггер 35, элемент ИЛИ 36.

Устройство для контроля логических схем работает в четырех режимах следующим образом.

Первый режим работы - анализ логических состояний.

В этом режиме при каждом постро-. ении синхроимпульса в- первом регистре 1 происходит запоминание логических состояний входов объекта. Набранный на клавиатуре код режима работы устройства запоТиинается в регистре 14. С выхода дешифратора 15 выдается команда Запись информации

с исследуемого объекта, поступающая на входы счетчика 23 и элемента ИЛИ 36, на выходе которого формируется команда Запись. С выхода счетчика 23 через узел 29 адреса записи поступают в память 10, куда

также приходит команда Запись

с элемента ИЛИ 36, и данные регистра 1 переписываются в память 10.

При отладке программ часто возникает необходимость контролировать массив данных в районе какого-либо ключевого слова. В этом случае оператором заносится требуемое слово в компаратор 6. Когда входное слово .из массива входных данных сравнивается с ключевым словом, управление передается через дешифратор 15 в блок 12.таким образом, что если требуется контролировать данные, предшествующие ключевому слову, то происходит прекращение процесса непрерывной записи в память 10 и усройство переходит в режим отображен информации, а если требуется массив данных, последующих ключевому слову, то сигнал из компаратора 6 дает разрешение записи в память 10 до ее заполнения, после чего информаци

отображается. При этом оператор может задержать сбор данных на опреде ленное число периодов синхросигнала В этом случае оператор заносит в

блок 9 требуемую величину задержки. После прихода сигнала сравнения из компаратора 6 в блок 9 за-, пускается счетчик синхроимпульсов (на чертеже не показан), и как только счетчик сосчитает требуемое число импульсов, управление передается дешифратору 15, После заполнения памяти 10 данными начинается процесс обработкиинформации для отображения. При это с дешифратора 15 команда Считывани информации по строкам поступает на счетчик 23 и элемент ИЛИ 36, а команда Считывание информации по столСа ам - на счетчик 24 и элемент ИЛИ 36.1 На элементе ИЛИ 36 формируеся команда Считывание, на выходе узла 29 - адреса считывания. С выходов блока 5 поступают сигналы на счетные входы счетчиков 23 и 24 и на вход делителя .27. Информация, считанная из памяти 10, подается через первый коммутатЬр 19 в преобразователь 28 в форме, удобной для работы блоков 17 и 18,откуда коды подаются на коммутатор 20. С него по команде Выборка временной диаграммы или Выборка знаковой информации , приходящей .с дешифратора 15, коды выдаются на регистр 2. В него же с выхода делителя 27 пода ются частоты.записи или сдвига кодов. Через узел 31 информация поступает на вход узла 30, куда также приходит полный телевизионный сигнал с выхода распределителя 26, что обеспечивает блок 12 всеми сигналами синхронизации, необходимыми для работы телевизионного монитора. С выхода узЛа 30 .ма вход блока 12

подается полный телевизионный сигна с замешанной информацией.

Второй режим работы - анализ логических временных диаграмм.

В этом режиме работы устройство для контроля логических схем синхронизируется не внешними сигналами, а внутренним генератором 4, частота которого выбирается на несколько порядков выше, чем частота, циркулирующая на входных шинах устройства. При каждом импульсе генератора происходит запоминание логических состояний входов в цифровой форме; вначале в регистре 1, а затем - в первой памяти 10, после заполнения которой происходит обработка информации, т.е. преобразование и выдача на монитор для отображения в виде временных диаграмм. Частота генератора выбирается порядка 100 мГц. Это дает возможность измерять временные интервалы с точностью 10 не.

Третий режим работы - генерация входных воздействий.

По поступлении команды Ввод с дешифратора 15 на дешифратор 16 с его выхода на вход блока 3 подается сигнал Ввод, по которому он начинает принимать информацию. . С выхода дешифратора lis на триггер 3 подается сигнал установа,под воздейвием которого триггер 35 взводится и с его выхода на память 16 и элемент И 23 поступает сигнал разрешения записи. С дешифратора 16 на счетчик 25 поступает сигнал разрешении счета. С дешифратора 16 на коммутатор 21 поступает сигнал, по которому он подает частоту синхронизации ввода, поступающую с блока 3 на счетчик 25 и элемент И 34. На каждый этап синхронизации, поступающий синхронно с вводимой информацией , с элемента И 34 выдается сигнал записи,поступающий на память 11, а счетчик 25 вырабатывает следующий адрес, по которому запишется следующая информация, и выдает ее на память 11. По сигналу Конец ввода, поступайщего из блока 3 на триггер 35, он сбрасывается и снмает сигнал разрешения записи. Запись прекращается и память 11 переходит в режим хранения.

Для генерации входных воздействи с дешифратора 15 выдается команда Генерация. С дешифратора 16 выдается команда включения на компарато 7 и на элемент 33. С дешифратора 16 на счетчик 25 вьодается сигнал разрешения счета, а на коммутатор 21 сигнал, под воздействием которого частота генерации, поступающая с делителя 27, подается на элемент И 33 и на счетчик 25. На каждый так частоты генерации с элемента И 33 через коммутатор 22 и компаратор 7 выдается импульс синхронизации навыход устройства, а со счетчика 25 выдается адрес, по которому выбираются -данные из памяти 11. Шестнадцатиразрядные слова воздействий из памяти 11 подаются через компаратор 8 -на выход устройств Для проверки исследуемых объекто на их Еэабочей частоте в устройстве предусмотрена возможность изменения частоты генерации входных воздейстВИЙ путем изменения частоты содержимого памяти. . Четвертый режим работы - режим сравнения. В этом режиме устройст.во для контролялогических схем подключается к источнику тестовой информации и к входам исследуемого- объекта. Тестовая программа указанным способом вводится в память 11. Посл этого с дешифратор а--15 на дешифратор 16 выдается команда Генерация а в память 10 - сигнал 6 записи информации, поступающей от исследуемо го объекта. По команде Генерация начинается генерация последовательностей входных воздействий на иссле дуемый объект. Реакция исследуемого объекта на входные воздействия с контролируемых точек исследуемого объекта заносится в регистр 1, отку переписывается в пгииять 10. После заполнения памяти 10 данными начинается процесс обработки„информации для отображения в режиме сравнения. Информация, считываеная из памяти 1 через коммутатор 19 и преобразовате 28 передается в блок 13 или генератор 14. Информация, считываемая из памяти 10, также передается в блок Для проверки информсщии от иссле дуемого объекта необходимо сравнить ее с эталонными данными, которые вводятся в память 11 аналогично вводу тестовой информации. Дпя того, чтобыобнаружить несовпадение, эталонных данных с фактической реакцией объекта на входные вЬздействия в блоке 13 происходит сравнение содержимого памяти 10 и памяти 11. При считывании эталонных данных с дешифратора 15 по ступает команда Сравнение на дешифратор 16, под воздействием которой подается сигнал на сравнение информации в блок 13. Выдается сигна;; разрешения счета на счетчик 25, коммутатор 21 выдает сигнал, под воздействием которого частота, для синхронного считывания памяти 10 и памяти 11 поступает с делителя 27 на коммутатор 21 и на счетчик 25, который выдает адреса считывания инфорМсщии на память 11. В блоке 13 вырабатывается сигнал несовпадения эталонной информации и записанной с объекта. При сигнале несовпгщения на элементе И 32 производится индикация ошибки -с дешифратора 15, которая подается на узел 31 информация с регистра 2 подается через узел 31 на узел 30 с прерываниями, которые и определяют мерцание ошибочной информации на экране блока 12. Индикация ошибки устраняет необходимость просмотра всей информации, выведенной на экран, что-на 50-60% сокращает время отладки цифровых схем; при этом снижаются требования к квалификации настройщиков. Использование изобретения позволит уменьшить номенклатуру контрольнодиагностической аппаратуры, время на обработку результатов испытаний-, что повышает эффективность использования контролирующей аппаратуры.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля логических схем | 1978 |

|

SU744580A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для анализа информационной последовательности | 1978 |

|

SU746529A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-04-23—Публикация

1981-04-29—Подача