1

Изобретение относится к вычислительной технике и может быть использовано при построении временных коммутационных устройств в универсальных вычислительных системах высокой производительности.

Известны в вычислительных система коммутаторы для последовательной передачи дискретной информации, содержащие элементы сравнения, задающие регистры и регистры для приема и выдачи дискретной информации. Управление передачей и коммутацией двоичных сигналов осуществляется с помощью-двух групп переключат ел ётй, каждая из которых содержит п подгрупп с тремя ключами в каждой, мажоритарного элемента, двух элементов ИЛИ и двух элементов задержки, а также . соответствующих элементов сравнения первые входы каждого из которых подключены к выходам шифратора, а вторые входы - к выходам соответствующего задающего регистратора

Основным недостатком данного устройства является низкое быстродействие, вызванное тем, что при последовательной передаче дискретной информации требуется одновременная коммутация единичных и нулевых сигналов.

С целью повьиаен ия быстродействия в коммутаторе, содержащем п--разр.яд ный приемный регистр, т-разрядный выходной регистр, единичные разрядные входы которого соединены с выходами соответствующих элементов сравнения, первые входы каждого из которых подключены к log sr; выходам шифратора, а вторые входы - к выходам соответствующего задающего регистра, а также два элемента ИЛИ, два элемента задержки, мажоритарный элемент и две группы переключателей, каждая из которых содержит п подгруп с тремя ключами в каждой, i-ый единичный разрядный выход приемного регистра соединен с информационным входом первого ключа i-ой подгруппы первой группы переключателей, информационным входом второго ключа i-ой подгруппы второй группы переключателей и 1-ым входом мажоритарного элемента, а i-ый нулевой разрядный выход приемного регистра подключен -к информационному входу второго ключа 1-ой подгруппы первой группы переключат.елей и информационному входу первого ключа i-ой подгруппы второй группы переключателей. При этом первый выход мажоритарного элемента соединен с управляющими входами ключей первой подгруппы первой группы переключателей, а второй выход - с управляющими входами ключей первой подгруппы второй группы переключателей, в каждой группе переключателей выход первого ключа предыдущей подгруппы соединен с управляющими входами ключей последующей подгруппы, а выходы первых ключей последних подгрупп соединены с входами первого элемента ИЛИ, выходы вторых ключей соотзетствующих подзгрупп переключателей объединены и подключены к соответствующему входу, шифратора. Выходы шифратора соединены с входами второго элемента ИЛИ, выход которого через первый элемент задержки подключен к входам третьих ключей всех подгрупп переключателей, выход третьего ключа i-ой подгруппы первой группы переключателей соединен с i-ым единичным разрядным входом приемного регистра, а выход третьего ключа i-ой подгруппы второй группы переключателей подключен к 1-ому нулевому разрядному входу приемного регистра. Выход первого элемента ИЛИ через второй элемент задержки соединен с входами сброса приемного и выходного регистров, первый управляющий вход последнего из которых подключен к выходу первого ключа последней подгруппы переключателей, а второй упраляющий .вход соединен с выходом первого ключа .последней подгруппы первой группы переключателей.

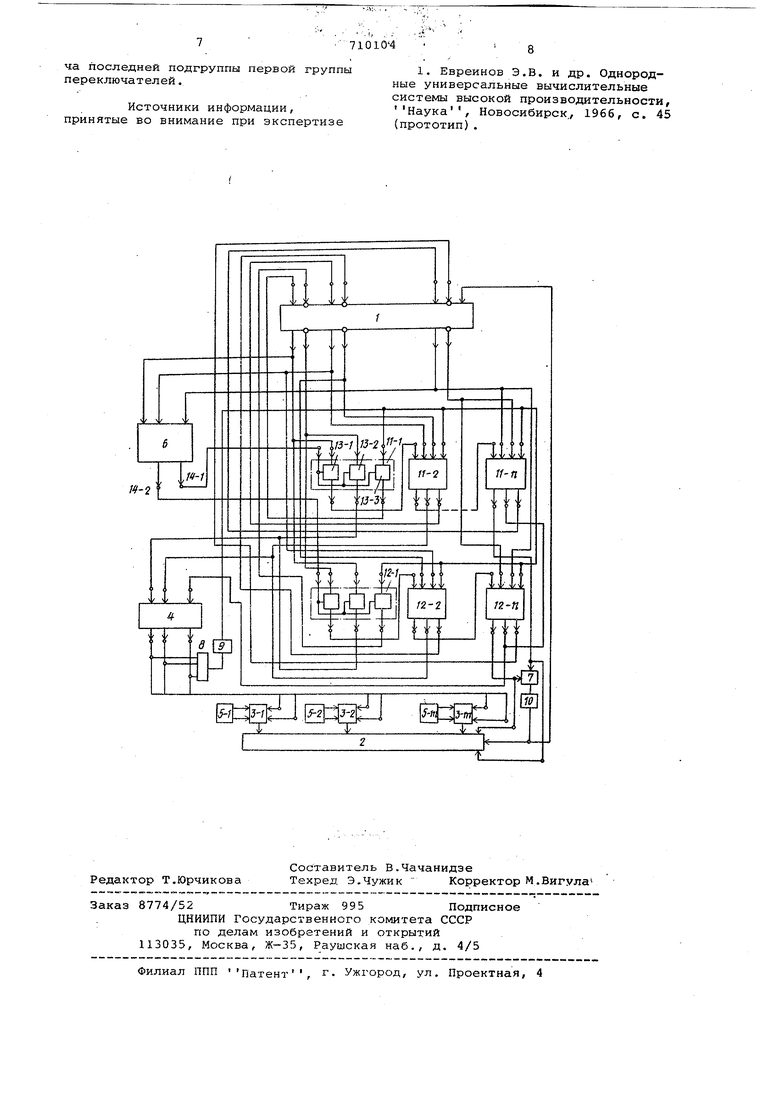

На чертеже представлена функциональная схема, коммутатора.

Коммутатор содержит п-разрядный приемный регистр 1, т-разрядный выходной регистр 2, единичные разрядные входы которого соединены с выходами соответствующих элементов сравнения 3-1-3-т. Первые входы каждого элемента сравнения подключены к Idgjn выходам шифратора 4, а вторые .входы - к выходам соответствующего задающего регистра 5 (на чертеже задающие регистры 5-1-5-т) . Комглутатор содержит также мажоритарный элемент 6, элементы ИЛИ.7 и 8, элементы задержки 9 и 10 и две группы переключателей 11 и 12. Каждая из групп переключателей -содержит Г; подгрупп: и 12-1-12-п„ Е одну подгруппу входят три ключа 13-1-13-3

При передаче информации из приемного регистра 1 в выходкой регистр 2 согласно программе ко.лм тации в задающих регистрах 5-1, 5-2, .. , , , коммутатор работает следующим образо

Записанный в приемном регистре п разрядный код поступает на все входы мажоритарного элемента 6, имеющего порог срабатывания п/2. Если в п-разрядном коде количество единиц больще, чем п/2, то на выходе 14-1 мажоритарного элемента присутствует

потенциал. Он поступает на управляющие входы ключей 13-1, 13-2, 13-3 подгруппы 11-1 группы переключателей 11. Когда в первом разряде приемного регистра записана логическая единица, то открыт в подгруппе 11-1 ключ 13-1, с которого потенциал поступает на вход ключа 13-1 подгруппы 11-2. Если в первом разряде приемного регистра зафиксирован логический нол то потенциал с соответствующего выхода проходит через открытый ключ 13-2 и поступает на первый вход шифратора 4. На выходах шифратора образуется двоичный код 00...01, который соответствует номеру разряда (в данном .случае первому) , хранящему логический ноль. Далее образованный двоичный код поступает на входы элементов сравнения 3-1, 3-2,..., 3-т.

8них происходит сравнение с кодами, записанными в задающих регистрах 5-1, 5-2,..., 5-)т. Когда произойдет совпадение, сигнал с соответствующих элементов сравнения записывается в необходимые разрядаг .выходного регистра 2. Одновременно с этим на выходе элемента ИЛИ 8. появляется потенциал, который через элемент задержки

9и открытый ключ 13-3 подгруппы 11-1 перебрасывает первый разряд приемного регистра 1 в единичнйе состояние. В результате этого в подгруппе 11-1 открывается ключ 13-1 потенциал с которого поступает на управляющие входы ключей подгруппы 11-2. Следовательно, потенциал с выхода 14-1 мажоритарного элемента 6 проходит аналогичным образом через остальные подгруппы (11-2,- 11-3,..., 11-п) группы переключателей 11, причем время затрачивается только на. передачу нулевых значений в разрядах приемного регистра и информация из приемного регистра перезаписывается в выходной регистр в обратном коде.

Потенциал, появившийся в конце передачи на выходе ключа 13-1 подгруппы 11-п, .поступает на второй управляю дий вход выходного регистра 2, По этому сигналу с выходного регистра происходит считывание информации в виде инверсного т-разрядного кода. Сброс в ноль приемного регистра 1 и выходного регистра 2 происходит через элемент задержки 10 сигналом с выхода элемента ИЛИ 7.

Когда в п-разрядном коде приемного регистра количество логических нулей больше, чем единиц, присутствует потенциал на выходе 14-2 мажо-ритарного элемента 6, который поступает на управляю;цие -входы ключей . 13-1, 13-2, 13-3 подгруппы 12-1 группы переключателей 12. Если в первом разряде приемного регистра зафиксирован логический ноль, то потенциал с выхода ключа 13-1 подгруппы 12-1 поступает непосоедственно на управляющие входы ключей 13-1, 13-2, 13подгруппы 12-2 группы переключателей 12. Если в первом разряде приемного регистра зафиксирована логическая единица, то сигнал с единичного вых да данного разряда проходит через открытый ключ 13-2 подгруппы 12-1 и поступает на первый вход шифратор 4. На выходах шифратора образуется двоичный код 00...01, который соответствует номеру разряда (в данном случае первому), хранящему единицу. Далее образованный двоичный код поступает на входы элементов сравнени 3-1, 3-2,..., 3-т, где происходит сравнение с кодами, записанными в задающих регистрах 5-1, 5-2,...,5-т В случае совпадения с выходов соответствующих элементов сравнения появляется сигнал, который записывает ,ся в соответствующие разряды выходн го регистра 2. Одновременно с этим на выходе элеьзнта ИЛИ 8 появляется потенциал, который через элемент задержки 9 и открытый ключ 13-3 под группы 12-1 группы переключателей 1 перебрасывает первый разряд приемно го регистра 1 в нулевое состояние. с этого момента сигнал через откр вающийся ключ 13-1 подгруппы 12-1 группы переключателей 12 поступает на управляющие входы ключей 13-1, 13-2, 13-3 подгруппы 12-2. Потенциал с выхода 14-2 мажоритарного элемента 6 аналогично проходит через остал ные подгруппы (12-2, 12-3,...,12-п) группы переключателей 12. При этом время затрачивается только на передачу логических единиц, хранимых в приемном регистре 1. Причем информация из приемного регистра перезаписывается на выходной регистр 2 согласно программе коммутации в прямом коде. В конце передачи сигнал на выходе ключа 13-1 подгруппы 12-п группы переключателей 12 поступает на первый управляющий вход выходного регистра. По этому потенциалу с выходного регистра происходит считывание информации в виде прямого т-разрядного кода. Сброс в ноль приемного регистра 1 и выходного регистра 2 осуществ ляется этим же сигналом с выхода элемента ИЛИ 7 через элемент задержки 10.. Когда в п-разрядном коде приемного регистра число нулей и единиц оди наково, на любом из выходов (14-1 и 14-2) мажоритарного элемента б может присутствовать потенциал. В этом случае время передачи информации в коммутаторе максимально и равно п/2 тактам. Формула изобретения Коммутатор, содержащий п-разрядный приемный регистр, га-разрядный выходн-ой регистр, единичные разрядные входы которого соединены с выходами соответствующих элементов сравнения, первые входы каждого из которых подключены к Iog2m выходам шифратора, а вторые входы - к выходам соответствующего задающего регистра/ а также два элемента ИЛИ, два элемента задержки, мажоритарный элемент и две группы, переключателей, каждая из которых содержит п подгрупп с тремя ключами в каждой, отличающийся тем, что, с целью повышения быстродействия, i-ый единичный разрядный выход приемного регистра соединен с информационным входом первого ключа i-ой подгруппы первой группы переключателей, информационным входом второго ключа i-ой подгруппы второй группы переключателей и 1-ым входом мажоритарного элемента, а нулевой разрядный выход приемного регистра подключен к информационному входу второго ключа i-ой подгруппы первой группы переключателей и информационному входу первого ключа i-ой подгруппы, второй группы переключателей, первый выхол мажоритарного элемента соединен с управляющими входами ключей первой подгруппы первой группы переключате-лей, а второй выход - с управляющими входами ключей первой подгруппы второй группы переключателей, Б каждой, группе переключателей выход первогс: ключа пседыдущей подгруппы соединен с управляющими входами ключей последующей подгруппы, а выходы первых ключей последних подгрупп соединены с входами первого элемента ИЛИ, выходы вторых ключей соответствующих подгрупп переключателей объединены и подключены к соответствующему входу шифратора, выходы которого соединены с входами второго элемента ИЛИ, выход которого через первый элемент задержки подключен к входам третьих ключей всех подгрупп переключателей, выход третьего ключа i-ой подгруппы первой группы переключателей соединен с i-ым единичным разрядным входом приемного регистра, а выход третьего ключа i-ой подгруппы второй группы переключателей подключен к i-oMy нулевому разрядному. входу приемного регистра, выход первого элемента ИЛИ через второй элемент задержки соединен с входами, сброса приемного и выходного регистров, первый управляющий вход последнего из которых подключен к выходу первого ключа последней подгруппы переключателей, а второй управляюгдий вход соехмнен с выходом первого ключа последней подгруппы первой группы переключателей.

Источники информации, принятые во внимание при экспертизе

1. Евреинов Э.В. и др. Однородные универсальные вычислительные системы высокой производительности, Наука, Новосибирск,, 1966, с. 45 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ | 1991 |

|

RU2037964C1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| Устройство для сортировки двоичных чисел | 1982 |

|

SU1049900A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| Конвейерный аналого-цифровой преобразователь | 1986 |

|

SU1381706A1 |

| Устройство для мажоритарного резервирования | 1983 |

|

SU1140278A1 |

| Кодирующее устройство | 1987 |

|

SU1481899A1 |

| Устройство ассоциативного кодирования и объемного сжатия информации | 1987 |

|

SU1441484A1 |

| Устройство для определения кратчайшего пути на графе | 1983 |

|

SU1134944A1 |

| ЦИФРОВАЯ СИСТЕМА РАДИОВЕЩАНИЯ | 2011 |

|

RU2457620C1 |

W-2

Авторы

Даты

1980-01-15—Публикация

1977-01-06—Подача