(54) ЦИФРОВОЙ ГЕНЕРАТОР ФУНКЦИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой генератор функций | 1976 |

|

SU736079A1 |

| Цифровое устройство для воспроизве-дЕНия фуНКций | 1979 |

|

SU809126A1 |

| Множительное устройство | 1978 |

|

SU824206A1 |

| Цифровой генератор функций | 1978 |

|

SU750467A1 |

| Цифровой генератор функций | 1984 |

|

SU1168921A1 |

| Цифровой генератор гармонических функций | 1983 |

|

SU1224802A1 |

| Устройство для вычисления функций двух переменных | 1983 |

|

SU1123034A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Цифровой преобразователь координат | 1980 |

|

SU942004A1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

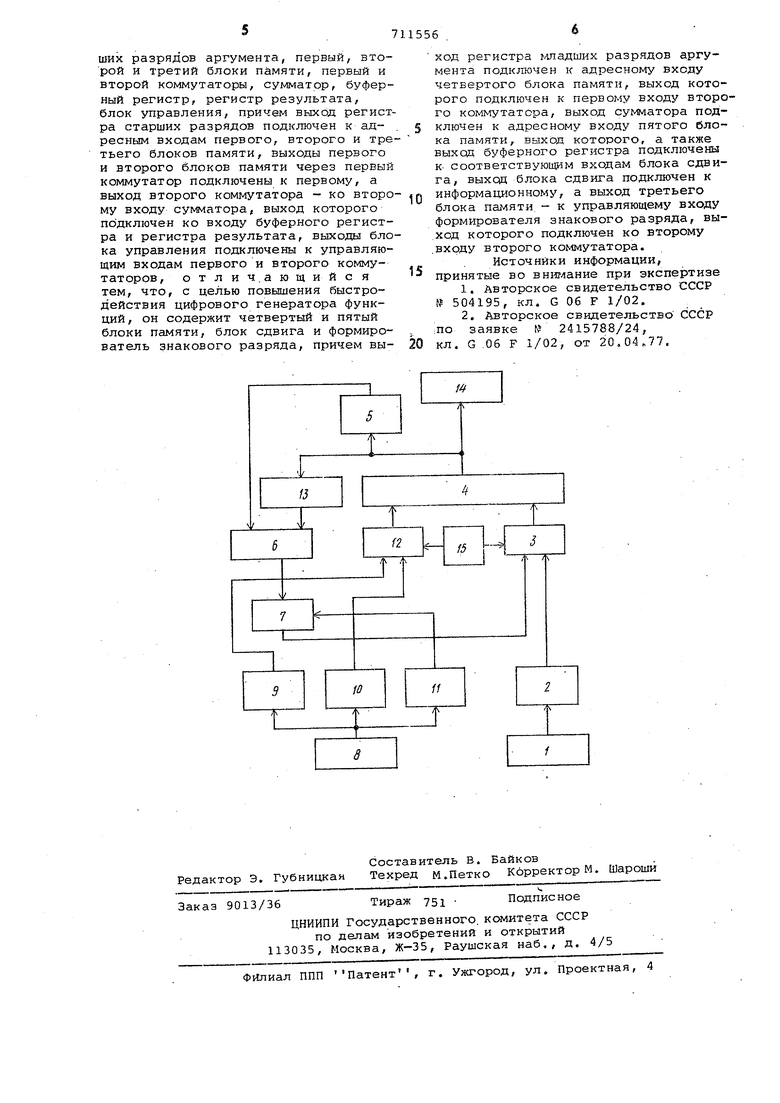

1 Изобретение относится к области автоматики и вычислительной техники и может быть использовано для аппаратурной реализации ангшитических функций в специализированных и универсальных быстродействующих цифровых вычислительных машинах. Известен цифровой генератор функ ций, содержащий регистры, блоки постоянного запоминающего устройства (ПЗУ), коммутатор и сумматор 1. Наиболее близким техническим решением к данному предложенному является цифровой генератор функций, содержащий регистр младших и регистр старших разрядов аргумента,, первый второй и третий блоки памяти, первый и второй ксяУ1мутаторы, сумматор, буферный регистр, регистр результата, блок управления, причем выход регист ра старших разрядов подключен к адресным входам первого, второго и третьего блоков памяти, выходы перво го и второго блоков памяти через пер вый коммутатор подключены к первому. а выход второго коммутатора - ко вто рому входу сумматора, выход которого подключен ко входу буферного регистра и регистра результата, выходы блока управления подключены к управляю1дам входам первого и второго коммутаторов 2 . Яедостатксм известных генераторов функций является низкое быстродействие. Целью изобретения является повышение быстродействия цифрового генератора функций. Поставленная цель достигается тем, что цифровой генератор функций содержит четвертый и пятый блоки памя- ти, блок сдвига и формирователь знакового разряда, причем выход регистра младших разрядов аргумента подключен к адресному входу четвертого блока памяти, выход которого подключен к первому входу второго коммутатора, выход сумматора подключен к Адресному вхсяу пятого блока памяти, (выхбд которого,а также выход буферного регистра подключены к соответствующим входам блока сдвига, выход блока сдвига подключен к инЛормационному, а выход третьего блока памяти-к управляющему входу формирователя знакового разряда, выход которого подключен ко второму входу второго котдмутатора. Функциональная схема цифрового генератора функций показана на чер1-e). Он содержит регистр 1 младших разрядоваргумента, блок памяти 2, коммутатор 3, сумматор 4, блок памяти 5, блок сдвига 6, формировател 7 знакового разряда, регистр 8 стар ших разрядов аргумента, блоки памяти 9, iO, 11, коммутатор 12, буферный регистр 13, регистр результата 14, блок управления 15. Блоки памят 2, 5, 9, 10, 11 могут быть реалнзованы в виде ПЗУ. . Вычисление значений функции прои водится на основе следующих соотношений. Для аргумента X обозначим через Кр число, образованное К старшими двоичными разрядами аргумента, где К - некоторый параметр (2 5 ) m - длина двоичного кода числа х. Число Ко представляет собой узловые точки. Число, образованное (т-К)..младшими разрядами аргумента X, обо значим через дХ так, что X Хд +Д Тогда для любой дифференцируемой в рассматриваемой области изменения аргумента X функции f имеет место разложение FCx)--FCXQ4.-) FCXo)(X.oHP. С ) где R - остаточный член. Для многих функций, в частности для функций, имеющих в рассматривае мой области изменения аргумента X ограниченную вторую производную, мо но найтрг такое значение параметра К для данной конкретной функции F, чт соответствующее ему значение остато ного члена R в (1) не превосходит половину величины младшего разряда формата чисел, используемых .в устройстве. При этом значении параметр коказывается возможным вычислять значения требуемой функции по форму ле FU-HK.o-) + .f(Xo), (eog-./iX-vtog- / F 4Xo HxV-FUoHsig-n СрСХо -)- ,) где функция Sign определяется условием1, если Z О Sign ,(2) О, если 2 0. - 1, если Z О. Вычисления по формуле (3) требуют, хранения пяти таблиц для соответ ствующих значений функций F { XQ) г Sign (FJXo)), tog,AX, Eog f р( 2 и используют лишь операций выборки из таблиц и сложение. Пере численные таблицы заносятся в ПЗУ 11, 2, 10, 5 соответственно. Работа цифрового генератора фун ций -осуществляется следующим образом. В первом такте хранящееся в регистре младших разрядов аргумента значение приращения дХ поступает на вход ПЗУ значений логарифма приращения аргумента 2 и с выхода этого ПЗУ значение логариЛма приращения аргумента Код X . передается через коммутатор 3 на сумматор 4„ Одновременно, в этом же такте, хранящееся в регистре 8 старших разрядов аргумента значение узловой точки Х,-, поступает на входы ПЗУ значения функции в узловой точке 9, ПЗУ значений логарифма модуля производной в узловых точках 10 и ПЗУ знака производной в узловых точках 11, образуя на их выходах, соответственно, значения F(Xo). og, IF (Хо)| и,В1дп (F- (Хо)) . В первом такте коммутатор 12 подключает к сумматору 4 выходы ПЗУ значений логарифма модуля производной в УЗЛОВЫХ точках, так что на выходе сумматора 4 в результате сложения поступивших на вход чисел c) J2//-(Ao)l и fOgj. образуется значе:ниееод2 (лх IF (Xo)f , характеристика которого запоминается на буферном регистре 13, а мантисса передается на вход ПЗУ значений показательной функции 5. Во втором такте мантисса логарифма од 2 (дХ IF (Xc)i); поступившая на вход ПЗУ значений показательной функции 5, потенцируется таблицей, хранящейся в этом ПЗУ, и с помощью блока сдвига 6, учитывающим характеристику од 2 (&х(F (Хо)1) , сдвигается на требуемое число разрядов,. образуя значение дХ IF (Хс,)|) г которое передается на формирователь 7 знакового разряда. Блок.7 в случае Sign (F (Хо)) 1 на его управляющем входе выдает на выход число, поступающее на еГо вход, а при SignfF (XQ)) -1 на управляющем входе образует дополнительный код из числа на входе, взятого с обратным знаком. На выходе блока 7 образуется значение uXF (Хс)) Sign(F (Хо) дХ/ F(XO)/. Значение &XF(X ) поступает через коммутатор 3 в сумматор 4, складываясь со значением F(XQ) , поступившим в этом же такте через коммутатор 12 с выхода ПЗУ значений функции в узловых точках, В результате сложения образуется согласно (3) искомое значение функции F(X), которое запоминается на регистре результата 14. Время Т вычисления значения функции в пред)1агаемом цифровом генераторе функци-и определяется формулой T-2(,,,,t И оказывается существенно меньше, чем в известном генераторе. Формула изобретения Цифровой генератор функций, содержащий регистр младших и регистр старших разрядов аргумента, первый, второй и третий блоки памяти, первый и второй коммутаторы, сумматор, буферный регистр, регистр результата, блок управления, причем вькод регистра старших разрядов подключен к адресным входам первого, второго и третьего блоков памяти, выходы первого и второго блоков памяти через первый коммутатор подключены к первому, а выход второго коммутатора - ко второму входу сумматора, выход которого подключен ко входу буферного регистра и регистра результата, выходы блока управления подключены к управляющим входам первого и второго коммутаторов, отлич.ающийся тем, что, с целью повышения быстродействия цифрового генератора функций, он содержит четвертый и пятый блоки памяти, блок сдвига и формирователь знакового разряда, причем выход регистра лладших разрядов аргумента подключен к адресному входу четвертого блока памяти, выход которого подключен к первому входу второго коммутатора, выход сумматора подS ключей к адресному входу пятого блока памяти, выход которого, а также выход буферного регистра подключены к- соответствующим входам блока сдвига, выхсд блока сдвига подключен к 0 информационному, а выход третьего блока памяти - к управляющему входу формирователя знакового разряда, выход которого подключен ко второму .входу второго коммутатора.

Источники информации,

5 принятые во вншлание при экспертизе

0

кл. G .06 F 1/02, от 20.04„77.

Авторы

Даты

1980-01-25—Публикация

1977-09-20—Подача