памяти, пятый и шестой выходы - с управляющими входами первого и второго коммутаторов соответственно, седьмой, восьмой и девятый выходы с управляющими входами первого, второго и третьего буферных регистров соответственно,десятый выход-с управляющим входом накапливающего сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций двух аргументов | 1986 |

|

SU1413626A1 |

| Устройство для вычисления функций | 1984 |

|

SU1206767A1 |

| Устройство для логарифмирования массивов двоичных чисел | 1979 |

|

SU926654A1 |

| Множительное устройство | 1978 |

|

SU824206A1 |

| Универсальный цифровой преобразователь координат | 1980 |

|

SU924701A1 |

| Параболический интерполятор | 1984 |

|

SU1231512A1 |

| Конвейерное устройство для потенцирования массивов двоичных чисел | 1984 |

|

SU1191909A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Устройство для вычисления функций двух аргументов | 1983 |

|

SU1191917A1 |

| Устройство для логарифмирования двоичных чисел | 1981 |

|

SU1059572A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ ДВУХ ПЕРЕМЕННЫХ, содержащее регистр первого аргумента, регистр второго аргумента, первый и второй коммутаторы, первый блок памяти, комбинационный сумматор, первый буферный регистр, информационный вход которого соединен с выходом комбинационного сумматора, второй буферный регистр и блок синхронизации, отличающееся тем, что, с целью повышения быстродействия, в него введенб1 второй, третий, четвертый, пятый и шестой блоки памяти, комбинационный сдвигатель, узел формирования знака, третий буферный регистр, дешифратор, накапливающий сумматор, первыйи второй выходы регистра первого аргумента соединены с адресными входами соответственно второго и третьего блоков Памяти, первый и второй выходы регистра второго аргумента соединены с адресными входами соответственно четвертого и пятого блоков памяти, первый и второй информационные выходы второго блока памяти соединены соответственно с первым информационным входом первого кo tмyтaтopa и с первым входом Узла формирования знака, первый и второй информационные выходы четвертого блока памяти соединены соответственно с первым информационным входом второго коммутатора и с вторым входом узла формирования знака, второй и третий информационные входы первого коммутатора соединены с информационными выходами соответственно первого буферного регистра и первого блока памяти, а выход - с первым входом комбинационного сумма- Toipa, второй, третий и четвертый информационные входы второго коммутатора соединены с информационными выходами соответственно третьего блока памяти, пятого блока памяти и второго (Л буферного регистра, а выход - с вторым входом комбинационного сумматора, выход которого соединен с адресным входом первого блока памяти и с информационными входами второго и третьего буферных регистров, первый и второй информационные выходы третье го буферного регистра соединены соответственно с входом дешифратора и с адресным входом шестого блока памяти, информационный вход комбинационного сдвигателя соединен с информационным выходом шестого блока памяти, управляющий вход - с выходом дешифратора, а выход - с первым информационным входом накапливающего сумматора, второй информационный вход которогЬ соединен с выходом ; узла формирования знака, а выход - с выходом устройства, первый, второй, третий и четвертый выходы блока синхронизации соединены соответственно с управляющими входами второго, третьего, четвертого и пятого блоков

Изобретение относится к области автоматики и вычислител:ьной техники и может быть использовано для ускоренного вычисления функций F(x,y) (f(x)(f(y) от двух аргументов-в уни- 5 нереальных и специализированных ЭВМ.

Известно устройство для вычисления функций, содержащее пять блоков памяти, регистр младших и старших разрядов аргумента, два коммутатора, сумматор, блок сдвига, формирователь знакового разряда, буферный регистр, регистр результата и блок синхронизации lj .

Недостатком такого устройства 5 является ограниченность области его применения, так как оно предназначено для функций одного аргумента.

Наиболее близким по технической 20 сущности к изобретению является устройство, предназначенное для вычисления функций, двух аргументов и содержащее регистр первого аргумента,, регистр второго аргумента, первый (25 и второй коммутаторы, первый блок памяти, комбинационный сумматор, первый буферный регистр, второй буферный регистр и блок синхронизации 2 .30

Недостатками известного устройства являются его относительно невысо;кое быстродействие и невысокая точность, обусловленная используемым в нем методом линейной интерполяции. 35 Действительно, если аргументы X и У имеют .11 двоичнык разрядов и в блоке памяти хранятся значения функции ,для (X, У), бпределяемых k старшими разрядами кодов а| гументов,л() то при требуемом в этом случае блоке памяти объемом 2 слов необходимо в процессе вь1числений для получения результата с точностью Уп двоичных , разрядов выполнять, в среднем (ni-lf)/2|| операций суммирований, причем ktH/2

9F

в области вычислезуг;

при

ния значении.

Цель изобретения - повышение быстродействия .

Поставленная цель достигается тем, что в устройство для вычисления функций двух переменных, содержащее регистр первого аргумента, регистр второго аргумента, первый и второй коммутаторы, первый блок памяти, комбинационный сумматор, первый буферный регистр, информационный вход которого соединен с выходом комбинационного сумматора, второй буферный регистр и блок синхронизации, введены второй, третий, четвертый, пятый и шестой блоки памяти, комбинационньй сдвигатель, узел формирования знака, третий буферный регистр, дешифратор, накапливающий сумматор, первый и второй выходы регистра первого аргумента соединены с адресными входами соответственно второго и третьего блоков памяти, первый и второй выходы ре- --, гистра второго аргумента соединены с адресными входами соответственно четвертого и пятого блоков памяти, первый и второй информационные вькоды второго блока памяти соединены соответственно с первым информационным входом первого коммутатора и с первым входом узла формирования знака, первый и второй информационные выходы четвертого блока памяти соединены соответственно с первым информационным входом второго коммутатора и с вторым входом узла формирования знака, второй и третий информационные входы первого коммутатора соединены с информационньфш выходами соответственно первого буферного регистра и первого блока памяти, а выход - с первьн входом комбинационного сумматора, второй, третий и четвертый информационные входы второго коммутатора соединены с информационными выходами соответственно третьего блока пймяти, пятого блока памяти и второго буферного регистра, а выход с вторым входом комбинационного сум- 5 матора, выход которого соединен с ад)есным входом первого блока памяти и с информационными входами второго и третьего буферных регистров, первый и второй информационные выходы третьею го буферного регистра соединены соответственно с входом дешифратора И с адресным входом шестого блока памяти, информационный вход сдвигателя соединен с информационным выходом is шестого блока памяти, управляющий вход - с выходом дешифратора, а выход - с- первым информационным входом накапливающего сумматора, второй информационный вход которого соединен 20 с выходом узла формирования знака, а выход - с выходом устройства, первый, второй, третий и четвертый ёьЬсоды блока синхронизации соединены сЬответйтвенно с управляншщми входами 25 второгб, третьего, четвертого и пятого блоков памяти, пятый и шестой ВЫХОДЫ - с управляющими входами первого и второго коммутаторов соответственно, седьмой, восьмой и девя- зо тый выходы - с управляющими входами первого, второго и третьего буферных регистров соответственно, десятый вькод - с управляющим входом накапливающего сумматора.,

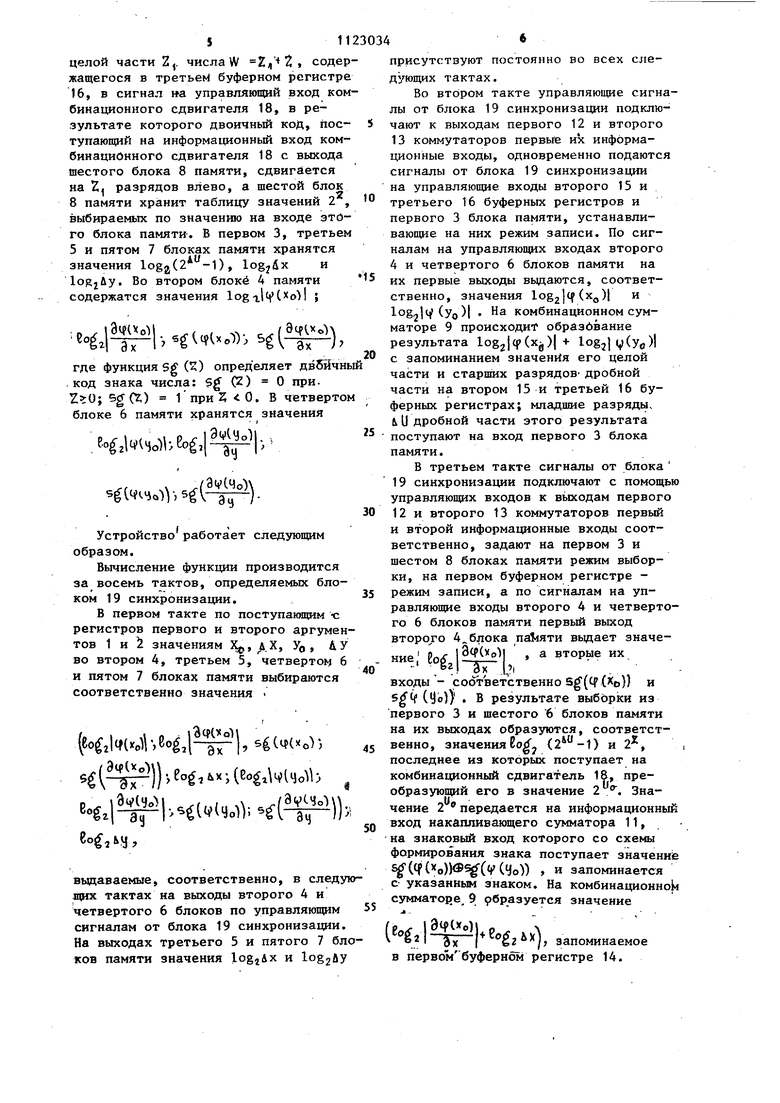

На чертеже изображена структурная схема устройства.

Устройство содержит регистр 1 первого аргумента, регистр 2 второго аргумента, первый 3,.. второй 4, 40 третий 5, четвертый 6, пятый 7 и шестой 8 блоки памяти, комбинационный сумматор 9, узел 10 формирования знака , накапливающий сумматор 11, первый коммутатор 12, второй коммутатор 5 13, первый 14, второй 15, третий 16 буферные регистры, дешифратор 17, комбинационный сдвигатель 18, блок 19 синхронизации.

Старшие разряды регистра первого 50 аргумента 1 соединены с адресным входом блока 4 памяти, а младшие г блок 5 памяти. Старшие разряды регистра второго аргумента 2 соединены с адресным входом блока 6 памяти, а 55 младшие - блока 7 памяти. Первые информационные выходы блоков 4 и 6 памяти через коммутаторы 12 и 13

подключаются к входам комбинационног сумматора 9.

Выход комбинационного сумматора 9 соединен с входами первого 3 блока памяти и первого 14, второго 15 и третьего 16 буферных регистров. Второй и третий входы первого коммутатора 12 подключен к выходам первого буферного регистра 14 и первого блок 3 памяти. Четвертый вход второго коммутатора 13 соединен с выходом второго буферного регистра 15. Входы узла 10 формирования знака соединены с вторыми выходами второго 4 и четвертого 6 блоков памяти, а ее выход подключен к знаковому входу накапливающего сумматора 11. Выход блока 19 синхронизации соединен с управляющими входами первого 3, второго 4 третьего 5, четвертого 6, пятого 7, (Шестого 8 блоков памяти с управляющими входами-первого 14, второго 15 и третьего 16 буферных регистров, первого 12 и второго 13 коммутаторов а также с управляющим входом накапливающего сумматора 11.

В первом 3 блоке памяти имеется регистр, в который записьшается информация с адресного входа; управляю щий сигнал для блока памяти определя либо прием и запись с адресного входа, либо выборку по информационному выходу.

Узел 10 формирования знака представляет собой одноразрядную логическую схему сложения по модулю 2.

Вычисление функции F(x,y) Cf (х)с(/(у) в устройстве производится на основе соотношения

Эсс(. Р(.х,у) - VC%Uvt

.ЗчЦо

(1)

Ч

где Xjj и У0 определяются старшими разрядами аргументов X и V X и У . определяются младшими разрядами аргументов X и У. ,

Значения членов разложения (1) находятся устройством предварительным логарифмированием и последующим по- тенхщрованием с помощью соответствующих таблиц, хранящихся в блоках питания. Потенцирование значения U , где и - дробная часть числа logjItfCxQ) xij/Cy j)/, выполняется на осноре соотношения 2 Iog2(), где Uоопределяется к старшими раэрядами двоичного кода числа U . Дешиф ратор 17 преобразует двоичный код $11 целой части Z,. числа W содер жащегося в третьем буферном регистре 16, в сигнал на управляющий вход ком бинационного сдвигателя 18, в результате которого двоичный код, поступающий на информационный вход комбинационного сдвигателя 18 с выхода шестого блока 8 памяти, сдвигается на Z разрядов влево, а шестой блок 8 памяти хранит таблицу значений 2 , выбираемых по значению на входе этого блока памяти. В первом 3, третьем 5 и пятом 7 блоках памяти хранятся значения 1о§2(2 -1), и logjiy. Во втором блоке 4 памяти содержатся значения log liC o)l ; Ч, Ч(}, где функция Sg () определяет дв5йчны .код знака числа: Sg (Z) О при. ,) 1при 0. В четвертом блоке 6 памяти хранятся значения ,)ЬH C.....(). Устройство работает следующим образом. Вычисление функции производится за восемь тактов, определяемых блоком 19 синхронизации. В первом такте по поступающим ч: регистров первого и второго аргументов 1 и i значениям Х,, ДХ, У , &У во втором 4, третьем 5, четвертом 6 и пятом 7 блоках памяти выбираются соответственно значения . |ЗсКХо} K2l(oi,Bo,|, sgCcfC.c,), Ч(} ° ( Р ...f,,;., Л. . Нг|-а Г Ч Но)). Ч1-а)) выдаваемые, соответственно, в следую щих тактах на выходы второго 4 и четвертого 6 блоков по управляющим сигналам от блока 19 синхронизации. На выходах третьего 5 и пятого 7 бло ков памяти значения и logjAy присутствуют постоянно во всех следующих тактах. Во втором такте управляющие сигналы от блока 19 синхронизации подключают к выходам первого 12 и второго 13 коммутаторов первые их информационные входы, одновременно подаются сигналы от блока 19 синхронизации на управляющие входы второго 15 и третьего 16 буферных регистров и первого 3 блока памяти, устанавливающие на них режим записи. По сигналам на управляющих входах второго 4 и четвертого 6 блоков памяти на их первые выходы вьщаются, соответственно, значения logjjtfCx) и )(УО)| . На комбинационном сумматоре 9 происходит образование результата log2Jq(х)| + logj ((У(,)| с запоминанием значения его целой части и старших разрядов дробной части на втором 15 и третьей 16 буферных регистрах; младшие разряды. Ь и дробной части этого результата поступают на вход первого 3 блока памяти. В третьем такте сигналы от блока 19 синхронизации подключают с помощью управляющих входов к вькодам первого 12 и второго 13 коммутаторов первый и второй информационные входы соответственно, задают на первом 3 и шестом 8 блоках памяти режим выборки, на первом буферном регистре режим записи, а по сигналам на управляющие входы второго 4 и четвертого 6 блоков памяти первый выход BTOpojo 4 блока выдает значе1 а(р(Уо) а вторые их входы - соответственно Sg(C|(Хе)) и (9Ь)) . В результате выборки из первого 3 и шестого 6 блоков памяти на их выходах образуются, соответственно, значения Cod. () последнее из которых поступает комбинационный сдвигатель 18, преобразующий его в значение 2 . Значение 2 передается на информационный вход накапливающего сумматора 11, на знаковый вход которого со схемы формирования знака поступает значение (tf Со))Ф(уСУо)) , и запоминается с указанным знаком. На комбинационной сумматоде 9 рбразуется значение : 3tf IXO) запоминаемое в первомбуферном регистре 14. в четвертом такте управляющие сигналы от блока 19 синхронизации подключают к выходам первого 12 и второго 13 коммутаторов, третий и четвертьш информационные входы и включают в режим записи третий 16 буферный регистр. Поэтому на выходе комбинационного сумматора 9 образует () + и запомися значение 2 v. 0 наемое на третьем 16 буферном регист ре. В пятом такте управляющие сигналы от блока 19 синхронизации подключают к выходам первого 12 и второго 13 коммутаторов второй и первый их информацйонные входы, включают в режим выборки шестой 8 блок памяти и в режим записи - третий 16 буферный регистр. Кроме того, сигналы на управляющих входах второго 4 и четвертого 6 блоков памяти обеспечивают выдачу на вторые входы, соответственно, 3Ha4eHm45g((f(Xfl)), Sg(V(yo)) а на первый вход четвертого блока памя ти 6 - вьщачу значения 6(7,/(ICijo)/ . Поэтому на выходе комбинационного сдвигателя 18 образуется значение (2 -iVUo которое прибавляетс с соответствующим знаком к содержимому накапливающего сумматора 11, что порождает в нём результат Cf(X(,)v{ij а на выходе комбинационного сумматор 9 образуется зНачениеВоб / ipuX/ + (9o)/ запоминаемое на третье 16 буферном регистре. В шестом такте управляющие сигналы от блока 19 синхронизации подключают к выходам первого ,12 и второго 13 коммутаторов, первый и третий их информационные входы, задают режим записи для первого 14 буферного регистра, режим выборки для шестого 8 блока памяти, на первых выходах второго 4 и четвертого 6 блоков памя ти обеспечивают вьщачу значений 6Jogj {(Xo)/ и Peg. / соответственно, а на вторых выходах этих блоков, соответственно, выдачу значений ( УЗх))) Поэтому на: комбинационном сумматоре 9 образуетс eag,|4Uo)lao., значение запоминаемое на первом 14 буферном регистре, а на выходе комбинационного сдвигателя 18 формируется значениерЧ(оУд |.р() ЛХ/ , передаваемое на информационный вход накапливающе148 го сумматора 11, на знаковый вход которого поступает с формирователя c((v(%i), знака значение 5 что приводит к сложению с содержимым накапливающего сумматора 11 значения второго члена разложения (t). В седьмом такте управляющие сигналы от блока 19 синхронизации подключают к выходам первого 12 и второго 13 коммутаторов соответственно второй и третий информационные входы, задают режим записи для третьего 16 буферного регистра, в результате чего на нем запоминается образуемое на комбинационном сумматоре 9 значение .У В восьмом такте по сигналу от блока 19 синхронизации на управляющий вход шестого блока памяти в неМ осуществляется выборка с оЬразованием на выходе комбинационного сдвигателя 1 , ,ЭЦИо -3 18 значения сигналу на управляющих входах второго 4 и четвертого 6 блоков памяти на их вторые выходы вьщаются, соответстренно значения S(cf(xо)) (,-Эи) К содержимому сумматора 11 добавляется число с выхода комбинационного сдвигателя 18 с соответствующим знаком и согласно выражению (1) образуется искомое значение функции F(я,у. . Время Т вычисления значений функЩ1И на устройстве определяется суммарной продолжительностью В тактов, каждый из которых выполняется в течение времени шах (Tgbig, ,), где Tgyg- время выборки из памяти; , время суммирования; Т 8. Для времени Т вычисления значения функции в известном устройстве Т д-.,, поэтому выигрыш по быстродействию в. пре утагаемом устройстве равен TO/Т IL В частности, при Л 16 имеем выигрыш по быстродействию в предлагаемом устройстве в четыре раза. Таким образом, введение новых блоков и конструктивньк связей позволило решить задачу повышения быстродействия устройства для вычисления функций двух аргументов.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР №,750467, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для сбора и удаления мусора | 1987 |

|

SU1413045A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-11-07—Публикация

1983-07-13—Подача