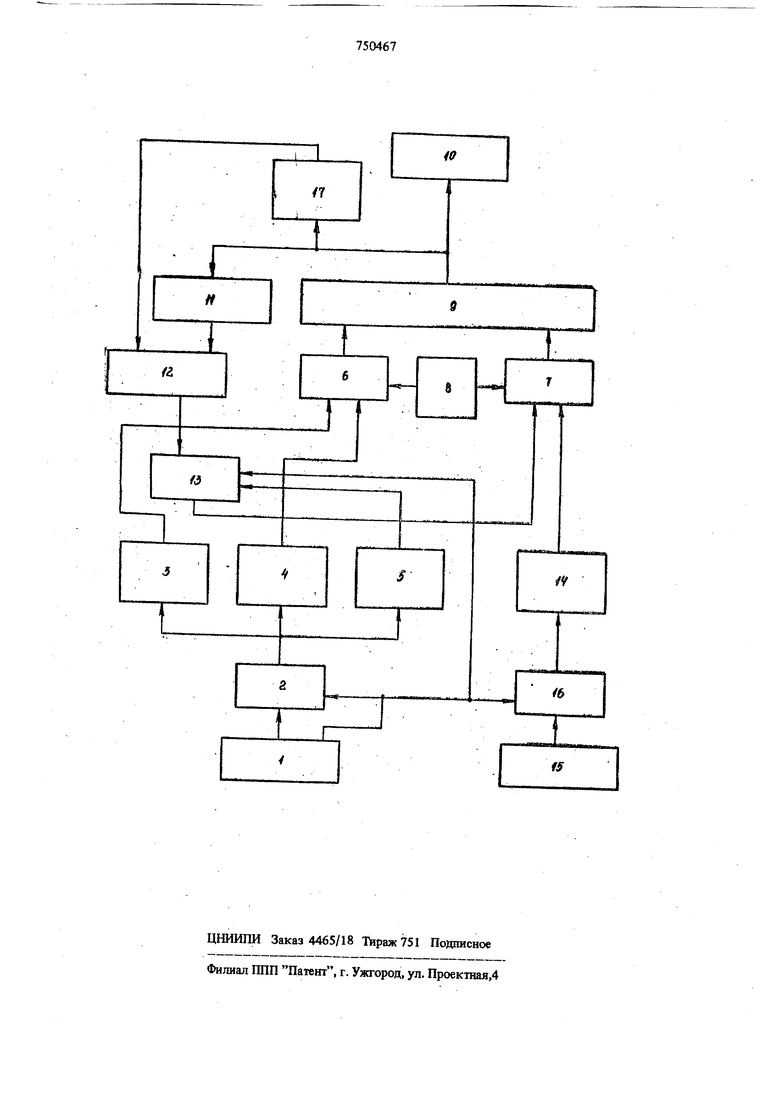

Изобретение относится к вычислительной технике и может быть использовано для аппар турной реализации аналитических функций в спепиализированных и универсальных быстр действующих цифровых вычислительных машинах. Известно устройство, содержащее преобразователь временного интервала в последовательность импульсов, блок весовых коэффициентов, выходной счетчик-регистр, блок декодирования и блок памяти (Ц. Недостатки - большой объем памяти и низкое быстродействие. Известен также цифровой генератор функций, содержащий регистр младших и регистр старших разрядов аргумента, первый, второй третий, четвертый и пятый блоки памяти, первый и второй коммутаторы, су№латор, буферный регистр, регистр результата и блок управления, причем выход регистра старших разрядов подключен к адресным входам первого, второго и третьего блоков памяти, выходы первого и второго блоков памяти через первый коммутатор подключены к первому, а выход второго коммутатора - ко второму входу сумматора, выход которого подключен ко входу буферного регистра и регистра результата, выходы блока управления подключены к управляющим входам первого и второго коммутатора. Кроме того, он содержит блок сдвига и преобразователь прямого кода в дополнительный, причем выход регистра младших разрядов аргумента подключен к адресному входу четвертого блока памяти, выход которого соединен с первым входом второго коммутатора, выход сумма-, тора подключен к адресному входу пятого блока памяти, выход которого, а также выход буферного регистра соединен с соответствующими входами блока сдвига, выход блока сдвига подключен к информационному, а выход третьего блока памяти - к управляющему входу прюбразователя прямого кода в дополнительный, выход которого подключен ко второму входу второго коммутатора 2. Недостатком данного цифрового генератора функций является относительно большая суммарная емкость используемых в нем блоков памяти. что ограничивает применение его в универсальш 1х ЦВМ. Цель изобретения - сокращение объема оборудования при незначительном (не превосх дящем времени одного сложения) уменьщении быстродействия устройства. Поставленная цель достигается тем, что в известное устройство введены второй преобразователь прямого кода в дополнительный и блок коррекции, причем первый выход регистра старших разрядов аргумента подключен ко входу блока коррекции, а второй выход подключен к управляющим входам блока коррекции, второго преобразователя пря мого кода в дополнительный, и второму управл 1 ющему входу первого преобразователя , прямого кода, в дополнительный, выход блок коррекции подключен ко входам первого, второго и третьего блоков памяти, выход регистра младщих разрядов аргумента подключен к входу второго преобразователя прямого кода в дополнительный, выход которого подключен ко входу четвертого блока памяти. На чертеже представлена блок-схема предлагаемого устройства. Устройство состоит из последовательно соединенных регистра 1 старших разрядов аргумента и блока 2 коррекоди, выход которого подключен к адресным входам первого, второго и третьего блоков 3, 4, 5 памяти из первого и второго коммутаторов 6 и 7, управляк1идие входы которых подсоединены к блоку 8 управления, а выходы - к первому и второму входам сумматора 9. Выход сумма тора 9 подключен ко входам регистра 10 результата и буферного регистра 11, а выход буферного регистра 11 через первый вход блока 12 сдвига и первый преобразователь 13 прямого кода в дополнительный - ко входу второго коммутатора 7; другой вход которог соединен с выходом четвертого блока 14 памяти. Кроме того, в состав устройства входят последовательно соединенные регистр 15 младщих разрядов аргумента и второй преобразователь 16 прямого кода в дополнительный, выход которого подключен к адресному входу четвертого блока 14 памяти, а также Пятый блок 17 памяти, адресный вход которого соединен с выходом сумматора 9, а выход подключен к второму входу блока 12 сдвига. Выходы первого и второго блоков 3 и 4 памяти подключе11Ы ко входам первого коммутатора 6, а выход третьего блока 5 памяти - к первому управляющему входу первого преобразователя 13 прямого кода в дополнительный. Кроме того, младший разряд регистра 1 старших разрядов аргумента подключен к управляющим входам второго прео 4 азователя 16 прямого кода в дополнительный, лока коррекции 2 и ко второму управляюему входу первого преобразователя 13 пряого кода в дополнительный. Работа цифрового генератора функций осуществляется следующим образом. В первом такте работы устройства, в зависимости от значения младшего разряда х регистра старших разрядов аргумента, значения узловой точки XQ И приращения аргумента ЛХ, хранящихся соответственно на регистрах старших и младших разрядов аргумента 1 и 15 с помощью блока коррекции 2 и второго преобразователя 16 прямого кода в дополнительный преобразуются в значения Z и AZ в соответствии с соопюшениями: (дх.еслы Х.,о Z если дг.« Ьо2:, 2. лх,еслих 1 если Значение приращения д7, поступает на адресный вход четвертого блока памяти, в котором хранится таблица значений . и с выхода 3Tord блока памяти значение передается через второй коммутатор 7 на второй вход сумматора- 9. Одновременно, в этом же такте, значение Z,, образованное на выходе блока 2 коррекции, поступает на адресные входы первого, второго и третьего блоков 3, 4, 5 памяти хранящих соответственно, таблицы значенийР(2, ) &ОР Fte М 3.grnZ, i.если Z. 7/0 usrgn(FZ), где еслмХ СО В первом такте работы устройства первый коммутатор 6 подключает к сумматору 9 выход первого блока 3 памяти, так что на выходе сумматора 9 в результате сложения поступивших на входы чисел Og2|F(Z(| 2 образуется значение tog(A2iF(ZJ|, характеристика которого запоминается на буферном регистре И, а мантисса передается на адресный вход пятого блока 17 памяти, хранящего таблицу значений 2 Во втором такте работы мантисса логарифма .( 2|i (2)1)поступившая на адресный вход пятого блока 17 памяти, потенцируется таблицей, хранящейся в этом блоке памяти, и с помощью блока 12 сдвига, учитывающим характеристику Со,,(л2, (ZQ)I}, сдвигается на требуемое число разрядов, образуя значение AZ|F(Z(,)| которое передается на первый преобразователь 13 прямого кода в дополнительный. Этот преобразователь в случае ((ZJ - 1 на. первом управляющем входе и Sn(X.)-l на втором управляющем входе, а также в случае (F(Zo) -1 и Sn(x.,)--i на этих входах выдает на выход число, по57504676

ступающее на его вход, а при других состоя-буферный регистр и регистр результата, приниях управляющих входов образует дополни-чем выходы первого и второго блоков пательный вход из числа на входе, взятого с обратным знаком, так что на выходе преобра вателя 13 прямого кода в дополнительный всегда образуется значение Sn(XjFCZjAZ Sign(F(Z))Sn(XjAZF(Z) Это значение Sn(yjAZ-F(Zo) поступает через второй коммутатор 7 на сумматор 9, складываясь на нем со значением F(ZQ), поступившим в этом же такте через первый . коммутатор 6 с выхода первого блока 3 памяти. В результате сложения образуется согласно соотношения-,Р(х)Р(2,)(Р (7,)) 5П(Х ),(F(2o)) искомое значение функции Ь(х) которое запоминается на регистре 10 результата. Сокращение объема оборудования, т.е. емкости блоков памяти в рассматриваемом уст ройстве, связано с меньшей, чем у XQ- разрядностью узловых точек 2,. Расчеты показывают, что для функции F()-tg и для разрядной сетки П 24, Q 398 Кбит, СХ 269 Кбит и, таким образом, выигрыш в суммарной емкости блоков памяти превышает 32%. Для функции F(x) -V , 1/16 X 4 1 и П 24, имеем, соответстве но Q 665 Кбит и Q 365 Кбит, а выигрыш в суммарной емкости превышает 55%. Формула изобретения Цифровой генератор функций, содержащий регистр старшего разряда аргумента, регистр младшего разряда аргумента, первый, второй, третий, четвертый и пятый блоки памяти, первый преобразователь прямого кода в дополнительный, блок сдвига, блок управления, первый и второй коммутаторы, сумматор, буферный регистр и мутаторы, сумматор. мяти через первый коммутатор второго блоков памяти через первый коммутатор подключены к первому, а выход четвертого блока памяти через второй коммутатор подключен ко второму входам сумматора, выход которого подключен ко входам буферного регистра результата к пятого блока памяти, выход которого подключен ко входу блока сдвига, второй вход которого подключен к выходу буферного регистра, а выход - ко входу первого преобразователя прямого кода в дополнительный, управляющий вход которого подключен к вьтходу третьего блока памяти, а выход подключен ко второму входу второго коммутатора, выходы блока управления подключены к управляющим входам первого и второго коммутаторов, от л ичающийся тем, что, с целью сокращения объема оборудования, в него введены второй преобразователь прямого кода в дополнительный и блок коррекщ1И, причем первый выход регистра старших разрядов аргумента подключен ко входу блока коррекции, а второй выход - подключен к управляющим входам блока Коррекции, второго преобразователя прямого кода в дополнительный и второму управляющему входу первого преобразователя прямого кода в дополнительный. выход блока коррекции подключен ко входам первого, второго и третьего блоков памяти, выход регистра младших разрядов аргумента подключен к входу второго преобразователя прямого кода в дополнительный, выход которого подключен ко входу четвертого блока памяти. Источники информации, принятые во внимание при экспертизе .1. Авторское свидетельство СССР № 451989, кл. G 06 F 1/02, 1973. 2. Авторское свидетельство СССР по заявке N 2528831/18-24, кл. G 06 F 1/02, 20.09.77 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций | 1984 |

|

SU1206767A1 |

| Цифровой генератор функции | 1977 |

|

SU711556A1 |

| Цифровое устройство для воспроизве-дЕНия фуНКций | 1979 |

|

SU809126A1 |

| Цифровой функциональный преобразователь | 1977 |

|

SU742947A1 |

| Множительное устройство | 1978 |

|

SU824206A1 |

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

| Устройство для вычисления функций двух переменных | 1983 |

|

SU1123034A1 |

| Вычислительное устройство | 1983 |

|

SU1080135A1 |

| Логарифмический преобразователь | 1984 |

|

SU1196860A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1130861A1 |

Авторы

Даты

1980-07-23—Публикация

1978-06-08—Подача