Изобретение предназначено для использования в области автоматики и вычислительной техники. Известны устройства для суммирования импульсных последовательностей Устройство содержит распределитель импульсов, генератор тактовых импульсов, умножитель частоты, запоминаицие триггеры, элементы И и ИЛИ 1. В этом устройстве сигналы входных суммируемых последовательностей запоминаются на время,цикла суммирования на входных запоминающих триггерах и далее информация с упомянутых триггеров считывается на выход устройства через элемент ИЛИ сигналами с выходов распределителя импульсов. Устройство содержит генератор опо ной частоты, функциональный генератор, счетчики импульсов, блок управления, элементы И, ИЛИ, схемы запрета 2. В этом устройстве результат суммирования формируется в виде кода в выходном счетчике импульсов. Недостатками известных устройств Являются низкая точность, ограниченный диапазон и невысокая надежность. Из известных устройств для суммирования импульсных -последовательностей наиболее близким по технической сущности является устройство для суммирования импульсных последовательностей 3. Это устройство содержит четыре счетчика импульсов и два регистра, входы и выходы первого из которых соответственно через первую и вторую групгщ элементов И переноса соединены с выходами первого и входами второго счетчиков, а входвл и выходы второго регистра соответственно через третью и четвертую группы элементов И переноса соединены с выходами третьего и входами четвертого счетчиков, управляющие входы лервой группы элементов И переноса Через первый элемент задержки подключены к входу первого слагаемого устройства, к входу второго элемента задержки, к первым входам первого, второго, третьего и четвертого элементов И .управления и первому входу первого элемента ИЛИ, управляющие входы второй и четвертой групп элементов И переноса подключены соответственно к входам первого и второго триггеров управления, управлякадие входы третьей группы элементов И переноса через третий элемент задержки соединены с входом обнуления второго реистра, с первыми входами третьего, етвертого и пятого триггеров управения, с выходом пятого элемента И правления и входом четвертого элеента задержки, выход которого соеинен с входом обнуления третьего четчика, первый вход шестого элемена И управления, соединенного выходом входом первого счетчика, связан с выходом шестого триггера управления, вход которого подключен к выходу первого элемента И управления, соединенного входами с выходами пятого и седьмого триггеров управления, и подключен к первому входу седьмого элемента И управления и через последовательно соединенные пятый элемент задержки и восьмой триггер управления подключен к второму входу седьмого элемента И управления, соединенного выходом с входом седьмого триггера управления, второй выход которого подключен к первому входу восьмого элемента И .управления, второй вход которого соединен с входом второго слагаемого устройства, счетный вход третьего счетчика соединен с выходом девятого элемента И управления, связанного входом с выходом второго элемента ИЛИ первый вход десятого элемента И управления подключен к выходу третьего триггера управления, а второй его вход - к входу запуска устройства, второму входу второго элемента И управления и входу одиннадцатого элемента И управления, другие входы которого соединены с выходом пе|рвого . элемента ИЛИ и выходом первого триггера управления, а выход девятого элемента И управления связан с первым входом третьего элемента ИЛИ; клемма подачи второго слагаемого соединена с соответствующими входами трГетьего, пятого, двенадцатого элементов И управления и третьим входом первого элемента ИЛИ, выход второго элемента И управления через последовательно соединенные шестой элемент задержки и девятый триггер управления подключен к второму входу четвертого элемента И управления и входу второго элемента ИЛИ, второй вход которого соединен с входом пятого элемента И управления и выходом десятого триггера управления, подключенного входом через седьмой элемент задержки к выходу двенадцатого элемента И управления, второй вход четверт го триггера управления, соединенного выходом с входом двенадцатого элемента И управления, подключен к выходу Пятого триггера управления, выходы которого сЪединены с соответ.ствующими входами второго и двенадцатого элементов И управления, а выход третьего элемента И управления соединен с входом восьмого элемента задержки; вход обнуления первого счетчика соединен с выходом второго

элемента задержки, а выход восьмого элемента задержки подключен к второму входу первого элемента ИЛИ.

Недостатками известного устройства 5 являются низкая точность и ограниченный диапазон изменения входных частот и выходной частоты. Это обус ювлено тем, что при увеличении суммируемых частот F и Fg существенно увеличиваQ ется погрешность дискретности результата, образованного во втором и тре.тьем счетчиках, что в конечном итоге определяет и выходную результирующую погрешность устройства. Таким образом, при необходимости уменьшения

погрешности существенно сужается диапазон изменения входных частот (и, следовательно, выходной частоты), а при необходимости обеспечения более широкого диапазона существенно увеличивается погрешность операции суммирования.

Целью настоящего изобретения является повышение точности и расширение диапазона изменения входных частот и 5 выходной частоты с одновременным увеличением быстродействия.

Поставленная цель достигается тем, что в устройство для суммирования импульсных последовательностей дополQ нительно введены два блока вычисления функционала коррекции, два блока временной задержки сигналов, два фазосдвигающих блока, одиннадцатый, двенадцатый и тринадцатый триггеры управ2 ления, тринадцатый, четырнадцатый и пятнадцатый элементы И управления, девятый, десятый, одиннадцатый,-двенадцатый и тринадцатый элементы задержки при этом первый вход первого. блока вычисления функционала коррекции подключен к входу первой последовательности импульсов опорной частоты, второй его вход - к входу второй последовательности импульсов опорной частоты, третий вход - к выходу второго элемента И и четвертый вход - к выходу двенадцатого элемента И управления; выход первого блока вычисления функционала коррекции свяэан с первым входом первого блока временной задержки сигналов, второй вход которого подключен к выходу тринадцатого элемента И управления и череэ девятый элемент задержки - к управляющим входам четвертой группы элементов и переноса, а выход - к второму

входу шестого элемента И управления и к первому входу первого фазосдвигающего блока, второй вход которого подсоединен к выходу десятого элемента И управления, а его выход - к

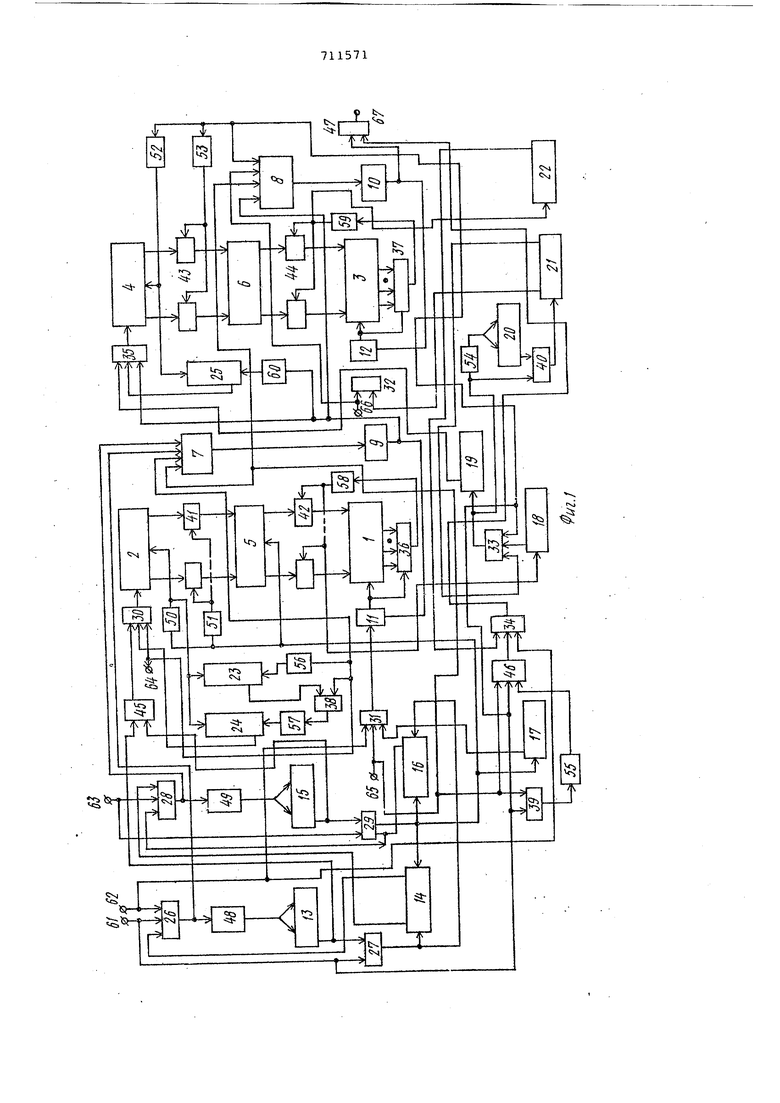

управляющему входу тринадцатого элемента И управления и к счетному входу четвертого счетчика, разрядные выходы которого связаны с входами тринадцатого элемента И управления; третий вход девятого элемента И управления подключен к выходу одиннадцато го триггера управления, вход установ ки в.1 которого подсоединен через десятый элемент задержки к выходу че тырнадцатого элемента И управления, первый вход которого связан с входом первой последовательности импульсов опорной частоты, а второй вход - с выходом двенадцатого триггера управпения, вход установки в 1 которого подключен через одиннадцатый элемент задержки к входу первой последовательности импульсов опорной частоты, а вход установки в нуль - к шине установки третьего счетчика, первый вход второго блока вычисления функци онала коррекции подключен к выходу первого блока временной задержки, вт рой его вход - к входу второго слага емого, третий вход - к входу второй последовательности импульсов опорной частоты и четвертый вход - к входу ;первого слагаемого, выход второго блока вычисления функционала коррекции связан с первым входом второго блока временной задержки, второй вхо которого подключен к выходу пятнадца того элемента И управления и через двенадцатый элемент задержки - к управляющим входам второй группы элементов И переноса, а выход - к второ му входу третьего элемента ИЛИ и к первому входу второго Лаэосдвигающего блока, второй вход которого подключен к выходу восьмого элемента И управления, а его выход - к управляющему входу пятнадцатого элемента И управления и к счетному ходу второго счетчика, разрядные выходы которо го связаны с входами пятнадцатого элемента И управления; третий вход двенадцатого элемента И управления подключен к выходу тринадцатого триг гера управления, вход установки в 1 которого подключен через тринадцатый элемент задержки к выходу первого блока временной задержки, а вход установки в О - к входу обнуления первого счетчика. На фиг, 1 изображена функциональная схема предложенного устройства; на фиг. 2 - временная диаграмма, поясняющая его принцип работы. Устройство состоит из счетчиков импульсов 1-4, регистров 5, 6, блоков 7, 8 вычисления функционала коррекции, блоков 9, 10 временной задержки сигна лов, фазосдвигающих блоков 11, 12, .триггеров управления 13-25, элементор И управления 26-40, групп элемен тов И переноса 41-44, элементов ИЛИ , элементов задержки 48-60, входов 61-67. В процессе функционирования устройства реализуется следующее выра-l3±lL.-fl±2. жение -14 -Vr;., Т,Т,,: FV Значение F получается с помощью счетчиков 1, 2, регистра 5, блока вычисления функционала коррекции 7, блока временной задержки сигналов 9, фазосдвигающего илока 11, а также логических элементов для управления сигналами на входах счетчиков 1, 2. Выражение (1) в целом реализуется на счетчиках 3, 4, регистре 6, блоке вычисления функционала коррекции 8, блоке временной задержки сигналов 10, фазосдвигающем блоке 12 и других логических элементах, служащих для управления соответствующими сигналами. Сначала опишем работу части устройства, предназначенной для получения величины F , Входные сигналы первой последовательности с частотой следования F , характеризукйдие одно из слагаемых, подаются на вход 61 (поз. 1 на временной диаграмме фиг. 2). Сигналы второй последовательности с частотой следования F, , характеризующие второе слагаемое, подаются на вход 63 (поз. 2), Сигналы опорных частот и РОПа подаются соответственно на входы 64, 65 (поз. 3, 4), Причем частота .fortx общем случае превышает частоту в несколько раз. В исходном состоянии счетчики 1-4, регистры 5, 6 и триггеры управления обнулены. В момент tj на вход 62 подается сигнал разрешения (поз. 5). При этом, -первый после момента t импульс, подаваемый на вход 61, проходит через элемент И управления 26 и через элемент задержки 48 на счетный вход триггера управления 13, переводя его из нулеiBoro в единичное состояние, С переводом триггера 13 в единичное состояние отпирающий сигнал с его выхода подается на вход элемента И управления 27 и через элемент ИЛИ 45 - на вход элемента И управления 30.- При этом через элемент И управления 30 после перевода триггера 24 в единичное состояние на счетный вход счетчика 2 начинают подаваться сигналы опорной частоты on-i которые выполняют функцию заполнения периодов входных сигналов. Сигналы на входе счетчика 2 представлены на поз. 6 фиг. 2, Заполнение периода частоты F осуществляется до момента поступления следующего сигнала на клемму 61. Информация в счетчике 2 Представлена на поз. 7. Следует отметить, что подача двух из импульсов частоты , на вход счетчика 2 запрещается. Это осуществляется с поощью триггеров 23, 24, элемента И упра.влени.я 38 и элементов задержки 56, 57. Сигнал из входной последовательноси каждый раз перед очередныи циклом уммирования устанавливает триггеры 23, 24 в нулевое состояние, запирая лементы И управления 30 и 38. При том, первый после подачи сигнала иэ последовательности F сигнал частоты проходит через элемент задержки 56 и устанавливает триггер 23 в состояние 1 в результате чего отпирается элемент И управления 33. Следующий импульс частоты Ff, проходит через элемент И 38 и далее через элемент задержки 57 на вход триггера 24, устанавливая его в состояние 1. В результаре этого отпирающий потендаал подается на вход элемента И управления 30 и третий и все последующие импульсы из последова.тельности с частотой FQPI проходят на вход счетчика 2. Следует отметить, что одновременно с подачей сигнала на клемму 61 блок вычисления функционала коррекции начинает определение функционала коррекции периода выходного сигнала. С поступлением на клемму 61 следующего (второго после ,подачи сигнала разрешения) импульса он проходит на выход элемента И управления 27, переводя триггер управления 14 в единичное состояние, и через время, определяемое элементом задержки 48, переводит три.ггер 13 в нулевое состояние. В результате прекращается подача отпирающего напряжения на вход элемента И управления 30, прекращается подача сигналов опорной частоты на вход счетчика 2 и в нем фиксируется инфор мация, соответствующая периоду Т-. Од новременно, в результате перевода три триггера 14 в единичное состояние открывается элемент И управления 28 для сигналов второй последовательности с частотой: F2. и запирается элемент И управления 26 для сигналов с частотой F . Первый после момента отпирания элемента И 28 сигнал из последовательности F/j, проходит через элемент И 28 на вход блока 7, где решается функционал коррекции, и через элемент задержки 49 - на счетный вход триггера управления 15, переводя его из нулевого в единичное состояние. В результате отпирающий сигнал с выхода триггера управления 15 подается на вход элемента И управления 29 и ч рез элемент ИЛИ 45 - на вход элемента И 30. При этом через элемент И 30 на вход счетчика 2 начинают подавать ся сигналы опорной частоты Fptu (поз. 6), которые суммируются с ранее накопленной в счетчике 2 информацией о переходе частоты F . Запол нение, периода сигналов второй последова ельности с частотой F, ocyuiecTвляб1тся до момента поступления следующего сигнала на вход 63. При поступлении сигнала на указанный вход он проходит на выход элемента И упра ления 29, переводя триггеры управления 16 и 17 в единичное состояние и триггер 14 - в нулевое, и через время., определяемое эле1-1ентом задержки 49 переводит триггер 15 в нулевое состояние. В--результате отпирается элемент И управления 26 для прохождения сигналов с частотой F , элемент И управления 31 для прохождения сигналов с частотой Fonz счетный вход счетчика 1 и запирается элемент И управления 30 для прохождения на счетный вход .счетчика 2 сигналов опорной частоты FontТаким образом в счетчике 2 фиксируется информация о сумме двух периодов Т и (поз. 7) . Число импульсов, зафиксированное в счетчике 2, определяется как , опл где Трп - период сигналов опорной частоты F,п Информация, накопленная в счетчике 2, переписывается в регистр .5 (поз. 8), где запоминается, а счетчик 2 обнуляется. В блоке вычисления функционала коррекции 7 при этом определяется величина л Т поправки выходного -периода, которая подается на вход блока временной задержки 9. Далее описанный выше процесс получения информации в счетчике 2 о сумме двух периодов повторяется. Сигналы опорной частоты F , проходящие с входа 65 через элемент И управления 31 и фазосдвигающий блок 11 на вход счетчика 1 (поз. 9), пересчитываются в нем. В процессе функционирования информация в счетчике 1 имеет вид, представленный на поз. 10. Выходные сигналы пересчета счетчика . Iформируются на выходе многовходо5ого элемента И управления 36, подключенного к разрядным выходам счетчика 1 таким образом что он открывается для сигналов Fona лишь в момент достижения в счетчике 1 единичной информации . В этот момент появляются на его выходе сигналы пересчета. Указанные сигналы подаются на вход блока временной задержки 9, на вход триггера 18 и через элемент задержки 58 - на управляющие входы группы элементов И переноса 42, В результате этого информация, запомненная в регистре памяти 5, периодически передается через группу элементов И переноса 42 в счетчик If образуя его исходную установку, а также осуществляется задержка сигнала на величину лТ, вырабатываемая 3 блоке 7. Задержанные сигналы с выхода блока временной задержки 9 полаются на один из входов фазосдвигающего блока 11, а также на входы элемента И управления 35 и блока вычисления функционала коррекции 8. На выходе фазосдвигающего блока IIпри подаче сигналов с выхода блока 9 вырабатываются сдвинутые по фазе сигналы с частотой таким образом, чтобы отсутствовал сдвиг по отношению к сигналам с выхода блока временной задержки 9. В этом случае на выходе блока 9 имеют место сигна пы, период которых изменен на велич ну, вырабатываемую в блоке 7, В зависимости от величины исходной установки на выходе элемента И 36 устанавливается вполне определен ная частота, .которая пропорциональ .., ... на- частоте F (поз. 11). Это определяетея следующим обраэом. Период последовательности импульсов на выходе элемента И 36 определяется вьфажением BblXd ОП2 Н где Тр„,2 - период Последовательности :импульсов частоты РОПЗ/ действующей на входе счетчика 1. Подставляя (2) в (3), получим т,т„-), BblX-t Т |или в частотном представлении БЫ.1 F Величина является константой. После появления первого же сигнала на выходе блока временной задержки 9 (поз. 11) триггер 18 переводится из нулевого в единичное состояние При этом первый после момента перевода триггера 18 импульс, подаваемый на вход 61, проходит через И управления 33, переводит триггер 19 и с задержкой триггер 20 в единич ное состояние, в результате перевода триггера 19 в единичное состояние отпирается элемент И управления 35 для сигналов с выхода блока временно задержки 9, которые начинают проходить на счетный вход счетчика 4. Сиг налы на входе счетчика 4 представлены на- поз. 12, а информация в нем - на поз. 13. Заполнение периода часто ты F- осуществляется до момента поступления следующего сигнала на вхол 61. Следует отметить, что подача одного из импульсов последовательнос ти сигналов с выхода блока 9 на вход счетчика 4 запрещается, что необходи о для осуществления коррекции перио да выходного сигнала. Запрет одного импульса осуществляется с помощью триггера 25 и элемента задержки 60, Сигнал из последовательности с частотой F каждый раз устанавливает триггер 25 в нулевое состояние, запи рая элемент И. управления 35. При это первый после подачи сигнала F сигна с выхода блока 9 не проходит на счет ный вход счетчика 4, а проходит через элемент задержки 60 и устанавлиjaeT триггер 25 в состояние 1. В результате элемент И 35 отпирается для поступающих на его вход сигналов и все последующие импульсы с выхода бло ка 9 проходят на счетный вход счетчика 4, Следует отметить, что одновременно с подачей сигнала на вход 61 он подается далее и на вход блока 8, который при этом начинает определение функционала коррекции периода выходйого сигнала. Наряду с этим с приходом каждого последующего импульса из последовательности с частотой следова ния Р осуществляется обнуление регистра 6, передача накопленной в счетчике 4 информации в регистр 6 (поз, 14) и обнуление счетчика 4. В блоке вычисления функционала кор рекции 8 при этом определяется величина дТ поправки выходного периода, oтopaя подается на вход блока вре енной задержки 10. Далее описанный выше процесс получения информации в счетчике 4 повторяется. Необходимая : задержка в подаче сигналов с клеммы 66 с частотой п Fg на вход счетчика 3 осуществляется следующим образом. Следующий за импульсом из последовательности F, переведшим триггеры 19 и 20 в единичное состояние, импульс той же последовательности проходит через элемент И управления 40 и устанавливает триггер 21 в состояние- 1. В результате опирается элемент И 32 для прохождения на вход счетчика 3 сигналов с частотой умноженной в общем случае на коэффициент умножения п (поз. 15) и запирается элемент И управления 33. Сигналы на входе счетчика 3 представлены на поз. 16. Итак, сигналы с частотой следования F/2-n, проходящие с входа 66 через элемент И 32 и фазосдвигающее устройство 12 на вход счетчика 3, пересчитываются в .нем. В процессе функционирования, информация в счетчике 3, который работает в режиме вычитания, имеет вид, представленный на поз. 17. Выходные сигналы пересчета счетчика 3 формируются на выходе многовходового элемента И 37, подключенного к разрядным выходам счетчика 3 таким образом, что он открывается для сигналов лишь в момент-достижения в счетчике 3 единичной информации. В эти моменты появляются на его выходе сигналы пересчета. Указанные сигналы подаются на вход блока временной задержки 10 и через элемент задержки 59 - на управляющие входы группы элементов И переноса 44. В результате этого информация, запомненная в регистре 6, периодически передается через группу элементов И переноса 44 в счетчик 3, образуя его исходную установку, а также осуществляется задержка сигнала на величину лТ, вырабатываемую в блоке В. Задержанные сигналы с выхода блог Ra временной задержки 10 подаются на один из входов фазосдвигающего блока 12, на вход триггера 22, а также про ходят через элемент ИЛИ 47 на выход 67, образуя последовательность импульсов, характеризующую окончательный результат (поз. 18). При этом под действием первого импульса с выхода блока 1.0 триггер 22 переводится в состояние 1, что приводит к запира нию элемента И управления 34 для сиг налов двух последовательностей с выхода элемента ИЛИ 46, которые опреде ляли сумму при неравномерном распределении до момента появления сигналов на выходе блока 10. йа выходе фазосдвигающего блока 12 при подаче сигналов с выхода блока 10 вырабатываются сдвинутые по фа зе сигналы с частотой- п Рд таким образом,чтобы отсутствовал сдвиг по отношению к сигналам с выхода блока временной задержки 10. В этом случае на выходе блока 10 имеют место сигналы, период которых изменен на вели чину, вырабатываемую в блоке 8, В зависимости от величины исходной установки, периодически запиаыйа емой в счетчик 3, на выходе блока 10 устанавливается вполне определенная частота, которая характеризует собой окончательный результат. Следует отметить, что каиодый Последующий импульс частоты Р осуществляет периодический сброс старой информации. Ко личество импульсов, поступаквдих в течение - периода Т последовательнос ти с частотой F на вход счетчика 4 с учетом (4), определяется как -1 oп ,.Т,7 Топ Дериод последовстельности импульсов на выходе элемента И 37 определяется выражением Ja-VjaVon-i вых я Или.в частном представлении . V a --T±7f8 Величина является константой и для получения правильного результа ,та... ее следует приравняешь единице, . Таким образом, из изложенного сле дует, что предложенное устройство обеспечивает существенное повышение точности при одновременном расширении диапазона изменения вхбдной и .выходной частоты. Это обусловлено тем, что в устройство в каждой его ступени (счетчики 1, 2, регистр 5 первая ступень и счетчики 3, 4, регистр б - вторая ступень) осуществл зтся коррекция периода сигнала на выходе соответствующей ступени на величину, зависящую от состояния счетчиков. При этом сохраняется высокая точность в широком диапазоне изменеВИЯ частот. Формула изобретения.; Устройство для сумг-гарования импульсных последовательностей, содержащее Четыре счетчика импульсов и два регистра, входы и выходы первого из которых соответственно через первую и вторую группы элементов И переноса соединены с выходами первого и входами второго счетчиков, а входы и выходы второго регистра соответственно через третью и четвертую группы элементов И переноса соединены с выходаМи . третьего и входами четвертох о счетчиков, управляющие входы.первой группы элементов И переноса через первый элемент задержки подключены к входу первого слагаемого устройства к вхрДу второго элемента задержки, к первым входам первого, второго, третьего и , четвертого элементов И управления и первому входу первого элемента ИЛИ, управляющие входы второй и четвертой групп элементов И переноса подключены соответственно к входам первого и второго триггеров управления, управляющие входы третьей группы элементов И переноса через третий элемент задержки соединены с входом обнуления второго регистра, с первыми вхоцами, третьего, четвертого и пятого триггеров управления, с выходом пятого элемента И управления и входом четвертого элемента задержки, выход которого соединен с входом обнуления третьего счетчика, первый вход шестого элемента И управления, соединенного выходом с входом первого счетчика, связан с выходом шестого триггера управления, вход которого подключен к выходу Первого элемента И управления, соединенного входами с выходами . пятого и седьмого триггеров управления, и подключен к первому входу седьмого элемента И управления и черед последовательно соединенные пятый элемент задержки и восьмой триггер управления подключен к второму входу седьмого элемента И управления, соединенного ВЕЛХОДОМ с входом седьмого триггера управления, второй вход которого подключен к первому входу восьмого элемента И управления, второй вход KOTOpioro соединен с входом второго слагаемого устройства, счетный вход третьегосчетчика сое- динен с выходом девятого элементами управления, связанного входом с выходом второго элемента ИЛИ; первый вход девятого элемента И управления подключен к выходу третьего триггера управления, а йторой его вход - к входу запуска устройства, второму входу

второго элемента И управления и входу одиннадцатого элемента И управления, другие входы которого соединены р выходом первого элемента ИЛИ и выходом первого триггера управления, а выход девятого элемента И управлеВИЯ соединен с первым входом третьего элемента ИЛИ; вход второго слагаемого соединен с соответст1эующими входами третьего, пятого, двенадцатого элементов И управления и третьим вхо дом первого элемента ИЛИ; выход второго элемента И управления через последовательно соединенные шестой элемент задержки и девятый триггер управления подключен к второму входу четвертого элемента И управления и входу второго элемента ИЛИ, второй вход которого соединен с входом пятого элемента И управления и выходом десятого триггера управления, подключенного входом через седьмой элемент задержки к выходу двенадцатого элемента И управления; второй вход четвертого триггера управления, соединенного выходом с входом двенадцатого элемента И управления, подключен к входу пятого триггера управления, выходы которого соединены с соответствующими входами вгорого и двенадцатого элементов И управления, а .выход третьего элемента И управления соединен с входом восьмого элемента задержки, вход обнуления первого счечика соединен с выходом второго элемента задержки, а выход восьмого элемента задержки подключен к второму входу первого элемента ИЛИ, о т л ичающеес я тем, что, с целью повышения точности и расширения диапазона изменения входных частот с одновременным увеличением быстродействия j в него введены два блока вычисления функционала коррекции, два блока временной задержки, два фазосдвигающих блока, одиннадцатый, двенадцатый и тринадцатый триггеры управления, тринадцатый, четырнадца,тый и Пятнадцатый элементы И управ1ления, девятый, десятый, одиннадцатый, двенадцатый и тринадцатый элементы задержки; при этом первый вход первого блока вычисления функционала коррекции подключен к входу Первой последовательности импульсов опорной частоты, второй его вход - к входу второй последовательности импульсов опорной частоты, третий вход - к выходу второго элемента И управления и четвертый вход - к выходу двенадцатого элемента И управления, Первого блока вычисления функционала коррекции связан с первым входом первого блока временной задержки сигналов, второй вход которого подключен 1 выходу тринадцатого элемента И управления и через девятый элемент зацержки - к управляющим входам четвер той группы элементов И переноса, а

Выход - к второму входу шестого элемента И управления и к йервому входу первого фазосдвигаюшего блока, второ вход которого подсоединен к выходу десятого элемента И управления, а ег выход к управляющему входу тринадцатого злемента И управления, и к счетному входу четвертого счетчика, разрядные выходы которого связаны с входами тринадцатого элемента И управления; третий вход девятого элемента И управления подключен к выходу одиннсщцатого триггера управления вход установки в 1 которого подсоединен через десятый элемент зсцаержки к выходу четьфнадцатого элемента И управления, первый вход которого связа с входом первой последовательности импульсов опорной частоты, а второй вход - с выходом двенадцатого триггера управления, вход установки в i которого подключен через одиннадцатый элемент задержки к входу первой последовательности импульсов опорной частоты, а вход установки в нуль - к входу обнуления третьего счетчика, первый вход второго блока вычисления функционала коррекции подключен к выходу первого блока временноп задержки, второй его вход - к входу второг слагаемого, третий вход - к входу втрой последовательности импульсов опоной частоты, четвертый вход - к входу первого слагаемого, выход второго блока вычисления функционала коррекции связан с первым входом второго блока временной задержки сигналов. Второй вход которого подключен к выходу пятнадцатого элемента И управления и через двенадцатый элемент задержкк - к управляющим входам второй группы элементов И переноса, а выход - к второму входу третьего элемента ИЛИ и к первому входу второго фазосдвигаюцего блока, второй вход которого подключен к выходу восьмого элемента И управления, а его выход - к управляющему входу пятнадцатого элемента И управления и к счетному Входу второго счетчика, разрядные выходы которого связаны с входами пятнадцатого элемента И управления; третий вход двенадцатого элемента И управления подключен к выходу тринадцатого триггера управления, вход установки в i которого подключен через тринадцатый элемент задержки к выходу первого блока временной задержки, а вход установки в О - к входу обнуления первого счетчика.

Источники инфopмaц 5и/ принятые- во внимание при эксперт зе

1. Авторское свидетельство СССР №446952, кл. Я 03 К 23/26, 1972.

2. Авторское свидетельство СССР № 377797, кл. G Об G 7/14, 1971 3, Авторское свидетельство СССР № 518768, кл. G 06 F 7/50, 1974 : (прототип) . 1111111111111111111111111111Ш1111111111111111111111 1111111ШШ111111ШШ IIIUMI IMIll .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для дифференцирова-Ния чАСТОТы СлЕдОВАНия иМпульСОВ | 1978 |

|

SU798881A1 |

| Устройство для суммирования импульсных последовательностей | 1974 |

|

SU518768A1 |

| Преобразователь цифрового кода в частоту следования импульсов | 1976 |

|

SU738158A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| Устройство для преобразования графической информации | 1982 |

|

SU1140148A1 |

| Устройство для дифференцирования частоты повторения импульсов | 1974 |

|

SU525117A1 |

| СПОСОБ УПРАВЛЕНИЯ ЧАСТОТНЫМ АСИНХРОННЫМ ЭЛЕКТРОПРИВОДОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2081503C1 |

| Преобразователь угла поворотаВАлА B КОд | 1979 |

|

SU840992A1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ ЦИФРОВОГО СИГНАЛА ИЗОБРАЖЕНИЯ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2004 |

|

RU2287909C2 |

Авторы

Даты

1980-01-25—Публикация

1977-09-20—Подача