(54) УСТРОЙСТВО ДЛЯ ДИФФЕРЕНЦИРОВАНИЯ ЧАСТОТЫ ПОВТОРЕНИЯ ИМПУЛЬСОВ

первый элемент задержки соединен с первым входом третьего триггера управления и выходом пятого элемента И, подключенного входами соответственно к входу устройства и второму выходу формирователя стрббов, причем второй вход третьего триггера управления, соединенного выходами с входами управления реверсом первого счетчика, подключен к выходу этого счетчика, поразрядные выходы которого через первую группу элементов И переноса соединены с входами регистра, выходы кото рого через вторую группу элементов И переноса соединены с поразрядными входами второго счетчика, подключенного выходом к управляющему входу второй группы элементов И переноса и первому входу множительно-делительного блока, второй вход которого соединен с вторым входом четвертого элемента И, подключенного выходом к выходу четвертого триггера управления, входу обнуления регистра, и через второй и третий элементы задержки соответственно к входу обнуления первого счетчика и управляющему входу первой группы элементов И переноса, а третий вход множителыю-дел11тельного блока подключен через умножительч частоты к первому выходу число-импульсного запоминающего блока, причем выход четвертого триггера управления соединен с вторым входом второго элемента И, подключенного выходом к счетному входу второго счетчика.

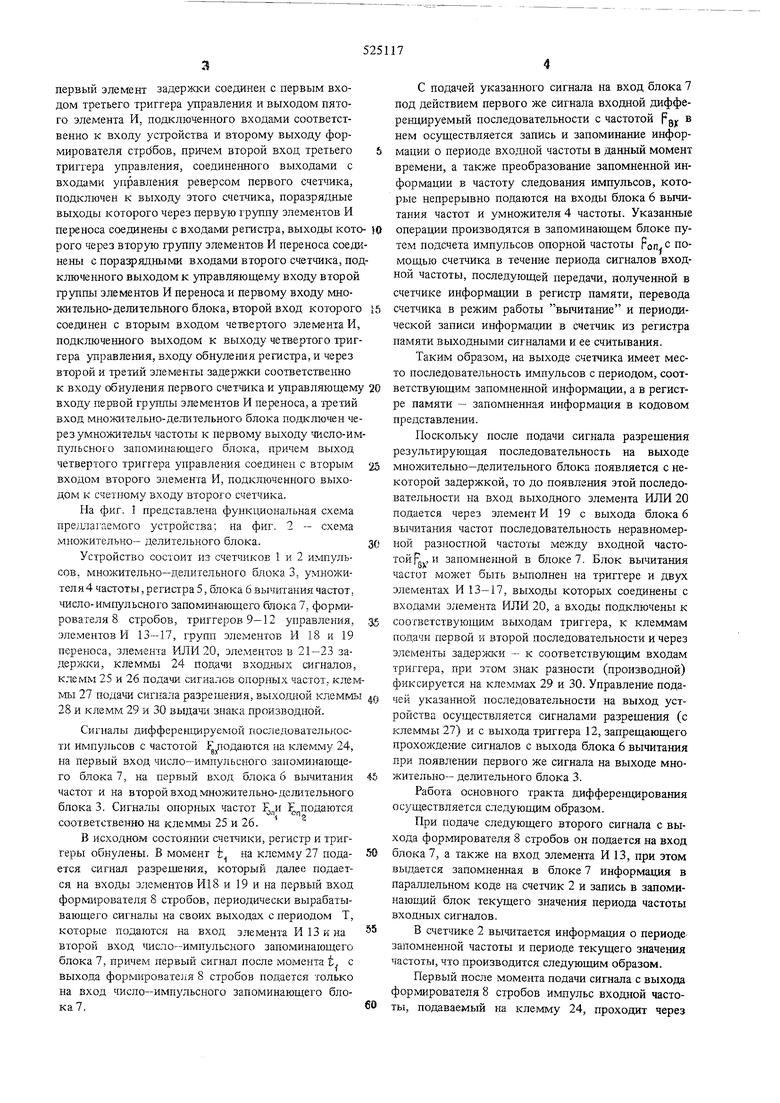

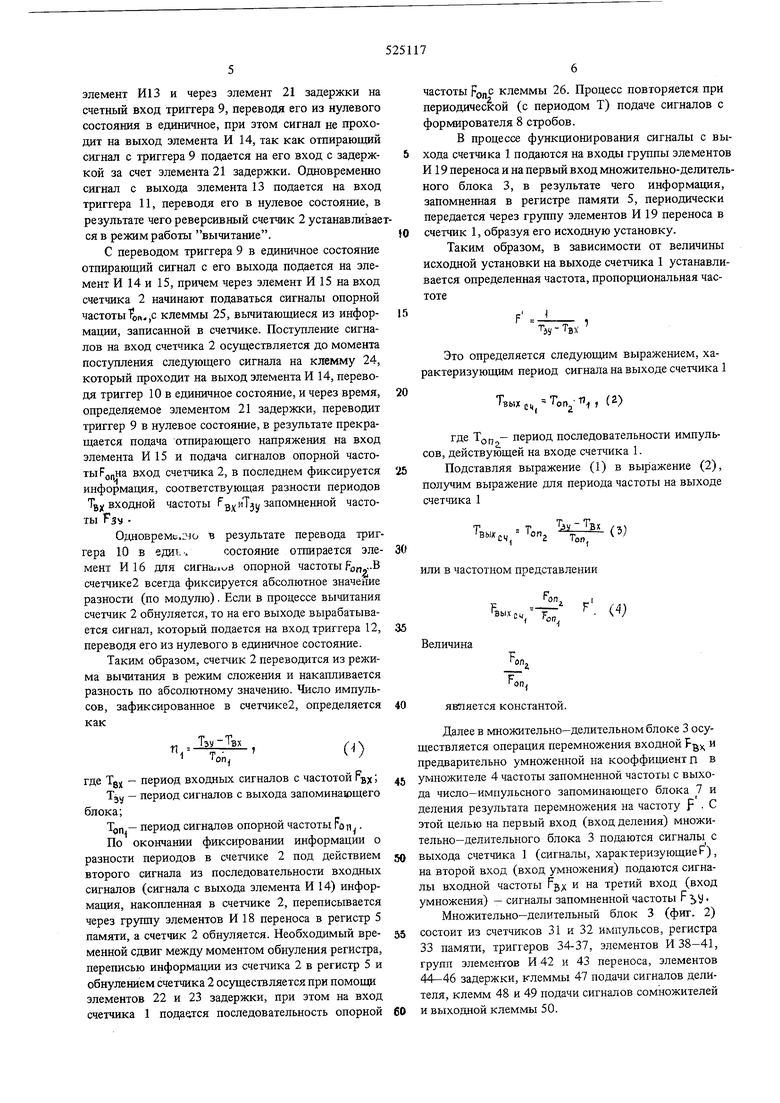

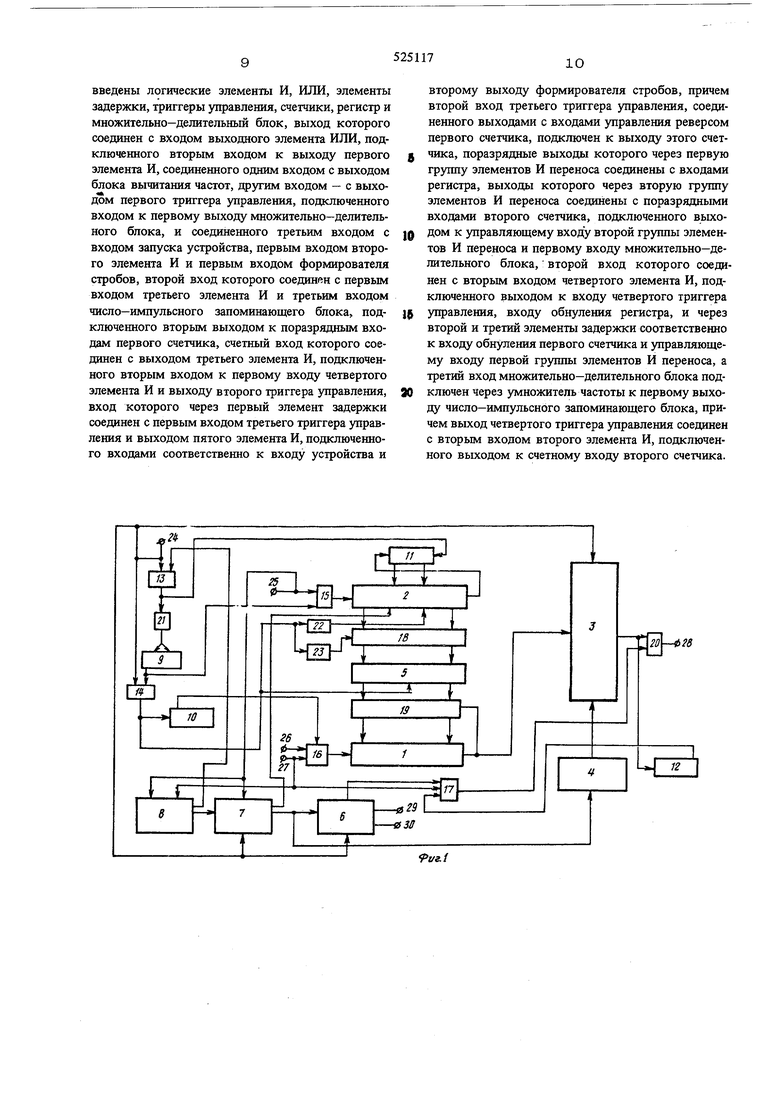

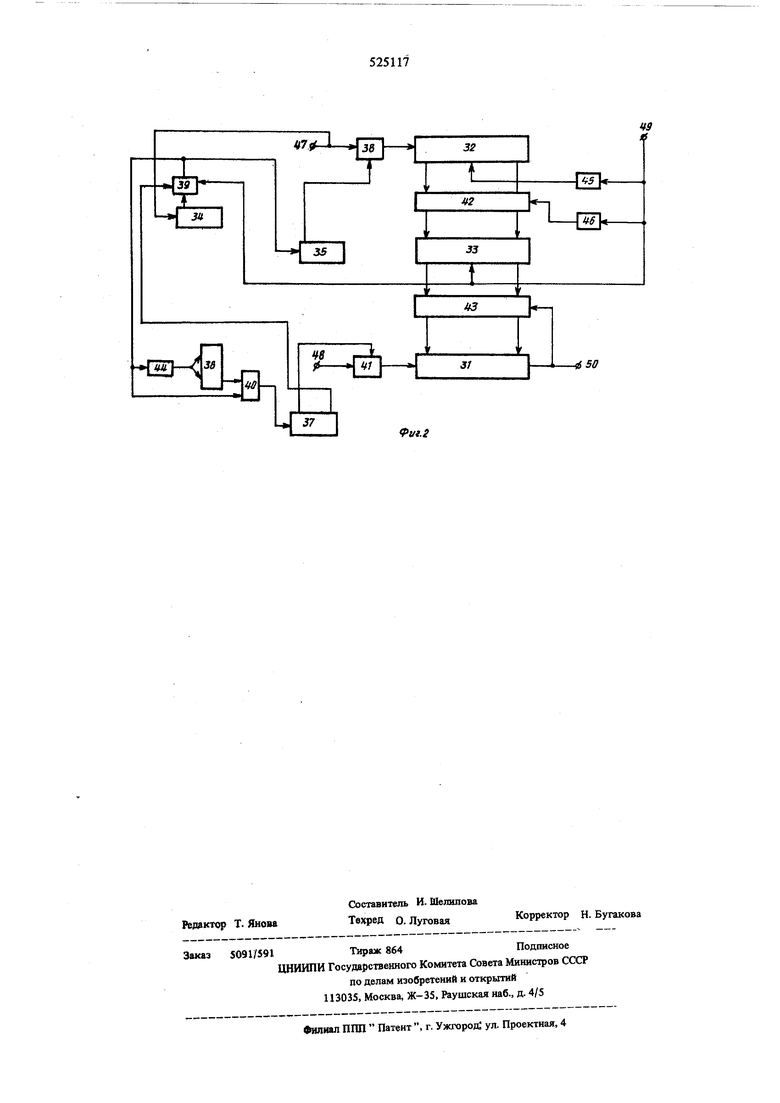

На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 схема множительно- делительного блока.

Устройство состоит из счетчиков 1 и 2 импульсов, множительно--целительно го блока 3. умножителя4 частоты, регистра 5, блока 6 вычитания частот, число-импульсного запоминающего блока 7, формирователя 8 стробов, триггеров 9-12 управления, элементов И 13-17, групп элементов И 18 и 19 переноса, элемента ИЛИ 20, элементов в 21-23 задержки, клеммы 24 подачи входных сигналов, клемм 25 и 26 подачи сигналов опорных частот, клеммы 27 подачи сигнала разрешения, выходной клемгльг 28 и клемм 29 и 30 выдачи знака производной.

Сигналы дифференцируемой гюследовательности импульсов с частотой .подаются на клемму 24, на первый вход число-импульсного запоминающего блока 7, на первый вход блока 6 вычитания частот и на второй вход множительно-делительного блока 3. Сигналы опорных частот Y.fi подаются соответственно на клеммы 25 и 26.

В исходном состоянии счетчики, регистр и триггеры обнулен-Ы. В момент t на клемму 27 подается сигнал разрещения, который далее подается на входы элементов И18 и 19 и на первый вход формирователя 8 стробов, периодически вырабатывающего сигналы на своих выходах с периодом Т, которые подаются на вход элемента И 13 и на второй вход число-импульсного запоминающего блока 7, причем первый сигнал после момента t, с выхода формирователя 8 стробов подается только на вход число-импульсного запоминающего блока 7.

С подачей указанного сигнала на вход блока 7 под действием первого же сигнала входной дифференцируемый последовательности с частотой pgjf в нем осуществляется запись и запоминание информапии о периоде входной частоты в данный момент времени, а также преобразование запомненной информации в частоту следования импульсов, которые непрерывно подаются на входы блока 6 вычитания частот и умножителя 4 частоты. Указанные операции производятся в запоминающем блоке путем подсчета импульсов опорной частоты РоПх с помощью счетчика в течение периода сигналов входной частоты, последующей передачи, полученной в счетчике информации в регистр памяти, перевода счетчика в режим работы вычитание и периодической записи информации в счетчик из регистра памяти выходными сигналами и ее считывания.

Таким образом, на выходе счетчика имеет место последовательность импульсов с периодом, соответствующим запомненной информации, а в регистре памяти - запомненная информация в кодовом представлении.

Поскольку после подачи сигнала разрешения результирующая последовательность на выходе множительно-делительного блока появляется с некоторой задержкой, то до появления этой последовательности на вход выходного элемента ИЛИ 20 подается через элемент И 19 с выхода блока 6 вычитания частот последовательность неравномерной разностной частоты между входной частотой pgj, и запомненной в блоке 7. Блок вычитания частот может быть в.ыполнен на триггере и элементах И 13-17, выходы которых соединены с входами элемента ИЛИ 20, а входы подключены к соответствующим выходам триггера, к клеммам подачи первой и второй последовательности и через элементы задеряжи - к соответствующим входам триггера, при этом знак разности (производной) фиксируется на клеммах 29 и 30. Управление подачей указанной последовательности на выход устройства осуществляется сигналами разрешения (с клеммы 27) и с выхода триггера 12, запрещающего прохождение сигналов с вьгх.ода блока 6 вычитания при появлении первого же сигнала на выходе множительно- делительного блока 3.

Работа основного тракта дифференцирования осуществляется следующим образом.

При подаче следующего второго сигнала с выхода формирователя 8 стробов он подается на вход блока 7, а также на вход элемента И 13, при этом выдается запомненная в блоке 7 информация в параллельном коде на счетчик 2 и запись в запоминающий блок текущего значения периода частоты входных сигналов.

В счетчике 2 вычитается информация о периоде запомненной частоты и периоде текущего значения частоты, что производится следующ им образом.

Первый после момента подачи сигнала с выхода формирователя 8 стробов импульс входной частоть, подаваемый на клемму 24, проходит через элемент И13 и через элемент 21 задержки на счетный вход триггера 9, переводя его из нулевого состояния в единичное, при этом сигнал не проходит на выход элемента И 14, так как отпирающий сигнал с триггера 9 подается на его вход с задержкой за счет элемента 21 задержки. Одновременно сигнал с выхода элемента 13 подается на вход триггера 11, переводя его в нулевое состояние, в результате чего реверсивный счетчик 2 устанавливае ся в режим работы вычитание. С переводом триггера 9 в единичное состояние отпирающий сигнал с его выхода подается на элемент И 14 и 15, причем через элемент И 15 на вход счетчика 2 начинают подаваться сигналы опорной частоты оп-,с клеммы 25, вычитающиеся из информации, записанной в счетчике. Поступление сигналов на вход счетчика 2 осуществляется до момента поступления следующего сигнала на клемму 24, который проходит на выход элемента И 14, переводя триггер 10 в единичное состояние, и через время, определяемое элементом 21 задержки, переводит триггер 9 в нулевое состояние, в результате прекращается подача отпирающего напряжения на вход элемента И 15 и подача сигналов опорной частоты вход счетчика 2, в последнем фиксируется информащ1я, соответствующая разности периодов Tgy входной частоты запомненной частоты ГЗУ Одновремс.1чо в результате перевода триггера 10 в едиь..состояние отпирается элемент И 16 для сигналов опорной частоты Рд,, -.В счетчике2 всегда фиксируется абсолютное значение разности (по модулю). Если в процессе вычитания счетчик 2 обнуляется, то на его выходе вырабатывается сигнал, который подается на вход триггера 12, переводя его из нулевого в единичное состояние. Таким образом, счетчик 2 переводится из режима вычитания в режим сложения и накапливается разность по абсолютному значению. Число импульсов, зафиксированное в счетчике2, определяется как где Tgj( - период входных сигналов с частотой Fgjj; Tji - период сигналов с выхода запоминающего блока; Топ - период сигналов опорной частоты Fon,. По окончании фиксировании информации о разности периодов в счетчике 2 под действием второго сигнала из последовательности входных сигналов (сигнала с выхода элемента И 14) информация, накопленная в счетчике 2, переписывается через группу элементов И 18 переноса в регистр 5 памяти, а счетчик 2 обнуляется. Необходимый временной сдвиг между моментом обнуления регистра, переписью информации из счетчика 2 в регистр 5 и обнулением счетчика 2 осуществляется при помощи элементов 22 и 23 задержки, при этом на вход счетчика 1 подается последовательность опорной (-i частоты РОП клеммы 26. Процесс повторяется при периодической (с периодом Т) подаче сигналов с формирователя 8 стробов. В процессе функционирования сигналы с выхода счетчика 1 подаются на входы группы элементов И19 переноса и на первьш вход множительно-делительного блока 3, в результате чего информация, запомненная в регистре памяти 5, периодически передается через группу элементов И 19 переноса в счетчик 1, образуя его исходную установку. Таким образом, в зависимости от величины исходной установки на выходе счетчика 1 устанавливается определенная частота, пропорциональная частотеТзг вхЭто определяется следующим выражением, характеризующим период сигнала на выходе счетчика 1 где TQ - период последовательности импульсов, действующей на входе счетчика 1. Подставляя выражение (1) в выражение (2), получим выражение для периода частоты на выходе счетчика 1 или в частотном представлении оп, 1 Величина является константой. Далее в множительно-делительном блоке 3 осуествляется операция перемножения входной F-g, и редварительно умноженной па кооффициентп в множителе 4 частоты запомненной частоты с выхоа число-импульсного запоминающего блока 7 и еления результата перемножения на частоту р . С той целью на первый вход (вход деления) множиельно-делительного блока 3 подаются сигналь с ыхода счетчика 1 (сигналы, характеризующие), а второй вход (вход умножения) подаются сигнаы входной частоты и на третий вход (вход множения) - сигналы запомненной частоты . Множительно-делительный блок 3 (фиг. 2) остоит из счетчиков 31 и 32 импульсов, регистра 3 памяти, триггеров 34-37, элементов И 38-41, рупп элементов И 42 и 43 переноса, элементов 4-46 задержки, клеммы 47 подачи сигналов делиеля, клемм 48 и 49 подачи сигналов сомножителей выходной клеммы 50. После появления первого же сигнала на выходе счетчика, подаваемого на клемму 47 множитель но- делительного блока 3, триггер 34 переводится из нулевого в единичное состояние, при этом первый же после момента перевода триггера 34 импульс входной частоты, подаваемый на клемму 49,связанную с клеммой 24 устройства для дифференцирования, проходит через элемент И 39, переводит триггеры 35 и 36 в единичное состояние. В результате перевода триггера 35 в единичное состояние отпирается элемент И 38 для сигналов, подаваемых на клемму 47, которые начинают проходить на вход счетчика 32. С поступлением на клемму 49 следующего сигнала входной дифференцируемой частоты, информация, накопленная в счетчике 32, передается через группу элементов И 42 переноса в регистр 33 памяти, где запоминается, а счетчик 32 обнуляется. Необходимый временный сдвиг между моментами передачи информации и обнулением счетчика 32 осуществляется с помощью элементов 45 и 46 задержки. Далее процесс повторяется. С приходом каждого последующего импульса из входной последовательности с частотой F-Q происходит обнуление регистра 33 памяти, а также передача накопленной в счетчике 32 информации в регистр памяти и обнуление счетчика 32. Необходимая задержка в подаче сигналов на вход счетчика 31 осуществляется следующим образом. Второй после подачи разрещающего сигнала с выхода триггера 34 сигнал с частотой FBX проходит через элементы И 39 и 40 и переводит триггер 37 в единичное состояние, в результате от пирается элемент И 41 для прохождения на вход счет чика 31 сигналов с частотой РЗУ П подаваемых на клемму 48 с выхода умножителя 4 частоты устройства для дифферецирования. Сигналы с выхода счетчика 31, который работает в режиме вычитания, подаются на выходную клемму 50, образуя последовательность импульсов, характеризующую окончательный результат. Наряду с этим, сигналы с выхода счетчика 31 подаются на управляющие входы груп пы элементов И 43 переноса и на вход триггера 12 устройства для дифференцирования. В результате этого первьш же сигнал с выхода счетчика 31 переводит триггер 12 устройства для дифференц рования в единичное состояние, что приводит к запиранию элемента И 19. С выхода блока 6 вычитания частот сигналы разностной частоты проходят на выход устройства до момента появления сигналов на выходе счетчика 31 множительно-делительного блока З.Кроме того, осуществляется периодическая передача информации из регистра памяти 33 в счетчик 31, которая является его исходной установкой. Таким образом в зависимости от величины исходной установки на выходе счетчика 31 устанавливается вполне определенная частота, которая хаактеризует собой окончательньш результат множиельно-делительной операции. Количество импульсов, поступающих в течение ериода последовательности с частотой вход четчика 32, с учетом выражения (3), определяется Твх вх, Твя Топ, Т1 - (Тз,.Т,, оо гдеТвьи(5,- период следования сигналов с выхода счетчика 1 устройства для дифференцирования, подаваемых на клемму 47 множительно-делительного блока. Период последовательности импульсов на выходе счетчика 31 множительно-делительного блока определяется выражением 7 -2яЛг - Тгу TBX Ton - т1(Тау-Твх -Топ2 где -i2 период последовательности импульсов на выходе умножителя 4 частоты устройства для дифференцирования, подаваемых на клемму 48 множительно-делительного блока, или в частном представлении является постоянной. Для получения правильного результата ее слеует приравнять единице, откуда onrFo В результате реализации выражений (7) и (8) с учетом равенства ТЗУ-ТВХ в предложенном устройстве реализуется операция дифференцирования входной величины, представленной в виде частоты следования импульсов, так как имеет место вычитание через определенные интервалы времени Т текущего значения входной частоты и запомненной частоты в предьщущем интервале времени. Формула изобретения Устройство для дифференцирования частоты повторения импульсов, содержащее умножитель частоты и блок вычитания частот, соединенный первым входом с входом устройства и с первым входом число-импульсного запоминающего блока, а вторым входом подключенный к первому выходу число-импульсного запоминающего блока, второй вход которого соединен с первым выходом формирователя стробов, OJличaющeecя тем, что с целью повышения точности, в него дополнительно

введены логические элемеиты И, ИЛИ, элементы задержки, триггеры управления, счетчики, регистр и множительно-делительный блок, выход которого соединен с входом выходного элемента ИЛИ, подключенного вторым входом к выходу первого элемента И, соединенного одним входом с выходом блока вычитания частот, другим входом - с выходом первого триггера управления, подключенного входом к первому выходу множительно-делительного блока, и соединенного третьим входом с входом запуска устройства, первым входом второго элемента И и первым входом формирователя стробов, второй вход которого соединен с первым входом третьего элемента И и третьим входом число-импульсного запоминающего блока, подключенного вторым выходом к поразрядным входам первого счетчика, счетный вход которого соединен с выходом третьего элемента И, подключенного вторым входом к первому входу четвертого элемента И и выходу второго триггера управления, вход которого через первый элемент задержки соединен с первым входом третьего триггера управления и выходом пятого элемента И, подключенного входами соответственно к входу устройства и

второму выходу формирователя стробов, причем второй вход третьего триггера управления, соединенного выходами с входами управления реверсом первого счетчика, подключен к выходу этого счетчика, поразрядные выходы которого через первую группу элементов И переноса соединены с входами регистра, выходы которого через вторую группу элементов И переноса соединены с поразрядными входами второго счетчика, подключенного выходом к управляющему входу второй группы элементов И переноса и первому входу множительно-делительного блока, второй вход которого соединен с вторым входом четвертого элемента И, подключенного выходом к входу четвертого триггера

управления, входу обнуления регистра, и через второй и третий элементы задержки соответственно к входу обнуления первого счетчика и управляющему входу первой группы элементов И переноса, а третий вход миожительно-делительного блока подключен Через умножитель частоты к первому выходу число-импульсного запоминающего блока, причем выход четвертого триггера управления соединен с вторым входом второго элемента И, подключенного выходом к счетному входу второго счетчика.

Т j-нй/, Мзtf3 tf Ч

Авторы

Даты

1976-08-15—Публикация

1974-12-19—Подача