тов и переноса подключены к выходу чет вертого счетчика, ко входу пятого триггера управления и первому входу шестого эл&мента И управления, соединенного выходо%1; со входом второго счетчика, а вторым входом - с выходом шестого триггера управления, вход кбтброгЬ. подключен к выходу первого элемент И уцрйвления, соединенного входами с выходами пятого и седьмого триггеров;У111|равяения, и пощслкх чей к первому входу седьмого элемента И управления и через поспедйватёльно соепиненные шестой элемент задержки и восьмой триггер управления подключен ко второму входу седьмого элемента И уИравл няя, соединенного вь ходом со вхооом седьмого триггера управления, второй выход которого подключен ко входу воськюго элемента И управления, соединенного выходом со счетным входом первого счет чика, причем счетные входы третьего и четвертого счетчнков соединены соответ. ственно с выходами девятого элемента И управления, соединенного входом с выходом третьего элемента ИЛИ, н десятого элемента И управления, первый вход которого подключен к выходу второго тригг&ра управления, а второй вход - ко входу запуска устройства, второму входу второго элемента И управления и входу одиннадцатого элемента И управления, другие входы которого соединены с выходом второго элемента ИЛИ. и выходом первого триггера управления, а выход одиннадцато-го элемента И управления соединен со вторым входом первого элемента ИЛИ, причем вход второго слагаемого соединен с соответствующими входами третьего, пятого, двенадцатого элементов И управления и третьим входом второго элемента ИЛИ, выход второго элемента И управления через последовательно соединенные седьмой элемент задержки и девятый триггер управления подключен ко второму входу четве{ того элемента И управления и входу треть го элемента ИЛИ, второй вход которого соединен со входом пятого элемента И управления и выходом десятого триггера управления, подключенного входом через . восьмой элемент задержки к выходу двена к цатого элемента И управления, а второй вход третьего триггера управления, соеди, ненного выходом со входом двенадцатого элемента И управления, подключен к выxoд четвертого элемента И управления и второму входу четвертого триггера управл - нкя, вьход. которого соединены с соотве-рствуюшими входами второго и двенадцатого элементов И управления, а выход треть.го элемента И управления соединен со вхо- дом второго элемента задержки.

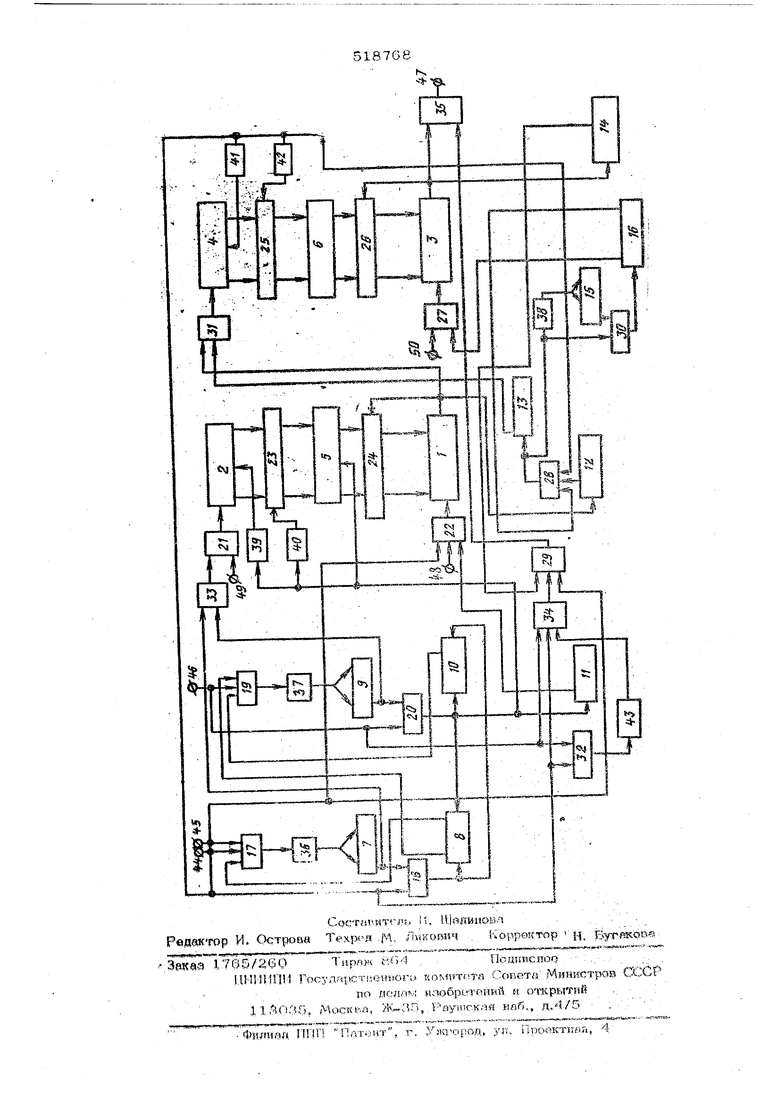

На чертеж представлена функциональная схема устройства для суммирования нмпупьсных последовательностей. « Устройство состоит из счетчиков импульсов 1-4, регистров памяти 5, 6, триггеров управления 7-16, элементов И управления 17-22, групп элементов И переноса 2326, элементов И управления 27-32, элементов ИЛИ 33-35, элементов задержки 36-43, клемм подачя сигналов 44-50.

В процессе функционирования устройства реализуется следующее выражение:

Tt

а.

i-V

Т. . Т,

18

U)

р1

где

F. - частота, е,

а;

Т, - период соответствующей импульсной последовательности.

Значение F получается с помощью ; счетчиков 1, 2, регистра 5,jа такжелоги.ческих элементов для управления сигналами на входах счетчиков 1, 2. Выражение же (1) в цепом реализуется на счетчиках 3, 4, регистре памяти 6 и других логи-i чёских элементах; cnyjkiaumx для управления

0 соответствующими сигналами. Сначала опишем работу части устройства, предназначенной для получения величины F . Сигналы первой последовательности с частотой следования Fj , характеризующие одно из. слагаемых, подаются на клемму 44.

Сигналы второй последовательности, характеризующие второе слагаемое, подаются на клемму 46. Сигналы опорных чаотот F(j и FO подаются соответсть. венно на клеммы 49 и 48. Причем частота в оОшем случае превышает чаото тур- в несколько раз. В исходном состоянии счетчики 1-4, регистры памяти 5, 6, и триггеры управления Ьбнупены. |В момент ti на клемму 45 подается сиг

5 нал разрешения. Пр этом первый после момента tj импульс, подаваемый на клемму 44, проходит через элемент И управления Д7, и через элемент задержки 36 на счетный вход триггера управления 7,переъопя его из нулевого в единичное состояние. Очевидно, что при этом сигнал не . проходит на выход. элемента И управления : 18, так как отпирающий сигйал с триггера 7 подается на его вход с задержкой , ;за счет элемента задержки 36. С переводом триггера 7 в единичное состояние от пираюший сигнал с его выхода подается ;на вход элемента И управления 18 и че

рез элемент ИЛИ 33 на вход элемент а И управ. (пения 21. При этом через элемент И управления 21 на счетный вход счетчика 2 {Начинают подаваться сигналы опорной час;готы Р( , которые выполняют функцию ;эаполненвя периодов входных сагвалов.

Очевидно, что частота должна быть

Г,

l6onbuie частот R

в несколько раз.

Заполнение периода частоты Ь locyuitecTBnaется до момента поступлення следующего сигнала на клемму 44. .

При поступлении следующего сигнала 1иа клемму 44 этот снгиал проходит на вы ход элемента И управления 18, переводя триггер управления 8 в единичное состо|Яние, и через; время, определяемое элеме |том задержки 36, переводит триггер управ ления 7 в нулевое состояние. В результате. прекращается подача отпирающего напряже ния .на вход элемента И управления 21, а 1 так же сигналов опорной частоты ly., иа

i вход счетчика 2 в и нем фиксируется и формация, соответствующая периоду Tj| . Одновременно в результате перевода триг гера 8% единичное состояние открывавiv1ся элемент И управления 19 для сигналов iBTopoft последовательности с частотой R и запирается элемент И управления 17 для сигналов с частотой F . Первый после момента отпиранйй элемента И управления 19 сигнал из последовательности с часто той Fj проходит через элемент И 19 и элемент задержки 37 на счетный вход триггера управления 9, переводя его из :нулевого в единичное состояние. В резуль« |тате; отпирающий сигнал с выхода триггера управления 9 подается на вход элемента И управления 2О и через элемент ИЛИ вход элемента И 21.

При этом через элемент И 21 на вход счетчика 2 начинают подаваться сигналы

опорной частоты F,

который суммируoHj

ются ,с ранее накопленной в счетчике 2 информацией о периоде сигналов частотыF..

Заполнение периода сигналов второй 1последовательности.с частотой F, осуществляется до момента поступления следу|юшего сигнала на клемму 46. При поступ ленил сигнала на указанную клемму он проходит на выход элемента И управления ;2О, переводя триггеры управления 3-0 и ill в единичное состояние и тригге|) 8-в |Нулевое, и через время, (определяемое эле (ментом задержки 37, переводит триггер 9

IB нулевое состояние.

В результате отпирается элемент И : управления 17 для прохождения icHrjianoBv; с частотой элемент И управления 22

I для прохождения сигналов с частотой FQ,,; |на счетный вход счетчика 1 и запирается элемент И управления 21 для прохождения

яа счетный вход счетчика 2 сигналов ondp. ной частоты с частотой РОИ . Таким o6pai- зом, всчетчике 2 (Цксируется информвоия о сумме двух периодов Tj, . ,

Число имщгяьсов, зафиксированное в ечетчике 2, определяется как

Са.)

где Та.,,

.ои. - период сигналов опорной час

: ;-.. . Т РО

тоты РОЧ

Информация, накопленная в счетчике 2, переписывается в регистр памяти 5 и в счетчик 1 через элементы И переноса 23. ; Далееописанный выше процесс получения инфортлации .в счетчике 2 о сумме /двух периодов слагаемых частот повторе- ется. При этом сигналы с выхода счетчи ка 1 подаются на вход элемента И управ ления 31, на вход триггера управления 12 и на I управляющие входы элементов И переноса 24; В результате этого информация, содержащаяся в регистре памяти 5, периодически передается через элементы И носа 24 в счетчик 1, образуя его исходную уставку. Таким образом, в зависимоОти от величины исходной уставки;на счетчика 1 устанавливается вполне определенная частота, которая пропорциональна частоте.

1 -. /

р1.

Т, 4 Т

1 2

Это определяется следующим образом.

Период последовательности импульсов v на выходе счетчика 1 определяется вы{)в женнем.

(3)

Т ,

К

ей.

)

где TOV - период последовательности импульсов,Тце14ствующей на входе счетчн-.

квД. -.,. .,.,... . : Подставляя (2) в (3),

Т.Т,

(4)

ОТ1,

.СЧ. ,

on.

или в частотном представлении

,i

-.pl

(5)

ы.сЧ.

F,

оИ

,

(является констанВеличина

гои I той.

После появления первого же сигнала : на выходе счетчика 1 триггер 12 переводится нз нулевого в единичное состояние. При этом первый после момента перевода триггера 12 импульс, подаваемый Ьакпек -: му 44, йроходит через элемент И упрйв-Г Ленин 28, переводит триггер 13 и с зад&ржкой триггер 15 в единичное состояние. В результате перевода триггера 13 в единичное состояние отпирается элемент И управления 31 для сигналов с выхода счетчика 1, которые начинают проходить на счетный вход счетчика 4.

С поступлением на,яяёйк у 44 следующего сигнала нвформацня ч-нак;опленная в счетчике 4, передаетрч черве элеме. ты И переноса 25 а.jpefiacTp памяти 6 к в очетчнк 3, где запоминается, а 4 обнуляется. Необхошгмый временной сдвиг между моментами передачи ннформаоин к обнулением сЧетчнка 4 осушествляется с помошью элементов зддерж ки 41, 42. Далее процесс повторяется.

С приходом каждого последующего км-: пульса из последовательности с частотой следования 1Р осуществляется обнуление регистра памяти 6 я счетчика 3, а также передача накоплеТшбй в счетчике 4 инфор-/ мации в регистр памяти 6:и обнуление счетчика 4. НеоВходимая задержка в сигналов на вход счетчика 3 осуществляется следующим образом. Второй поо-яе подачн разрешающего сигнала с вмхода триггера 12 сигнал с частотой fj проходит через элемент И управления 30 и переводит триггер 16 в единичное состояние. В результате отпирается элемент И управления 27 для прохождения на вход счетчика 3 сигналов с частотой F, ,умноженной в общем случаена коэффициент умнбжения и. , и запирается элемент И управления 28.

Сигналы с выхода счетчика 3 подаются через элемент ИЛИ 35 на выходную клем му 47, образуя последовательность импульсов, характеризующую окончательный резултат, а также на вход триггера 14 и на управляющие входы элементов И переноса 26. В результате этого первый же сигнал с выхода счетчика 3 :Переводит трнггер 14 в единичное состояние, что приводит к запиранию элемента И 29 для CHINналов двух последовательностей, которые определяли сумму при неравномерном раопределенни до момента появления сигналов на выходе счетчика 3.

Наряду с этим осуществля1ется периоди ческая передача информации из регистра памяти 6 в счетчик 3, которая является его исходной уставкой. . Таким образом, , в зависимости от величины исходной уставки на выходе счетчика 3 устанавливается вполне определенная частота, которая хара теризует собой окончательный результат. Следует отмет ить, что каждый последующий импульс частоты Fj осуществляет периодический сброс старой информации в югистре 6 и запись новой информации.

Количество имтжульсов, поступивших в течение периода последовательности с чвитотой Fj на вход счетчика 4, с учетом (4) определяется как

.,.

10

ои.

Период последовательности импульсов ;яа выходе счетчгаеа 3 определяется выра«жеяием;

ТУ .-t.-nt .

М. . «Wi-y-T 7) ИЛИ В частотном преоставпении

lWK.р1 . -р

си.

Ш

Величина К . ..Л.- . является постойй в г, :ной я для получения правильного ре льтата ее следует приравнять единице.

Таким образом, на выходе устройства 80 имеет место результат суммирЬваниЯ двух последовательностей с равномерным рвх Определением выходных сигналов.

Ф о р м у л а и 3 о б р е т е в и я

Устройство для суммирования импульсных последовательностей, содержащее элементы задержки, логические элементы

ИЛИ и счетчики импульсов выход перво-: го из Которых соединен с первым входом : первого элемента И ЛИ, а вход обнуления

второго счетчика соединен с выхрдомнер вого элемента задержки, выход второго

элемента задержки подключён к первому входу второго «лемецта ИЛИ, о т л я ч ю щ е е с я тем, что, с целью повышения точности и быстродействия работы /устройства, в-него дополнительно введенц

триггеры управления, логические элементы И переноса и управления и два per :стра, входы и выхо(ы первого на которых ;соответственно через первую и вторую группы элементов И переноса соединены :

,С выходами второго и входами первого ;ечетчиков, а входы и выходы второго регистра .Соответственно через третью и четвертую .группы элементов И переноса соединены , с выходами третьего и входами четверто;го счетчиков, управляющие входы первой

1группы элементов И переноса через элемент задержки подключеяьг ко первого спагаем6го, ко входу первого злемента задержки,k первым входам пера;вого, второго, третьего, и Четвертого элеП|ментов И управпення я вто мувходу второго элемента ИЛИ, управпяюпше входы второй группы элементов И переноса подклк ены к выходу первого счетчика и входу первого триггера управления, управля1юшне входал третьей группы элементов И I переноса через четвертый элемент задерткI ЕЙ соединены со входом обнуления второ-; jro регистра, с первыми входами второго, третьего и четвертого триггеров управлв ния, с выходом пятого элемента И управ |ления и входом пятого элемента аадержха, выход которого соешнен со входом обну |ления третьего счетчика, управл ошие i входы четвертой группы элементов И пере iHoca подключены к выходу 4etBepToro c4eiw |чика, ко входу пятого триггера управле8Я«1 |н первому входу шестого элемента Ц управления, соединенного выходом со вкр.. дом второго счетчика, а вторым входом |с выходом шестого триггера управления, вход которого подключен к выходу первого элемента И управления, соединенного 1 входами с выходами пятого и седьмого триггеров управления, и подключен к первому входу седьмого элемента И управления и через последовательно соеДивеыные шестой элемент задержке и восьмой триг |гер управления подключен ко второму седьмЬг6; элемента И управления соединенного выходом со входом трщ герй управления, второй выход которого подключен ко входу восьмогоалемешга И Цуправлёния, соедивенного выходом со счет ным входом первого с четчика, првЧём

счетные входы третьего и чете ртого сче чиков соединены соответственно с вьгходамн девятого элемента И управления, соединенного входом с выходом третьего элемет-а ИЛИ, и десятого элемента И управления, первый вход которого подклк чен к выходу второго триггера угц; авлений,: в второй вход - ко входу запуска устрой-i ства, BTxipoiyfy входу второго элемеита И ; управления я входу одиннадцатого элемен ;та И(Управления, другие входы которого ; соединены с выходом второго элемента ИЛИ я выхооом иервогр триггера упра&- : певкя, а выход одивиадоатого ;элемеита И, управления соединев to вторым {входом j первого элемента ИЛИ, причем вход второго слагаемого соединен с соответствующими входами третьего, пятого, двена : яатсях) алемеатов И управления и третьим уходам BTOfioro элемеата ИЛИ, выход вто рого 971ементв И yopaaiieraia через прслд4 {ювательяо соединенные сеоьмой элемент; задержки и девятый тртггвр управления подключен ко STopaJviy входу четвертого элемента И управления и входу третьего элемента ИЛИ, второй вход которого со-;

8 единен со входом пятого элемента Иуправ-« левия и выходом десятого триггера управ, Ленин, подключенного входом через вось-. мой элемент задержки к выходу двенадца того элемента И управления, а второй вход третьего триггера управления, соединенного выходом со входом двенадцатого; эаемента И управления, подключен к вы-: : ходу четвертого элемента И управления и; ртороМу входучетвертого триггера управ яения, выходы которого соединены с . ответствукяцимн входами второго и двенадаатого элеменггов И управления, а вык ход третьего элемента И управлении соединен со входом второго элемента зааерж- 1ки., .

0

Авторы

Даты

1976-06-25—Публикация

1974-05-15—Подача