i

Изобретение относится к автоматическим системам регулирования и управления работой оборудования.

Известен программно-логический регулятор, воспринимающий информацию от двухпозиционных датчиков и формирующий на основе анализа этой информации управляющие сигналы для исполнительных механизмов 1j. В состав регулятора в качестве основных блоков входят: блок памяти программ, блок ввода информации и блок вьшода управляющих сигналов. Блоки ввода и вывода содержат устройства преобразования и коммутации сигналов.

Наиболее близким по технической суш- ,ности к предложеннокту изобретению является программночлогический регулятор, который содержит генератор тактовых импульсов, блок памяти программ, состоящий из счётчика команд, запоминающего блока, регистра команд и блока команд условного перехода, логический операционный блок, а также блоки ввода и вывода информации, состоящие каждый из

входного (выходного) коммутатора и блоков согласования и нормирования входных и выходных сигналов соответственно р, Генератор тактовых импульсов подключен к синхронизирующим входам счетчика команд и других блоков, входящах в устройство. Счетчик команд п.одключен к запоминающему устройству, выход которого подключен к регистру команд. Регистр команд в свою очередь . подключен к входному коммутатору, вььходному коммутатору, логическому операционному блоку и к первому входу уст-, ройства команд условного перехода.. Входной коммутатор по входу соединен с уст5ройством согласовани я и нормирования блока ввода информации, а по выходу с логическим операционным блоком. Выходной коммутатор соединен с устройством согласования и нормирования блока вывода информации. Выход логического операционного блока подключен к информационному входу устройства.согласования и нормирования блока вывода информации и ко второму входу устройства комчнд условного перехода, выход которого подключен к счетчику команд блока памяти программ.

Недостатком известного рег-улятора является низкое быстродействие и большой объем запоминающего устройства.

Цель изобретения - повышение бьгстроействия программно-логического регуляора и снижение требуемого объема памяти запоминающего устройства.

Поставленная цель достигается тем, то программно-логический регулятор. одержащий последовательно соединенные енератор тактовых импульсов, счетчик команд, запоминающий блок, регистр команд и блок задания команд, выход коорого подключен ко второму аходу счётчика команд, а второй вход - к вьрсоду огического операционного блока и к первому входу выходного блока согласования и. нормирования сигналов, соединенного вторым входом через выходной коммутатор со вторым выходом регистра команд и с первым ахрдом аходного коммутатора, второй вход которого подключен к выходу входного блока согласования и нормирования сигналов, а третий выход регистра команд подключен к первому входу логического операционного блока, содержит блок свертки информацииг первый аход которого подключен к выходу аходного коммутатора, выходко второму аходу логического операционного блока, а второй и третий аходы к четвертому и пятому аыходам регистра команд соответственно а также тем, что блок свертки информадии содержит последовательно соединенные группу элементов ИЛИ-исключающее, группу элементов ИЛИ и элемент И, выход которого подключен к выходу блока, а вторые аходы элементов ИЛИ, первые, а также вторые аходы элементов ИЛИ исключающее соединены с третьим, вторым и первым блока соответственно,

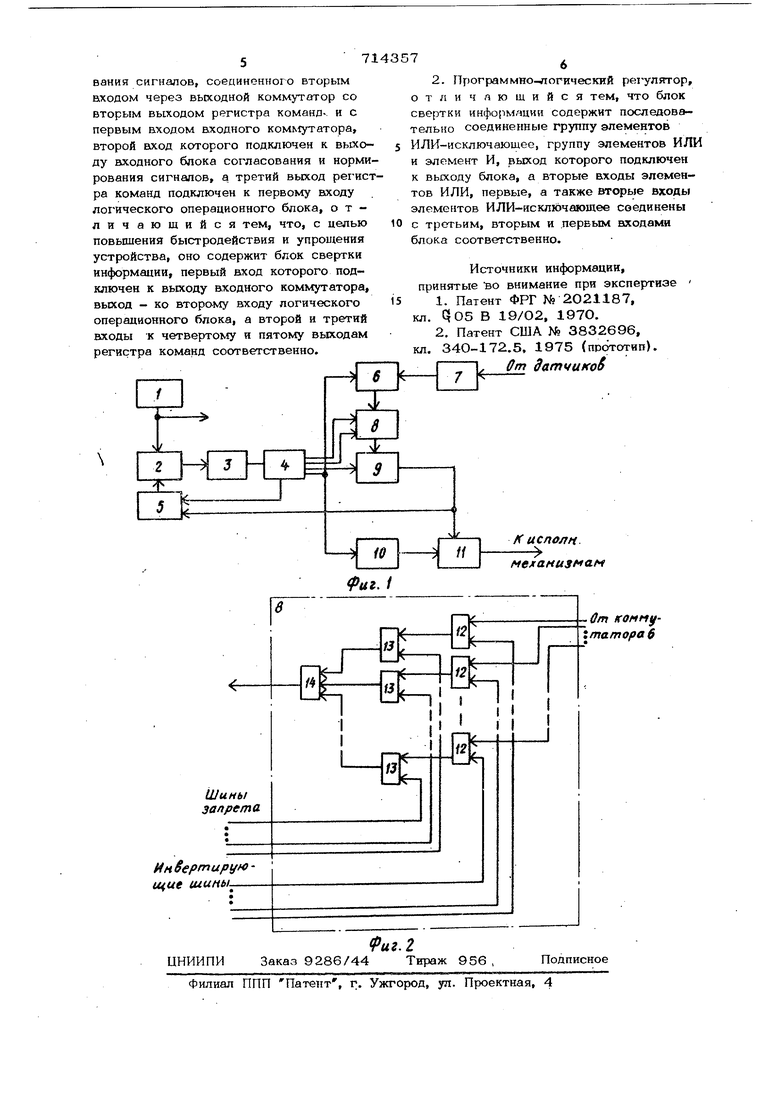

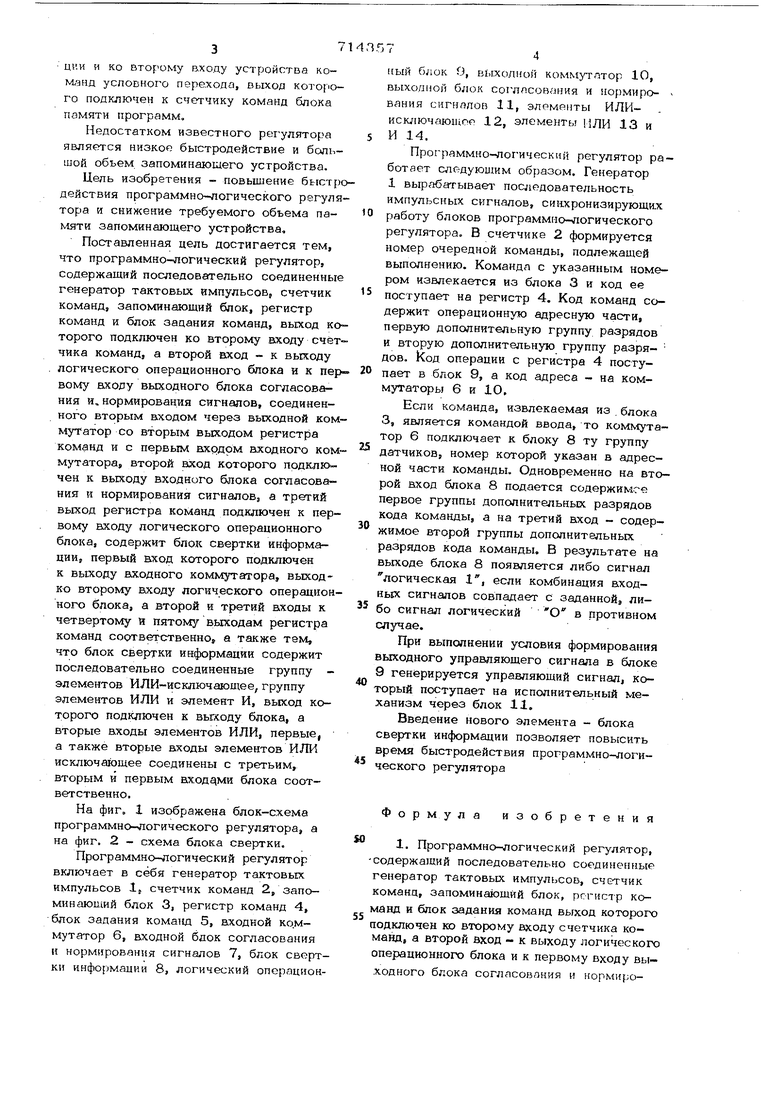

На фиг, 1 изображена блок-схема программно-логического регулятора, а на фиг, 2 - схема блока свертки.

Программно-логический регулятор включает в себя генератор тактовых импульсов IK счетчик команд 2, запоминаюишй блок 3, регистр команд 4, блок задания комавд 5, аходной коммутатор 6, аходной блок согласования II нормярования сигналов 7, блок свертки информации 8, логический операцяонЕ(ый блок О, вьглолнон коммутатор 10, ВЫ.ХОДИОЙ блок согллсования и нормиро- вання сигналоЕ) 11, элементы ИЛИисключаю1ЦО( 12, элементы ИЛИ 13 и

И 14,

Программно-логический регулятор работает следующим образом. Генератор 1 вырабатывает- последовательность импульсных сигналов, синхронизирующих

работу блоков программно-логического регулятора. В счетчике 2 формируется номер очередной команды, подлежащей выполнению. Команда с указанным номером извлекается из блока 3 и код ее

поступает на регистр 4. Код команд содержит операционную адресную части, первую дополнительную группу разрядов и вторую дополнительную группу разря- дов. Код операции с регистра 4 посту0 пает в блок 9, а код адреса - на коммутаторы б и 1О.

Если команда, извлекаемая из блока 3, является командой ввода, то коммутатор 6 подключает к блоку 8 ту группу датчиков, номер которой указан а адресной части команды. Одновременно на второй аход блока 8 подается содержимся первое группы дополнительных разрядов кода команды, а на третий аход - содержимое второй группы дополнительных разрядов кода команды. В результате на выходе блока 8 появляется либо сигнал логическая 1, если комбинация аходнь Х сигналов совпадает с заданной, ли бо сигнал логический О а противном случае.

При выполнении условия формирования выходного управляющего сигнала а блоке 9 ген ерируется управляющий сигнал, который поступает на исполнительный механизм через блок 11.

Введение нового элемента - блока свертки информации позволяет повысить время быстродействия программно-чпогического регулятора

Формула изобретения

1. Программно-алогический регулятор, -содержащий последовательно соединевшые генератор тактовых импульсов, счетчик команд, запоминающий блок, регистр команд и блок задания команд выход которого подключен ко второму входу счетчика команд, а второй вход - к выходу логического операционного блока и к первому входу выходного блока согласования н нормнрования сигналов, соединенного вторым входом через выходной коммутатор со вторым выходом регистра команд-, и с первым входом входного коммутатора, второй вход которого подключен к выходу входного блока согласования и нормирования сигналов, а третий выход регисра команд подключен к первому входу логического операционного блока, отличающийся тем, что, с целью повышения быстродействия и упрощения устройства, оно содержит блок свертки информации, первый вход которого подключен к выходу входного коммутатора, вькод - ко второму входу логического операционного блока, а второй и третий входы к четвертому и пятому выходам регистра команд соответственно.

2. Программно-логический регулятор, отличающийся тем, что блок свертки информации содержит последовательно соединенные группу элементов ИЛИ-исключающее, группу элементов ИЛИ и элемент И, выход которого подключен к выходу блока, а вторые входы элементов ИЛИ, первые, а также вторые входы элементов ИЛИ-исключающее соединены с третьим, вторым и .первым входами блока соответственно.

Источники информации, принятые во внимание при экспертизе 1. Патент ФРГ №2021187, В 19/О2, 197О.

кл

2. Патент США № 3832696,

кл. 340-172.5, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Программное устройство управления | 1982 |

|

SU1115021A1 |

| Устройство для последовательного программного управления | 1983 |

|

SU1126928A1 |

| Устройство опроса информационных каналов | 1980 |

|

SU920697A1 |

| Программируемый контроллер | 1981 |

|

SU1001012A1 |

| Устройство для сопряжения телеграфных каналов с вычислительной машиной | 1978 |

|

SU748403A1 |

| Распределенная система для программного управления технологическими процессами | 1988 |

|

SU1605212A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР | 2009 |

|

RU2417409C2 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2018 |

|

RU2708956C2 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

лг. /

ffm ifOMny1татора6

Авторы

Даты

1980-02-05—Публикация

1977-04-01—Подача