65

сл

тельной и вычислительной технике и может быть использовано в устройствах сбора, преобразования передачи и автоматизированной обработки электрических сигналов.

Целью изобретения является повышение точности работы устройства сжатия

устройства в исходное состояние из сетки частот на выходе делителя 4 частоты позволяет передать на вход регистра 7 самую высокую частоту, т.е. fГЦ . При таком состоянии сумматора коэффициент деления управляемого делителя 8 такой же, как и делителя информации при нестационарных входных IQ 3, т.е. запись ординат во второй блок сигналах.9 буферной памяти осуществляется с

устройства в исходное состояние из сетки частот на выходе делителя 4 частоты позволяет передать на вход регистра 7 самую высокую частоту, т.е. fГЦ . При таком состоянии сумма

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сжатия информации | 1983 |

|

SU1142855A1 |

| Устройство для сжатия информации | 1980 |

|

SU930333A1 |

| Устройство для сжатия информации | 1982 |

|

SU1056249A1 |

| Устройство для передачи телеметрической информации | 1983 |

|

SU1126993A1 |

| Устройство для передачи телеметрической информации | 1983 |

|

SU1129641A1 |

| ЦИФРОВОЙ РАДИОПЕЛЕНГАТОР | 1999 |

|

RU2149419C1 |

| Устройство для регистрации одиночных ударов | 1987 |

|

SU1479878A1 |

| Цифровое устройство селекции движущихся целей | 1984 |

|

SU1841294A1 |

| Устройство для выбора частотных диапазонов передачи группового радиосигнала | 1982 |

|

SU1072277A1 |

| Цифровой спектроанализатор | 1982 |

|

SU1092518A1 |

Изобретение относится к области измерительной и вычислительной тех-ч НИКИ и может быть использовано в устройствах сбора, преобразования, передачи и автоматизированной обработки электрических сигналов. Целью изобретения является повьшение точности работы устройства сжатия информации при нестационарных входных сигналах. Поставленная цель достигается введением управляемого делителя частоты, элемента И и новых связей, при этом в соответствии с найденной частотой дискретизации меняется коэффициент деления управляемого делителя частоты, в зависимости от которого изменяется частота записи существенных ординат обрабатываемого сигнала в выходную буферную память. 3 ил.

частотой запуска АЦП 1. Параллельно происходит запись ординат сигнала в первый блок 10 буферной памяти. По 15 сигналу переполнения счетчика 11, объем которого равен заданному числу

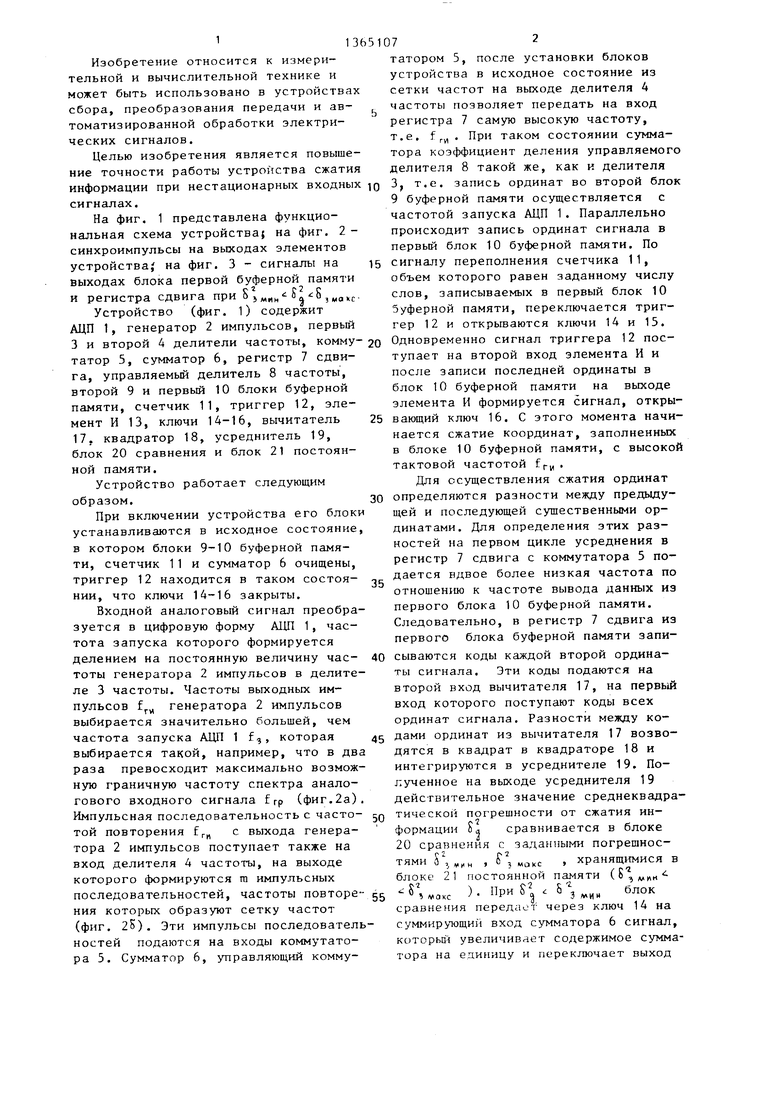

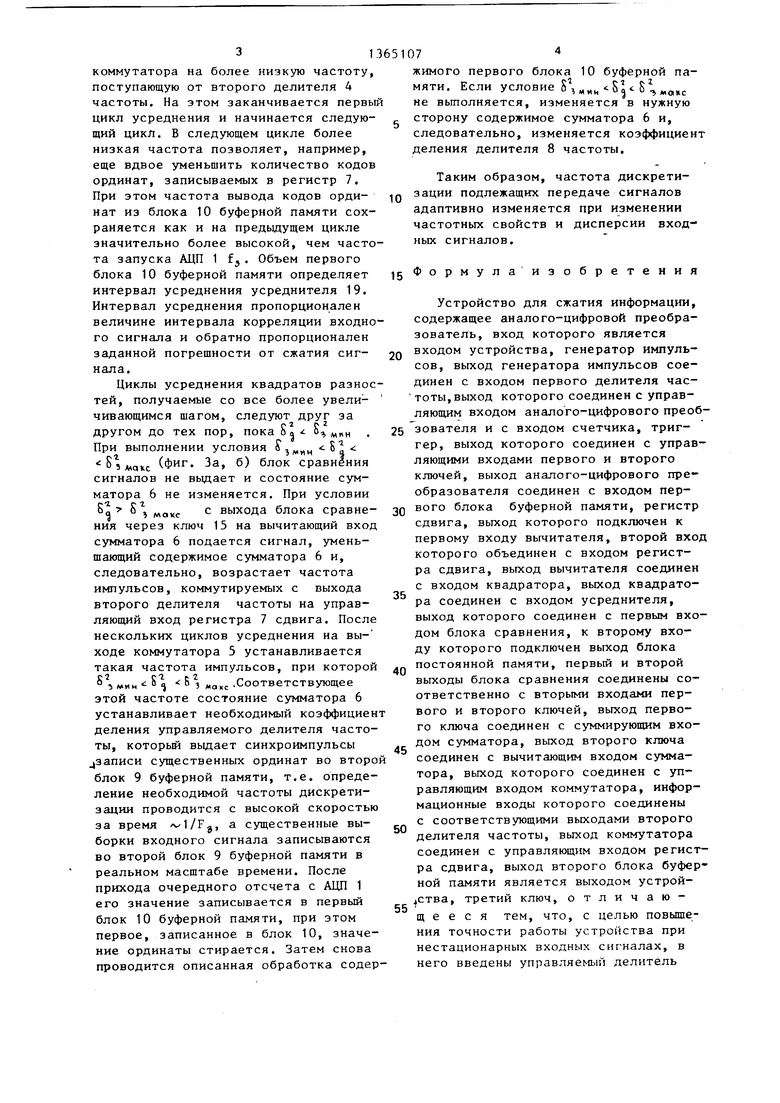

и регистра сдвига при S , „ S ,,0. слов, записываемых в первый блок 10 Устройство (фиг. 1) содержит буферной памяти, переключается тригАДП 1, генератор 2 импульсов, первый гер 12 и открьшаются ключи 14 и 15.

3 и второй 4 делители частоты, комму-20 Одновременно сигнал триггера 12 постатор 5, сумматор 6, регистр 7 сдви- тупает на второй вход элемента И и

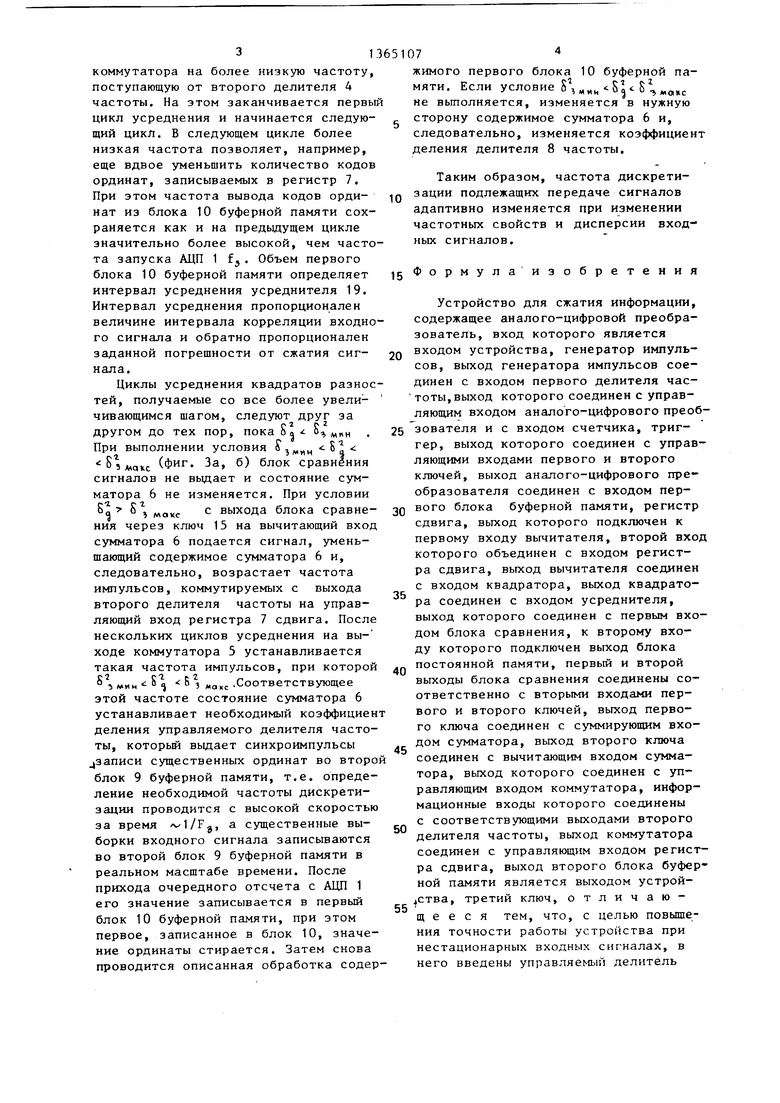

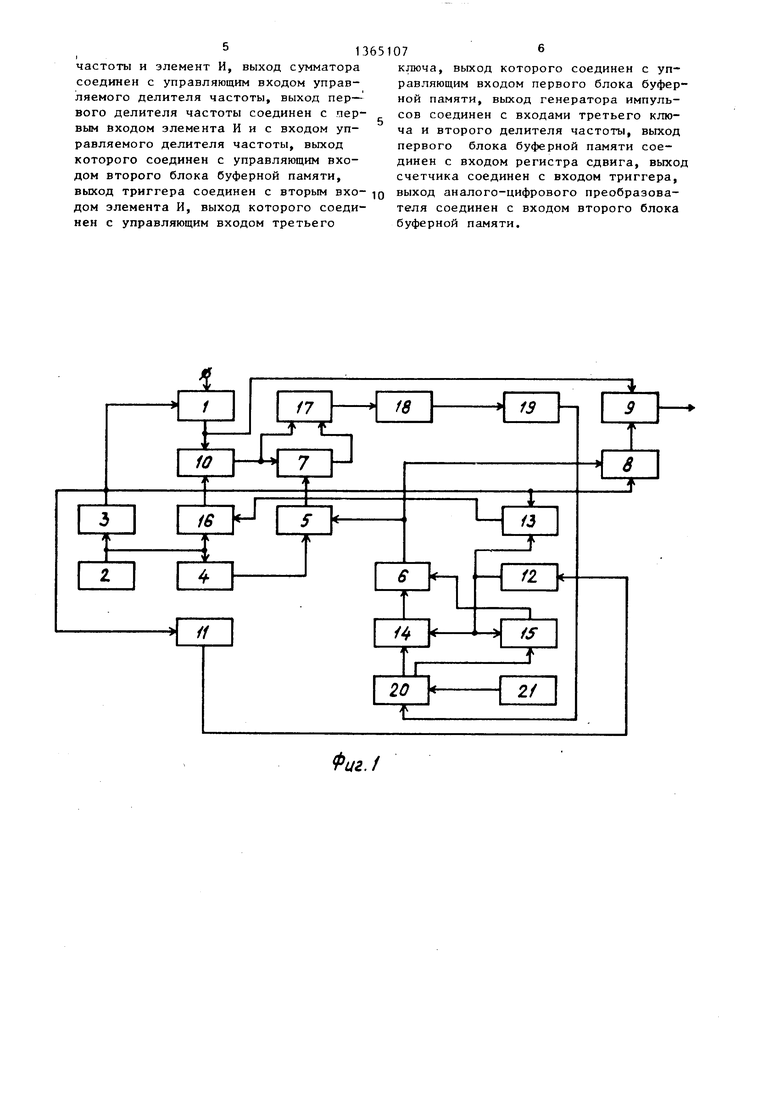

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - синхроимпульсы на выходах элементов устройстваJ на фиг. 3 - сигналы на выходах блока первой буферной памяти

га, управляемьш делитель 8 частоты, второй 9 и первый 10 блоки буферной памяти, счетчик 11, триггер 12, элемент И 13, ключи 14-16, вычитатель 17. квадратор 18, усреднитель 19, блок 20 сравнения и блок 21 постоянной памяти.

Устройство работает следующим образом.

При включении устройства его блок устанавливаются в исходное состояние в котором блоки 9-10 буферной памяти, счетчик 11 и сумматор 6 очищены, триггер 12 находится в таком состоя- НИИ, что ключи 14-16 закрыты.

Входной аналоговый сигнал преобразуется в цифровую форму АЦП 1, час

Для осуществления сжатия ординат 30 определяются разности между предыдущей и последующей существенными ординатами. Для определения этих разностей на первом цикле усреднения в регистр 7 сдвига с коммутатора 5 подается вдвое более низкая частота по отнощению к частоте вывода данных из первого блока 10 буферной памяти. Следовательно, в регистр 7 сдвига из первого блока буферной памяти запитота запуска которого формируется делением на постоянную величину час- 40 сываются коды каждой второй ордина- тоты генератора 2 импульсов в делите- ты сигнала. Эти коды подаются на ле 3 частоты. Частоты выходных им- второй вход вычитателя 17, на первый пульсов f, генератора 2 импульсов вход которого поступают коды всех выбирается значительно большей, чем ординат сигнала. Разности между ко- частота запуска АЦП 1 f, которая 45 Дзми ординат из вычитателя 17 возво- выбирается такой, например, что в два дятся в квадрат в квадраторе 18 и раза превосходит максимально возможную граничную частоту спектра аналоинтегрируются в усреднителе 19. Полученное на выходе усреднителя 19 действительное значение среднеквадрагового входного сигнала fгр (фиг.2а).

интегрируются в усреднителе 19. Полученное на выходе усреднителя 19 действительное значение среднеквадра

Импульсная последовательность с часто- Q тической погрешности от сжатия ин- той повторения f с выхода генера- формации а сравнивается в блоке тора 2 импульсов поступает также на вход делителя 4 частоты, на выходе которого формируются га импульсных последовательностей, частоты повторе- g - S , ния которых образуют сетку частот (фиг. 2S). Эти импульсы последователь- суммирующий вход сумматора 6 сигнал, ностей подаются на входы коммутатора 5. Сумматор 6, управляющий комму20 сравнения с за7;анными погрешностями 5,,;(,ц , , ц,д,с хранящимися в 21 постоянной памяти

2 г 1 : О

блоке 2

( S , VHH блок

vaKc ) Р 3 мии сравнения передает через ключ 14 на

которыи увеличивает содержимое сумма тора на единицу и переключает выход

после записи последней ординаты в блок 10 буферной памяти на выходе элемента И формируется сигнал, откры- вающий ключ 16. С этого момента начинается сжатие координат, заполненных в блоке 10 буферной памяти, с высокой

тактовой частотой f

ги

Для осуществления сжатия ординат определяются разности между предыдущей и последующей существенными ординатами. Для определения этих разностей на первом цикле усреднения в регистр 7 сдвига с коммутатора 5 подается вдвое более низкая частота по отнощению к частоте вывода данных из первого блока 10 буферной памяти. Следовательно, в регистр 7 сдвига из первого блока буферной памяти записываются коды каждой второй ордина- ты сигнала. Эти коды подаются на второй вход вычитателя 17, на первый вход которого поступают коды всех ординат сигнала. Разности между ко- Дзми ординат из вычитателя 17 возво- дятся в квадрат в квадраторе 18 и

сываются коды каждой второй ордина- ты сигнала. Эти коды подаются на второй вход вычитателя 17, на первый вход которого поступают коды всех ординат сигнала. Разности между ко- Дзми ординат из вычитателя 17 возво- дятся в квадрат в квадраторе 18 и

интегрируются в усреднителе 19. Полученное на выходе усреднителя 19 действительное значение среднеквадратической погрешности от сжатия ин- формации а сравнивается в блоке - S , суммирующий вход сумматора 6 сигнал

20 сравнения с за7;анными погрешностями 5,,;(,ц , , ц,д,с хранящимися 21 постоянной памяти

2 г 1 : О

блоке 2

( S , VHH блок

vaKc ) Р 3 мии сравнения передает через ключ 14 на

тической погрешности от сжатия ин- формации а сравнивается в блоке - S , суммирующий вход сумматора 6 сигнал,

которыи увеличивает содержимое сумматора на единицу и переключает выход

31

коммутатора на более низкую частоту, поступающую от второго делителя 4 частоты. На этом заканчивается первы цикл усреднения и начинается следующий цикл. В следующем цикле более низкая частота позволяет, например, еще вдвое уменьшить количество кодов ординат, записываемых в регистр 7. При этом частота вывода кодов орди- нат из блока 10 буферной памяти сохраняется как и на предыдущем цикле значительно более высокой, чем частота запуска АЦП 1 f. Объем первого блока 10 буферной памяти определяет интервал усреднения усреднителя 19. Интервал усреднения пропорционален величине интервала корреляции входного сигнала и обратно пропорционален заданной погрешности от сжатия сиг- нала.

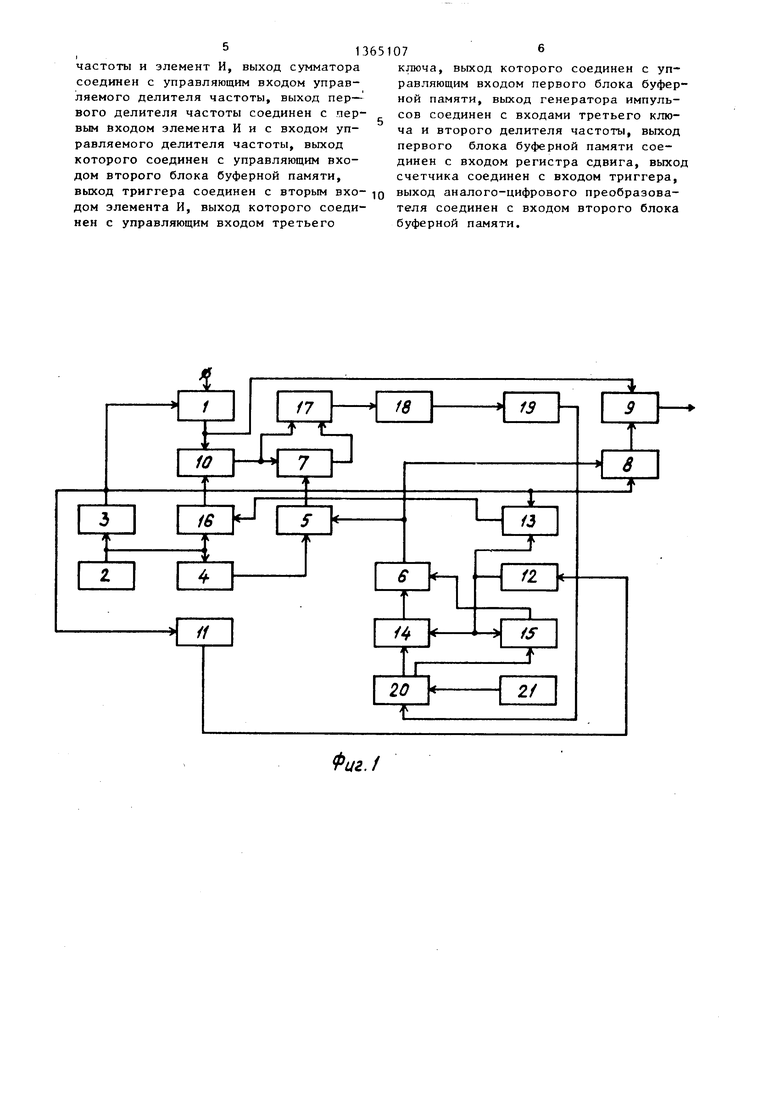

Циклы усреднения квадратов разностей, получаемые со все более увели- чивающимся шагом, следуют друг за

2 2

другом до тех пор, пока S i млн , Ппи пополнении условия 5,„„ S

Mqfcc (фиг- За, б) блок сравнения сигналов не выдает и состояние сумматора 6 не изменяется. При условии S

s

с выхода блока сравне- ни я через ключ 15 на вычитающий вход сумматора 6 подается сигнал, уменьшающий содержимое сумматора 6 и, следовательно, возрастает частота импульсов, коммутируемых с выхода второго делителя частоты на управляющий вход регистра 7 сдвига. После нескольких циклов усреднения на вы- ходе коммутатора 5 устанавливается такая частота импульсов, при которой мин 3 ма«с .Соответствующее этой частоте состояние сумматора 6 устанавливает необходимый коэффициен деления управляемого делителя частоты, который выдает синхроимпульсы записи существенных ординат во второ блок 9 буферной памяти, т.е. определение необходимой частоты дискретизации проводится с высокой скоростью за время 1/Г, а существенные вы- борки входного сигнала записываются во второй блок 9 буферной памяти в реальном масштабе времени. После прихода очередного отсчета с АЦП 1 его значение записывается в первый блок 10 буферной памяти, при этом первое, записанное в блок 10, значение ординаты стирается. Затем снова проводится описанная обработка содер

5

5

О Q с

5

07

жимого первого блока 10 буферной па- мяти. Если условие ,,,,, не вьтолняется, изменяется в нужную сторону содержимое сумматора 6 и, следовательно, изменяется коэффициент деления делителя 8 частоты.

Таким образом, частота дискретизации подлежащих передаче сигналов адаптивно изменяется при изменении частотных свойств и дисперсии входных сигналов.

Формулаизобретения

Устройство для сжатия информации, содержащее аналого-цифровой преобразователь, вход которого является входом устройства, генератор импульсов, выход генератора импульсов соединен с входом первого делителя частоты, выход которого соединен с управляющим входом аналого-цифрового преоб- зователя и с входом счетчика, триггер, выход которого соединен с управляющими входами первого и второго ключей, выход аналого-цифрового преобразователя соединен с входом первого блока буферной памяти, регистр сдвига, выход которого подключен к первому входу вычитателя, второй вход которого объединен с входом регистра сдвига, выход вычитателя соединен с входом квадратора, выход квадратора соединен с входом усреднителя, выход которого соединен с первым входом блока сравнения, к второму входу которого подключен выход блока постоянной памяти, первый и второй выходы блока сравнения соединены соответственно с вторыми входами первого и второго ключей, выход первого ключа соединен с суммирующим входом сумматора, выход второго ключа соединен с вычитающим входом сумматора, выход которого соединен с управляющим входом коммутатора, информационные входы которого соединены с соответствующими выходами второго делителя частоты, выход коммутатора соединен с управляющим входом регистра сдвига, выход второго блока буферной памяти является выходом устрой- iCTsa, третий ключ, отличающееся тем, что, с целью повышения точности работы устройства при нестационарных входных сигналах, в него введены управляемый делитель

51

частоты и элемент И, выход сумматора соединен с управляющим входом управляемого делителя частоты, выход пер- вого делителя частоты соединен с первым Входом элемента И и с входом управляемого делителя частоты, выход которого соединен с управляющим входом второго блока буферной памяти, выход триггера соединен с вторым входом элемента И, выход которого соединен с управляющим входом третьего

Фцг.1

651076

ключа, выход которого соединен с управляющим входом первого блока буферной памяти, выход генератора импуль- сов соединен с входами третьего ключа и второго делителя частоты, выход первого блока буферной памяти соединен с входом регистра сдвига, выход счетчика соединен с входом триггера, 10 выход аналого-цифрового преобразователя соединен с входом второго блока буферной памяти.

а

N

5| |1

«s

5

|§ |ч

§

I

I

I

I

I

т

время

бреия

8peAfjt

ut. z:

5l ii

i

§i

V

1 c Illllllllllllllllllllllllllllllllllll

Si

L a

III MM II III

Сриг.З

epewi

| Устройство для сжатия информации | 1983 |

|

SU1142855A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1988-01-07—Публикация

1986-07-07—Подача