(54) МИКРОПРОГРАММНЫЙ ПРОЦЕССОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор с микропрограммным управлением | 1982 |

|

SU1124298A1 |

| Микропрограммный процессор | 1974 |

|

SU535567A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Микропрограммное устройство управления | 1981 |

|

SU955061A1 |

| Микропрограммный процессор | 1987 |

|

SU1517034A1 |

| Микропрограммный процессор | 1982 |

|

SU1062712A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1084793A1 |

| Микропрограммное устройство управления | 1980 |

|

SU881748A1 |

| Процессор с микропрограммным управлением и динамическим ветвлением | 1979 |

|

SU773624A1 |

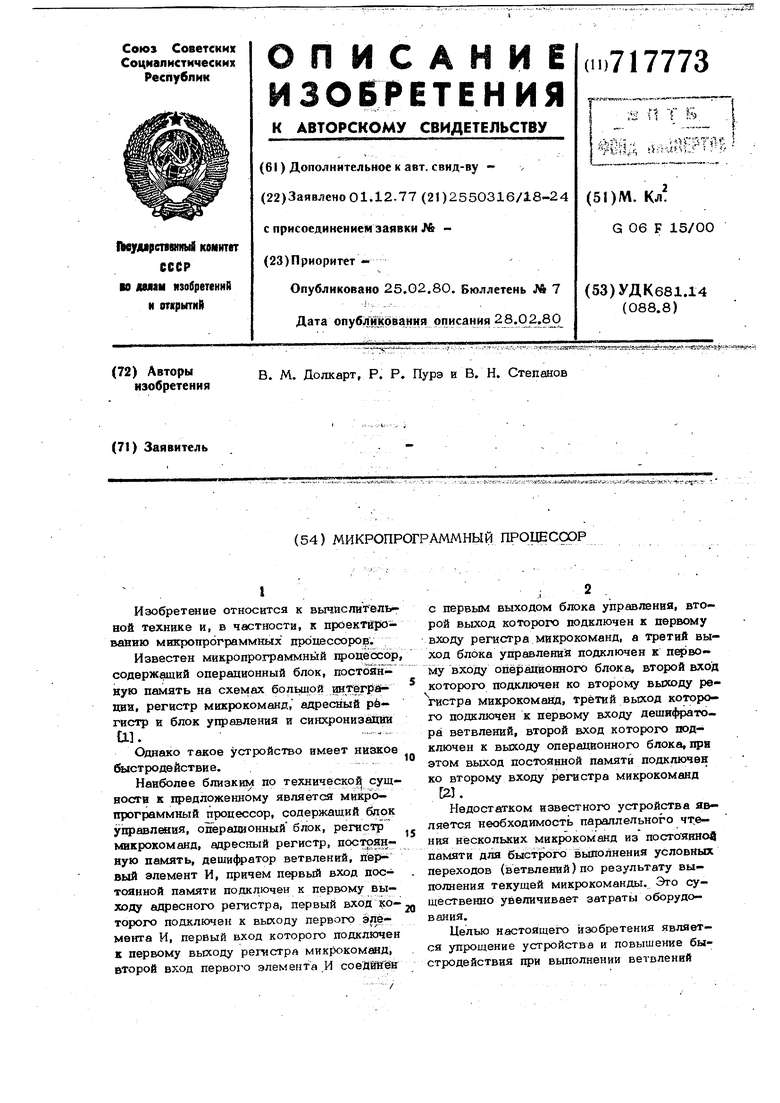

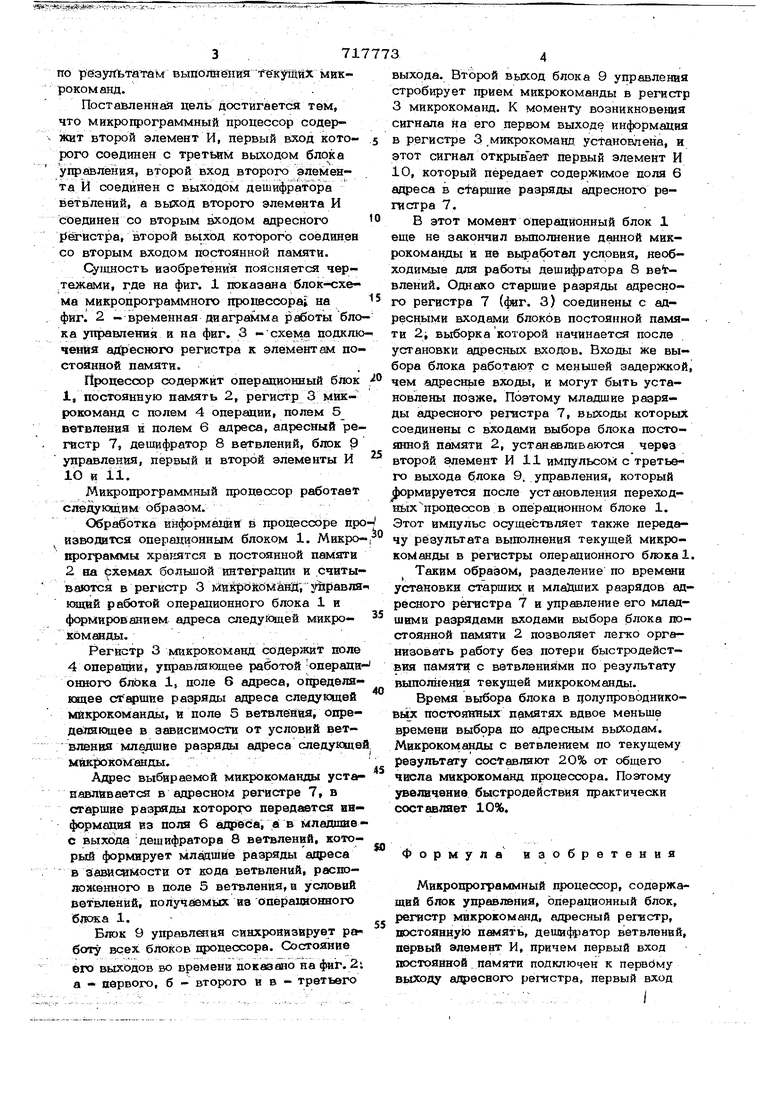

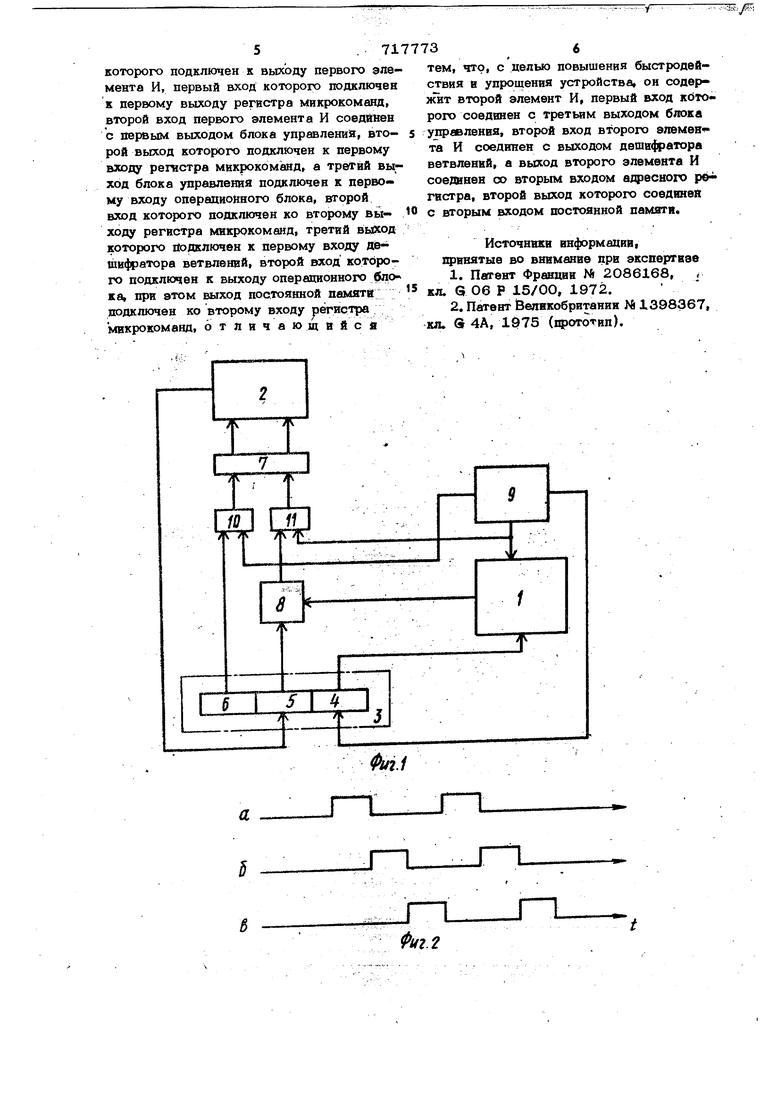

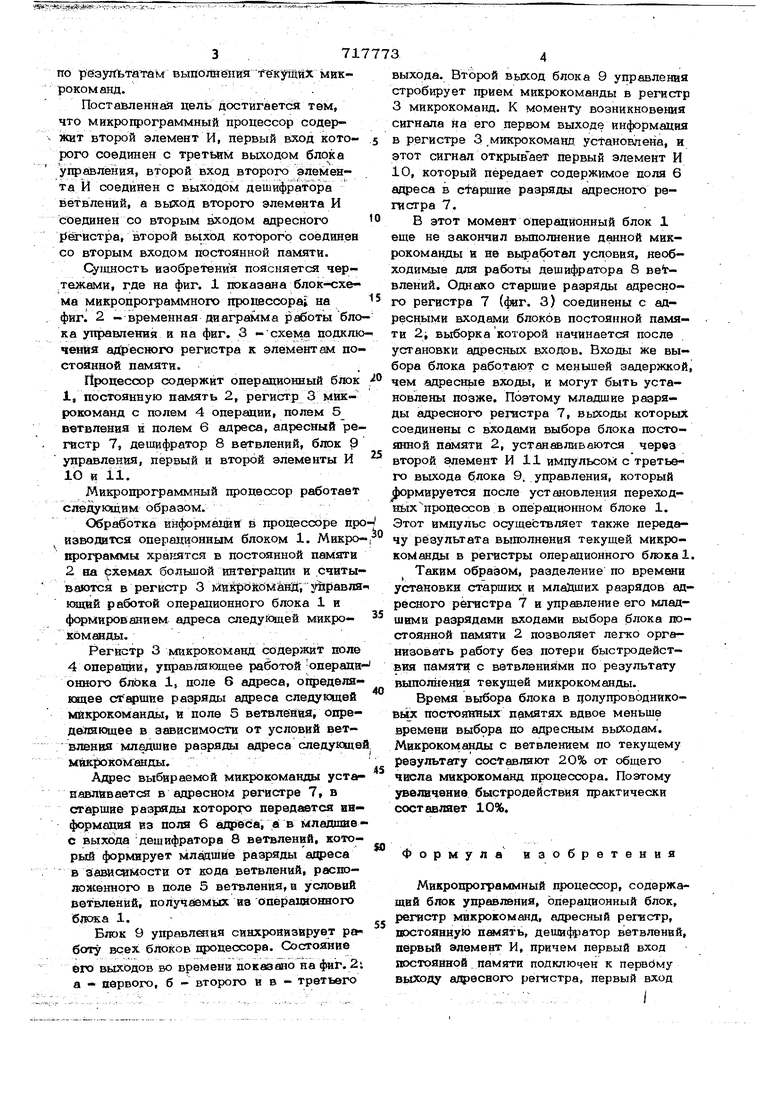

.I Изобретение относится к вычислительной технике и, в частности, к проектированию микропрограммных процессоров. Известен микропрограммный процессор содерж ий операционный блок, посто н- кую память на схемах большой интегра дин, регистр микрокоманд, адресный регистр и блок угфавления и синхронизации Однако такое устройство имеет низкое &1стродеЙстви е. Наиболее близким по техническо)а сущности к 1фадложенному является микропрограммный процессор, содержащий блок управления, операционный блок, регистр макрокоманд, адресный регистр, постоянную память, деши4 атор ветвлений. Пёр- вый элемент И, причем первый вход постоянной памяти подключен к первому выходу адресного регистра, первый вход которого подключен к выходу первого эр емента И, первый вход которого подключен к первому выходу регистра микрокоманд, второй вход первого элемента И соейЩён С первым выходом блока управления, второй выход которого подключен к первому входу регистра микрокоманд, а третий выход блока управлений подключен к первому входу операционного блока, второй axoia которого подключен ко второму выходу реVиcтpa микрокоманд, третий выход которого подключен к первому входу дешифратора ветвлений, второй вход которого подключен к выходу операционного блока, при этом вьисод постоянной памяти подключен ко второму входу регистра микрокоманд Д1. Недостатком известного устройства является необходимость параллельного чтения нескольких микрокоманд из постояввов памяти для быстрого выполнения условных переходов (ветвлений) по результату выполнения текущей микрокоманды. Это существенно увеличивает затраты оборудования. Целью настоящего изобретения является упрощение устрюйства и повышение быстродействия при выполнении ветвлений 3717 по результатам выполнения -feRymftX микрокоманд.. Поставленная цель достигается тем, что микрогфограммный процессор содержит второй элемент И, первый вход которого соединен с третьим выходом блока управления, второй вход второго элемента И соединен с выходом дешифратора ветвлений, а выход второго элемента И соединен со вторым входом адресного рагистра, второй выход которого соединен со вторым входом постоянной памяти. Сущность иаобретения поясняется чертежами, г;де на фиг. 1 показана блок-схема микропрограммного процессора на фиг. 2 -временная диаграмма работы блока управления и на фиг. 3 - cxevia подклю ченйя адресного регистра к элементам постоянной памяти. Йроцессор содержит операционный блок 1, постоянную память 2, регистр 3 микрокоманд с полем 4 операции, полем 5 ветвления и полем 6 адреса, адресный резгистр 7, дешифратор 8 ветвлений, блок Э управления, первый и второй элементы И 10 и 11. Микропрограммный процессор работает следующим образом. Обработка информации в процессоре npo йзводится операционным блоком 1. Микро- прохраммы храггятся в постоянной памяти 2 ва Схемах болыиой интеграции к считываются в регистр 3 йизфошманй, jйpaвля ющий работой операционного блока 1 в формированием адреса следуквцей микрокоманды. Регистр 3 микрокоманд содержит поле 4 операции, управляющее работой операцаонного блока 1, поле 6 адреса, О1феделяющее разряды адреса следующей Микрокоманды, и поле 5 ветвления, опре- дейгакчдее в зависимости от условий ветвления младшие разряды адреса следующе мйкрокоманды. Адрес выбираемой микрокоманды устагнавливается в адресном регистре 7, в старшие разряды которого передвется информация из поля б адреса, а в младшиес выхода дешифратора 8 ветвлений, который формирует младшие разряды адреса в завйсйМрсти от кода ветвлений, расположенного в поле 5 ветвления, и условий ветвлений, получаемьос из операционного бдока 1. Блок 9 управлшия синхронизирует работу всех блоков процессора. Состояние его вьгходов во времена показеио на фиг. 2t а - первого, б - второго и в - третьегчэ 3 выхода. Второй выход блока 9 управления стробирует прием микрокоманды в регистр 3 микрокоманд. К моменту возникновения сигнала на его первом выходе информация в регистре 3 .микрокоманд, установлена, и этот сигнал открывает первый элемент И 10, который передает содержимое поля 6 адреса в старшие разряды адресного регистра 7. В этот момент операционный блок 1 еще не закончил вьшолнение данной микрокоманды а не выработал условия, необходимые для работы дешифратора 8 ве влений. Однако старшие разряды адресного регистра 7 (4иг. 3) соединены с адресными входами блоков постоянной памяти 2; выборка которой начинается после установки адресных входов. Входы же выбора блока работают с меньщей задержкой. чем адресньш входы, и могут быть установлены позже. Поэтому младшие разряды адресного регистра 7, вьгходы которых соединены с входами выбора блока постоянной памяти 2, устанавливаются через второй элемент И 11 импульсом с третьего выхода блока 9. управления, который {юрмируется после установления переходных процессов в операционном блоке 1. Этот импульс осуществляет также передачу результата выполнения текущей микрокоманды в регистры операционного блока. Таким образом, разделение по времени установки старших и млайших разрядов адресного регистра 7 и управление его младшими разрядами входами выбора блока постоянной памяти 2 позволяет легко организовать работу без потери быстродействия памяти с ветвлениями по результату выполнения текущей микрокоманды. Время выбора блока в цолупроводниковых постоянных памятях вдвое меньше времени выбора по адресным выходам. Микрокоманды с ветвлением по текущему результату составляют 20% от общего числа микрокоманд процессора. Поэтому увеличение быстродействия црактически составляет 10%. Формула изобретения Микропрограммный процессор, содержащий блок управления, операционный блок, регистр микрокоманд, адресный регистр, постоянную память, деши41звтор ветвлений, первый элемент И, причем первый вход постоянной памяти подключен к первому выходу адресного) регистра, первый вход

которого подключен к выходу первого элемента И, первый вход которого подключен к первому выходу регистра микрокоманд, второй вход первого элемента И соединен с первым выходом блока управления, второй выход которого подключен к первому входу регистра микрокоманд, а третий выход блока управления подключен к первому входу операционного блока, второй вход которого подключен ко второму выходу регистра микрокоманд, третий в:ьйсод которого подключен к первому входу Д1э ши41ратора ветвлений, второй вход которого подключен к выходу операционного бло ка, при этом выход постоянной памяти подключен ко второму входу регистра микрокоманд, 6 т л и ч а ющ и и с я

Ш Ш

Ж ф |Сж

тем, что, с целью повышения быстродейс -вия и упрощения устройства, он содержит второй элемент И, первый вход кЬторого соединен с третьим выходом блока управления, второй вход второго элемев та И соединен с выходом дешифратора ветвлений, а выход второго элемента И соединен со BTopbUvt входом адресного рё гистра, второй выход которого соединен с вторым входом постоянной памяти.

Источники информации, щзинятые во внимание цри экспертизе

L

Й«./

ГЛ.

-П.

Фиг.2

717773

Авторы

Даты

1980-02-25—Публикация

1977-12-01—Подача