И, элемент НЕ и элемент ИЛИ, при этом адресный вход, информационный вход, вход управления выборкой, вход строба записи младшего слова, вход строба записи старшего слова, выход старшего слова и выход младшего слова накопителя соединены соот ветственно с адресным выходом коммутатора адреса, информационным входом блока, выходом элемента ИЛИ, выходом первого элемента И, выходом второго элемента И, первым и вторым выходами блока, йервые входы всех элементов И подключены к первому управляющему входу блока, управляющий выход коммутатора адреса соединен с вторым входом первого элемента И и входом элемента НЕ, выход которого подключен к второму входу второго элемента И, вторые входы и выходы третьего и четвертого элементов И соединены соответственно с вторым и третьим управляющими входами блока и первым и вторым входами элемента ИЛИ, первый и второй адресные входы и- первый и второй управляющие входы коммутатора адреса подключены соответственно к первому и второму адресным входам блока и второму и третьему управляющим входам блока.

3. Процессор по п. 1, отличающийся тем, что блок формирования адреса микрокоманд содержит регистр адреса микрокоманд, дешифратор адреса, группу элементов ИЛИ и три группы элементов И, первые входы которых соединены соответствен но с nepBfcjM, вторым и третьим адресными входами.блока, вторые входы элементов И всех групп подключены к управляющему входу блока, первый, второй и третий входы и выходы элементов ИЛИ группы соединены соответ

ственно с выходами элементов И первой, второй и третьей групп и входом регистра адреса микрокоманд, выходы младшей и старшей частей которого подключены соответственно к адресному выходу блока и входу дешифратора адреса, а выход дешифратора адреса соединен с управляющим выходом блока.

4. Процессор по п. 1, о т л ичающийся тем, что блок обработки содержит первый и второй узлы регистров, коммутатор, сумматор, сдвигатель, регистр данных и узел сравнения, первый и второй входы и выход которого подключены соответственно к управляющему входу блока, выходу сумматора и второму адресному выходу блока, информационные и управляющие входы первого и второго узлов регистров соединены соответственно с выходом сдвигателя и управляющим входом блока, выходы первого и второго узлов регистров подключены к первым информационным входам соответственно сумматора и коммутатора, второй информационный вход, управляющий вход и выход которого соединены соответственно с информационным входом блока, управляющим входом блока и вторым информационным входом сумматора, управляющий вход и выход сумматора подключены соответственно к управляющему входу блока и информационному входу сдвигателя, управляющий вход и выход которого соединены соответственно с управляющим входом и первым адресным выходом блока, а информационный вход, управляющий вход и выход регистра данных подключены соответственно к выходу сдвигателя, управляющему входу и информационному выходу

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Микропрограммный процессор | 1986 |

|

SU1462339A1 |

| Процессор с микропрограммным управлением | 1982 |

|

SU1124298A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Микропрограммный процессор со средствами быстрого прерывания | 1982 |

|

SU1116432A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Микропрограммное устройство для сопряжения процессора с абонентами | 1987 |

|

SU1539787A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

1

Изобретение относится к вычислительной технике и предназначено для применения в малых цифровых вычислительных мal Jинax с микропрограммным управлением (мини- и микро-ЭВМ).

Как известно, в основе построения микропрограммных процессоров лежит использование постоянных запоминающих устройств для хранений микропрограмм. В то же время развитие технологии, появления новых аппаратных и программных средств реализации, возрастающий объем микропрограммного обеспечения и необходимость наиболее эффективного его применения при-г вело к введению в состав ЭВМ микропрограмглной памяти с перезаписью.

в том числе оперативной памяти, и построение на ее основе процессоров с динамическим микропрограммированием. Динамическое микропрограммирование улучшает функциональные возможности традиционных способов применения микропрограммирования, обеспечивает возможность моделирования с использованием микропрограммного

уровня управления, разработку новых языковых средств, доступность микропрограммирования пользователю и др. . Микропроцессоры с динамическим микропрограммированием открывают новые

возможности при использовании их для построения высокопроизводительных больших ЭВМ и мультисистем. В настоящее время используются главным образом два подхода при построении процессоров с динамическим микропрограммированием. Первый под, ход состоит в использовании собстве ,ной оперативной памяти устройства управления, запись в которую осущес вляется по выбранному алгоритму из главной памяти, микропрограммной постоянной памяти либо внешних устройств l . Второй подход заключается в использовании главной памяти ЭВМ для хранения и выполнения .из нее микропрограмм. В этом случае нет необход мости в дополнительной аппаратуре перезаписи, разработке алгоритмов предварительного вызова микропрогра при их оперативной смене, затратах времени на перезапись необходимых микропрограмм, так как они могут храниться в общем поле.программ пол зователя. Кроме того, отпадает необ ходимость в специальных командах за грязки и процедурах поиска местонахождения микропрограмм. Наиболее близким по технической сущности к предлагаемому является микропрограммный процессор, позволя ющий выполнять микропрограммы, хранящиеся I в микропрограммном постоян1 м запоминающем устройстве или в Главной памяти. Этот микропрограммный процессор содержит блок главной памяти, блок микропрограммной памяти, регистр команд, регистр данных, элементы И, коммутатор микрокоманд, регистр микрокоманд с адресной и операционной частями, блок формирования адреса микрокоманд, дешифратор управляющих сигналов, блок обработки и блок управления адресацией главной памяти.. Выход блока главной пам ти соединен с входом регистра коман и регистра данных. Первый выход бло ка микропрограммной памяти соединен с информационным входом элементов И Второй выход блока микропрограммной памяти соединен с первым входом ком мутатора, второй вход которого соединен с выходом регистра данных и H формационным входом блока обработки Выхрды элементов И и коммутатора . соединены с входами адресной и oneрационной частей регистра микрокоманд соответственно. Выход адресной части соединен с первым входом блока формирования адресов микрокоманд второй вход которого соединен с В1ых дом регистра команд, третий вход со динен с управляющим выходом блока обработки, а выход соединен с входо блока микропрограммной памяти. Упра ляяхций выход блока $шравления ёщресацией соединен с управляющими входами элементов И и коммутатора, а адресный выход соединен с адресным входом блока главной памяти. Блок управления адресацией соединен также с блоком обработки, информационные выходы которого соединены с соответствующим входом блока главной памяти. Выход операционной части регистра микрокоманд соединен с входом дешифратора управляющих сигналов, выходы которого соединены соответственно с управляющими входами блока обработки, блока формирования адреса микрокоманд, блока управления адресацией главной памяти и управляющими входами регистра команд, регистра данных соответственно .23 . Недостатком известного процессора является невысокое быстродействие. Это вызвано тем, что цикл обращения к главной памяти в современных ЭВМ больше(обычно в несколько раз) цикла обращения к постоянной микропрограммной памяти. В связи с этим в режиме обращения к главной памяти время выполнения микропрограмм увеличивается. Креме того, описанная организация процессора ограничивает разрядность микрокоманд разрядностью главной памяти, которая,, например, в современных мини-ЭВМ составляет в основном 16 разрядов. Это приводит либо к ограничению мощности микрокоманды, либо к применению сильных способов кодирования. В обоих случаях быстродействие снижается, так как мощность микрокоманды определяется числом параллельно выполняющихся микроопераций, а сильные способы кодирования усложняют схемы дешифрации, вносящие дополнительные за- держки. Цел.ью изобретения является увеличение быстродействия микропрограммного процессора. Поставленная цель достигается тем, что в микропрограммный процессор, содержащий блок главной памяти, блок управления адресацией главной памяти, состоящий из дешифратора адреса и регистра адреса, блок обработки, блок микропрограммной памяти, блок формирования адреса микрокоманд, коммутатор микрокоманд, регистр микрокоманд, дешифратор управляющих сигналов и регистр команд, управляющий вход которого соединен с выходом дешифратора управляющих сигналов, информационный выход, первый, второй адресные выходы и управляющий вход блока обработки подключены соответственно к информационному входу блока главной памяти, адресному входу регистра адреса, первому адресному входу блока формирования адреса микрокоманд и выходу дешифратора управляющих сигналов, управляющий вход, выход старшей части и выход младшей части регистра адреса соединены соответственно с выходом дешифратора управляющих сигналов, входом дешифратора адреса и адресным входом бло ка главной памяти, управляющий вход второй и третий адресные входы, адресный выход и управляющий выход бло ка формирования адреса микрокоманд подключены соответственно к выходу дешифратора управляющих сигналов, выходу регистра команд, выходу адресной части регистра микрокоманд, адресному входу блока микропрограммной памяти и управляющему входу коммутатора микрокоманд, первый и второй информационные входы и выход которого соединены соответственно с первым и вторым выходами блока микропрограммной памяти и входом регистра микрокоманд, выход операционной части регистра микрокоманд подключен к входу дешифратора управляющих сигналов, выход которого соединен с управляющими входами блока главной памяти и блока микропрограммной памяти, введены блок оперативной памяти и коммутатор данных, первый и второй управляющие входы и первый, второй и третий информационные входы которого подключены соответственно к выходам дешифратора адреса и младшего разряда регистра адреса, выходу блока главной памяти первому и второму выходам блокаоперативной памяти, выход коммутатора данных соединен с. информационными входами регистра команд и блока обработки, а и: фopмaдиoнный вход первый, второй и третий управляющие входы, первый и второй адресные вхо ды, первый и,второй выходы блока опе ративной памяти подключены соответственно к информационному выходу блока обработки, выходу дешифратора управляющих сигналов, выходу дешифратора адреса, управляющему выходу блока формирования адреса микрокоманд,, выходу младшей части регистра адреса, адресному выходу блока формирования адреса микрокоманд, треть му и четвертому информационным входам коммутатора микрокоманд. Кроме тога, блок оперативной памяти содержит накопитель, коммутатор адреса, четыре элемента И-, элемент НЕ и элемент ИЛИ, при этом адресный вход, информационный вход, вход управления выборкой, вход стро записи младшего слова, вход строба записи старшего слова, выход старшего слова и выход младшего слова накопителя соединены соответственно с адресным выходом коммутатора адре са, информационным входом блока, вы ходом элемента ИЛИ, выходом первого элемента И, выходом второго элемента И, первым и вторым выходами блока, первые входы всех элементов И подключены к первому упревляк-щему вхо ду.блока, управляющий выход коммутатора адреса соединен с вторым входом первого элемента И и входом элемента НЕ, выход которого подключен к второму входу второго элемента И, вторые входы и выходы третьегои четвертого элементов И соединены соответственно с вторым и третьим управляющими входами блока и первым и вторым входами элемента ИЛИ, первый и второй адресные входы и первый и второй управляющие входы коммутатора адреса подключены соответственно к первому и второму адресным входам блока и второму и третьему удравляющим входам б.лока. Причем блок формирования адреса микрокоманд содержит регистр адреса микрокоманд, дешифратор адреса, группу элементов ИЛИ и три группы элементов И, первые входы которых соединены соответственно с первым, вторым и третьим адресными входами .блока, вторые входы элементов И всех групп подключены к управляющему входу блока, первый, второй и третий входы и выходы элементов ИЛИ группы соединены сбответственно с выходами элементов И первой, второй и третьей групп и входом регистра адреса микрокоманд, выходы младшей и старшей частей которого подключены соответственно к адресному выходу блока и входу дешифратора адреса, а выход дешифратора адреса соединен с управляющим выходом блока. При этом блок обработки содержит первый и второй узлы регистров, коммутатор, сумматор, сдвигатель, регистр данных и узел .сравнения, первый и второй входы и выход которого подключены соответственно к управляющему входу блока, выходу сумма- тора и второму адресному выходу блока, информационные и управляющие входы первого и второго узлов регистров соединены соответственно с выходом сдвигателя и управляющим входом блока, выходы первого и второго узлов регистров подключены к первым информационным входам соответственно сумматора и коммутатора, второй информационный вход, управляющий вход и выход которого соединены соответственно с информационным входом блока, управляющим входом блока и вторым информационным входом сумматора, управляющий вход и выход сумматора подключены соответственно к управляющему входу блока и информационному входу сдвигателя, управляющий вход и выход которого соединены соответственно с управляющим входом и первым, адресным выходом блока, а информационный вход, управляющий вход и выход регистра данных подключены соответственно к выходу сдвигателя, управляющему входу и информационному выходу блока.

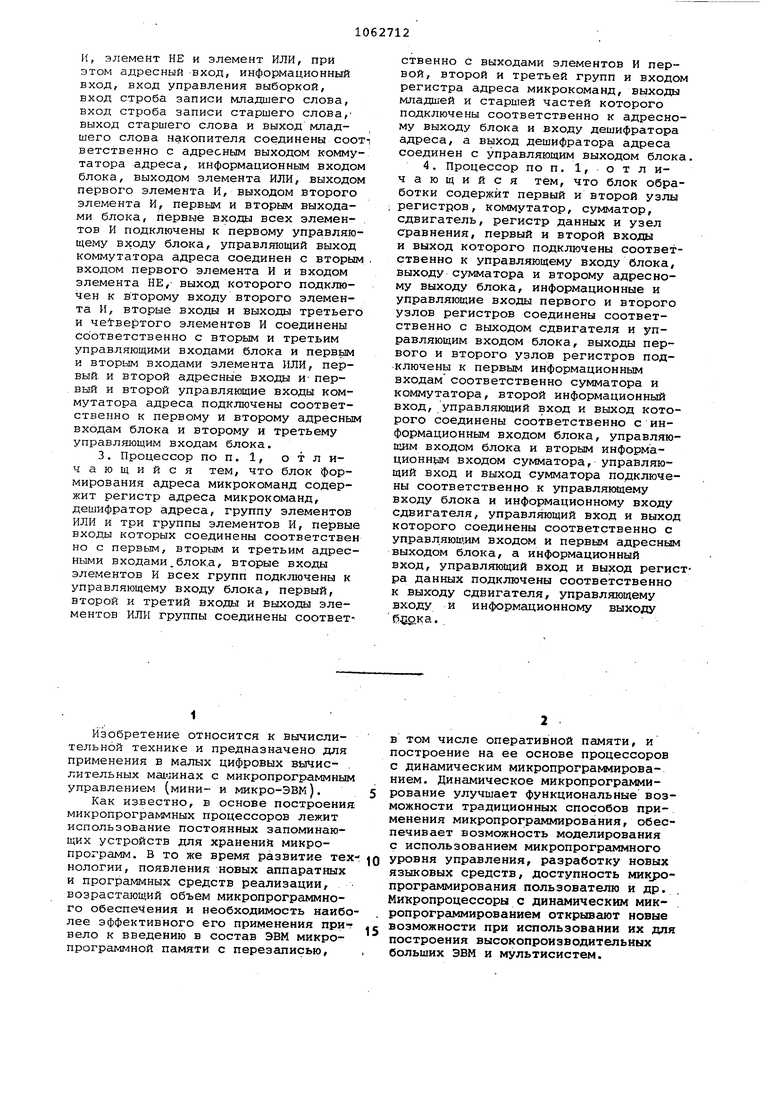

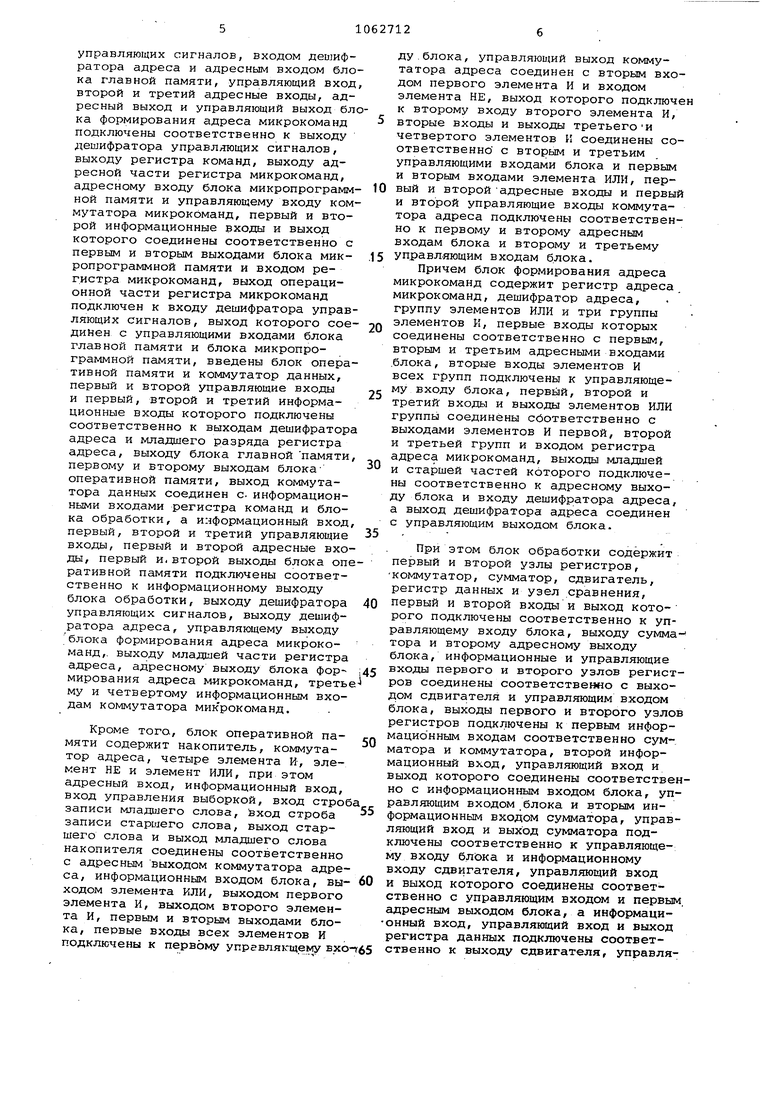

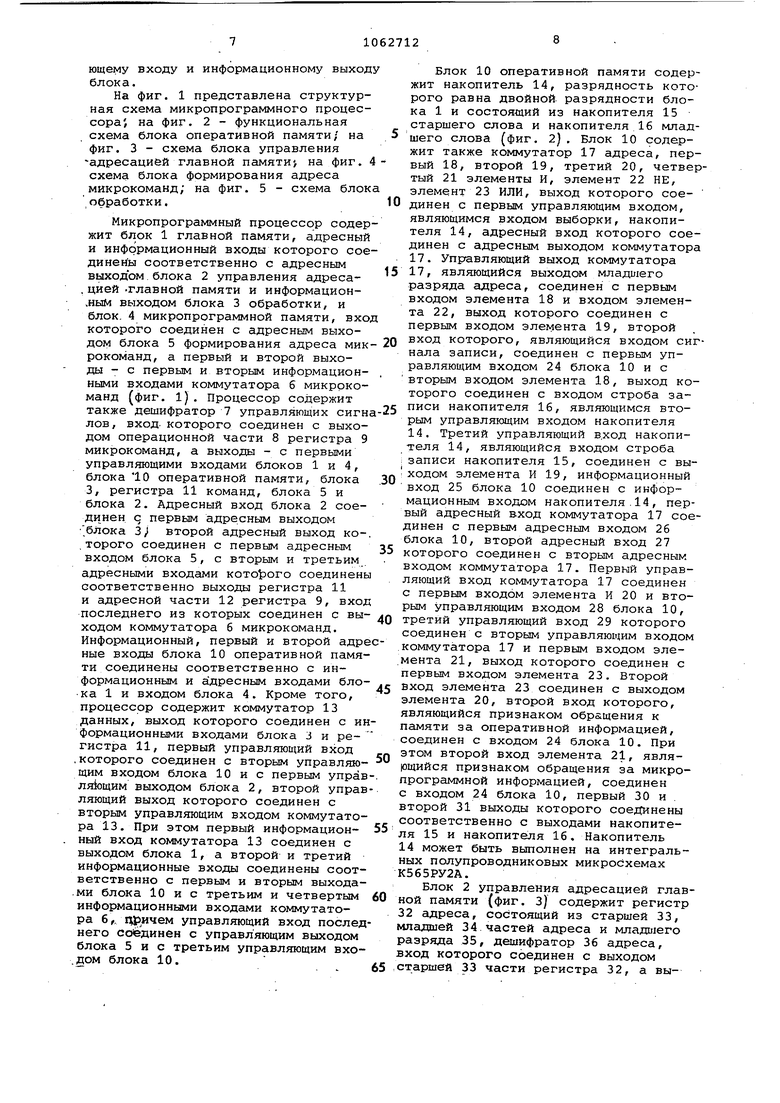

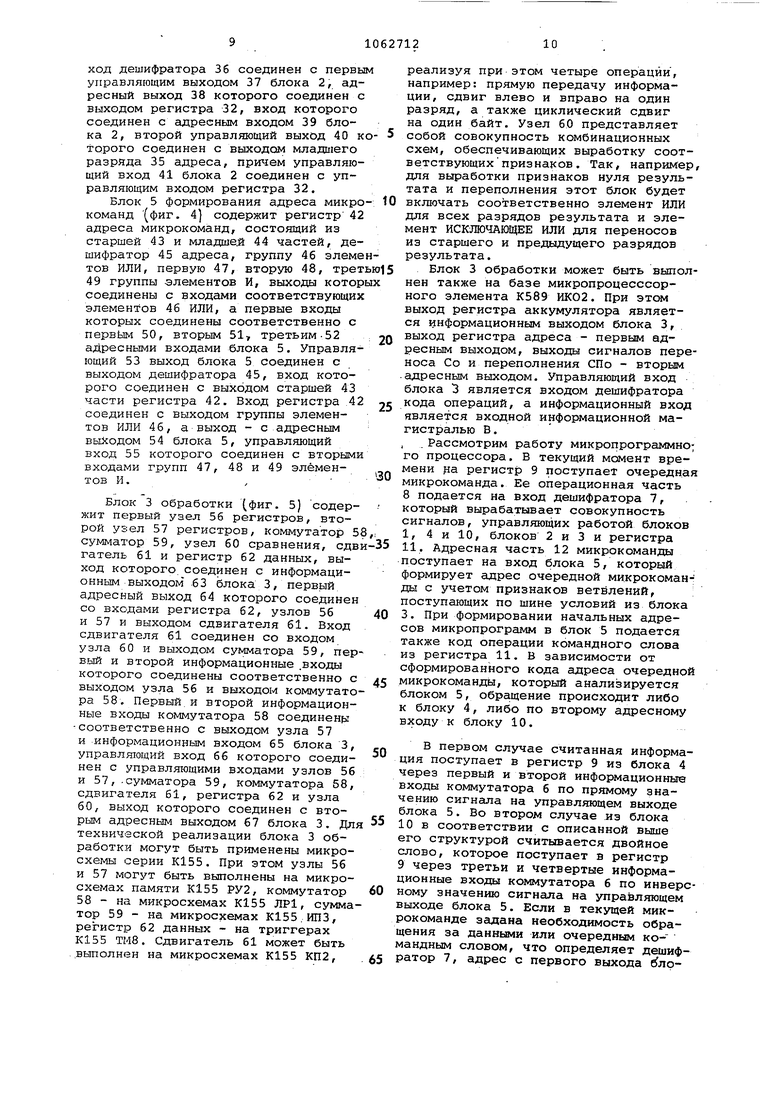

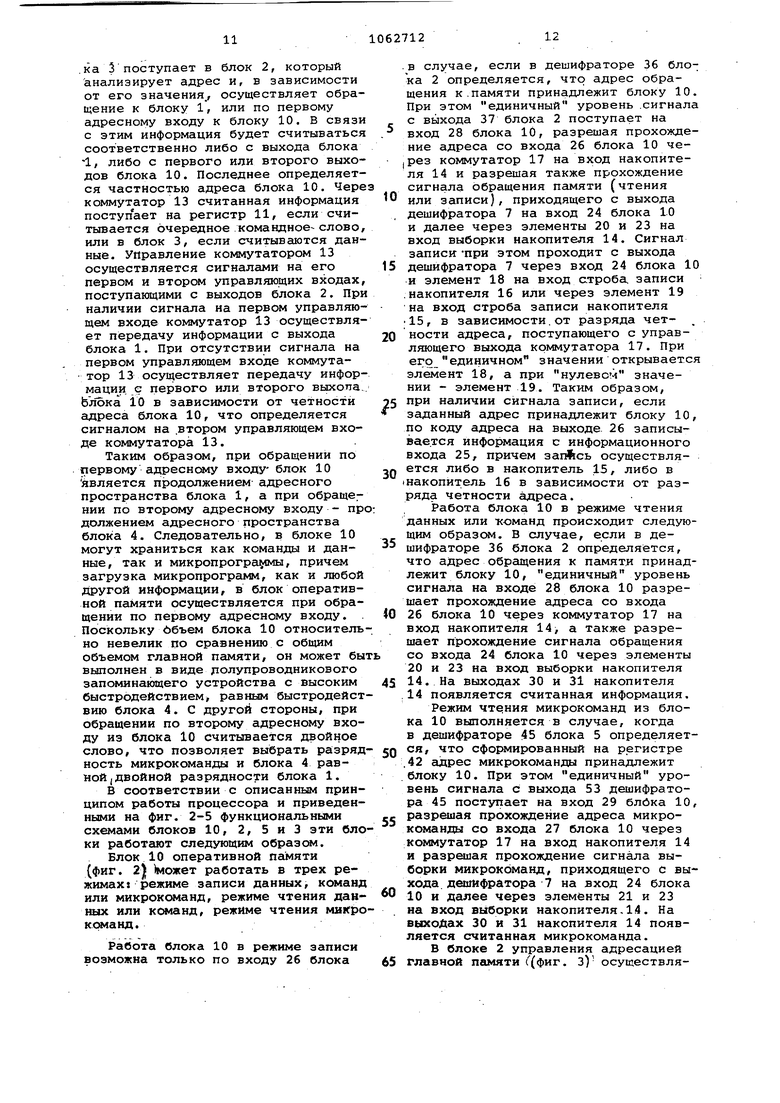

На фиг. 1 представлена структурная схема микропрограммного процесcopaj на фиг. 2 - функциональная схема блока оперативной памяти/ на фиг. 3 - схема блока управления -адресацией главной памяти на фиг. 4схема блока формирования адреса микрокоманд; на фиг. 5 - схема блока обработки.

Микропрограммный процессор содержит блок 1 главной памяти, адресный и информационный входы которого соединейл соответственно с адресным выходом блока 2 управления адреса,цией -главной памяти и информационным выходом блока 3 обработки, и блок. 4 микропрограммной памяти, вход которого соединен с адресным выходом блока 5 формирования адреса микрокоманд, а первый и второй выходы - с первым и вторым информационными входами коммутатора 6 микрокоманд (фиг. 1). Процессор содержит также дешифратор 7 управляющих сигна лов, вход- которого соединен с выходом операционной части 8 регистра 9 микрокоманд, а выходы - с первыми управляющими входами блоков 1 и 4, блока 10 оперативной памяти, блока 3, регистра 11 команд, блока 5 и блока 2. Адресный вход блока 2 соеди нен Я первым адресным выходом блока 3} второй адресный выход ко-. ,торого соединен с первым адресным входом блока 5, с вторым и третьим адресными входами которого соединены соответственно выходы регистра 11 и адресной части 12 регистра 9, вход последнего из которых соединен с выходом коммутатора 6 микрокоманд. Информационный, первый и второй адреные входы блока 10 оперативной памяти соединены соответственно с информационным и адресным входами блока 1 и входом блока 4. Кроме того, процессор содержит коммутатор 13 данных, выход которого соединен с информационными входами блока 3 и ре- гистра 11, первый управляющий вход ,которого соединен с вторым управляющим входом блока 10 и с первым управ ляЬщим выходом блока 2, второй управляющий выход которого соединен с вторым управляющим входом коммутатора 13. При этом первый информационный вход коммутатора 13 соединен с выходом блока 1, а второй и третий информационные входы соединены соответственно с первым и вторым выхода.ми блока 10 и с третьим и четвертым информационными входами коммутатора б,. причем управляющий вход последнего соединен с управляющим выходом блока 5 и с третьим управляющим вхо.дом блока 10.

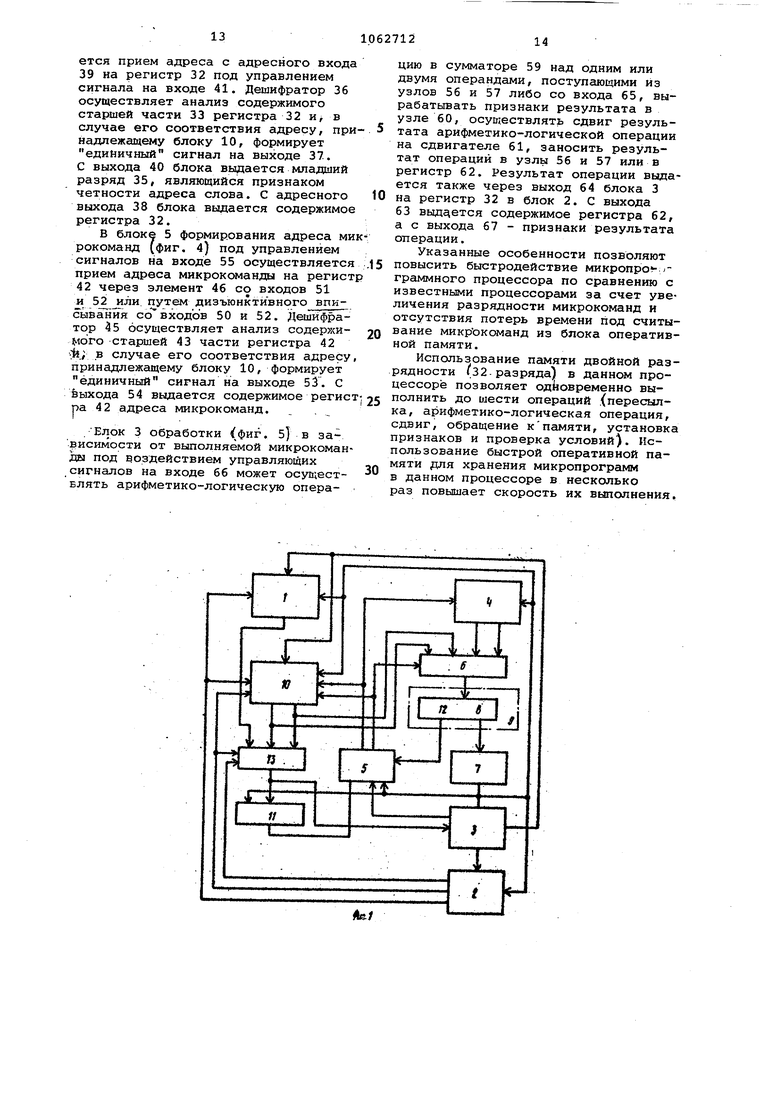

Блок 10 оперативной памяти содержит накопитель 14, разрядность которого равна двойной разрядности блока 1 и состоящий из накопителя 15 старшего слова и накопителя 16 младшего слова (фиг. 2}. Блок 10 содержит также коммутатор 17 адреса, первый 18, второй 19, третий 20, четвертый 21 элементы И, элемент 22 НЕ, элемент 23 ИЛИ, выход которого соединен с первым управляющим входом, являющимся входом выборки, накопителя 14, адресный вход которого соединен с адресным выходом коммутатора 17. Управляющий выход коммутатора 17, являющийся выходом младшего разряда адреса, соединен с первым входом элемента 18 и входом элемента 22, выход которого соединен с первым входом элемента 19, второй вход которого, являющийся входом сигнала записи, соединен с первЕлм управляющим входом 24 блока 10 и с вторьом входом элемента 18, выход которого соединен с входом строба записи накопителя 16, являющимся вторым управляющим входом накопителя 14. Третий управляющий вход накопителя 14, являющийся входом строба i записи накопителя 15, соединен с выходом элемента И 19, информационный вход 25 блока 10 соединен с информационным входом накопителя.14, первый адресный вход коммутатора 17 соединен с первым адресным входом 26 блока 10, второй адресный вход 27 которого соединен с вторым адресным входом коммутатора 17. Первый управляющий вход коммутатора 17 соединен с первым входом элемента И 20 и вторым управляющим входом 28 блока 10, третий управляющий вход 29 которого соединен с вторым управляющим входом коммутатора 17 и первым входом эле.мента 21, выход которого соединен с первым входом элемента 23. Второй вход элемента 23 соединен с выходом элемента 20, второй вход которого, являющийся признаком обращения к памяти за оперативной информацией, соединен с входом 24 блока 10. При этом второй вход элемента 21, являрщийся признаком обращения за микропрограммной информацией, соединен с входом 24 блока 10, первый 30 и . второй 31 выходы которого соединены соответственно с выходами накопителя 15 и накопителя 16. Накопитель 14 может быть выполнен на интегральных полупроводниковых микросхемах К565РУ2А.

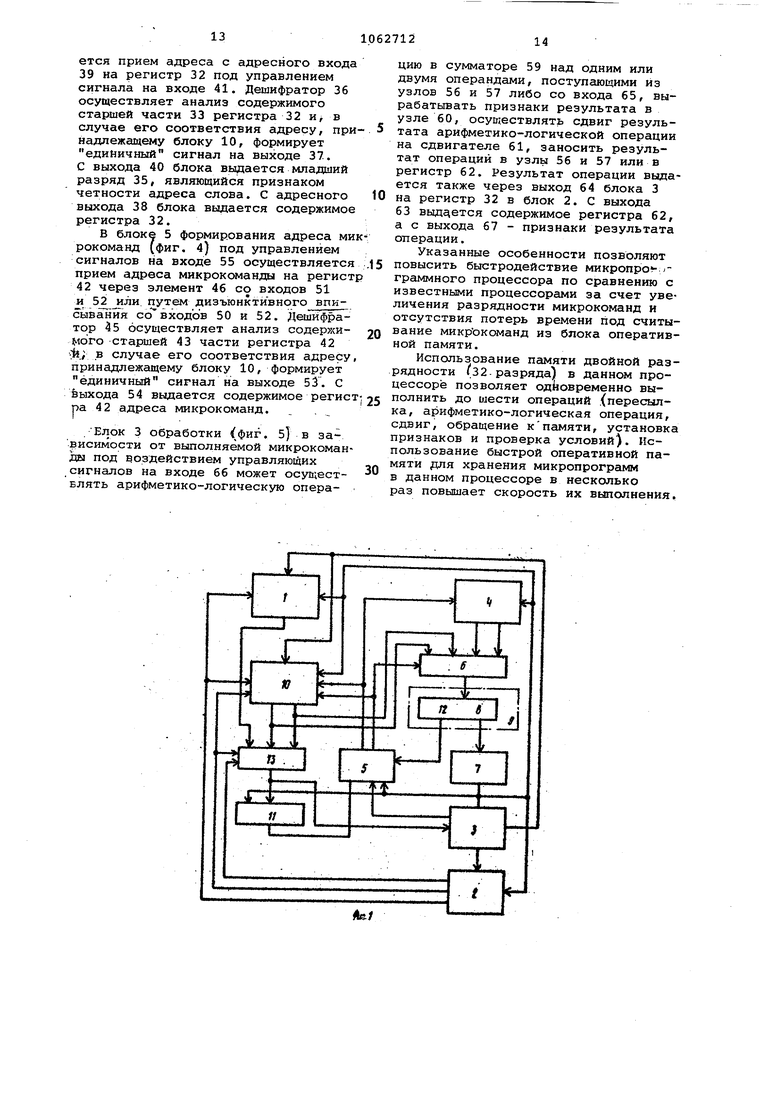

Блок 2 управления адресацией главной Пс1мяти (фиг. 3) содержит регистр 32 адреса, состоящий из старшей 33, младшей 34. частей адреса и младгиего разряда 35, дешифратор 36 адреса, вход которого соединен с выходом старшей 33 части регистра 32, а выход дешифратора 36 соединен с первым управляющим выходом 37 блока 2, адресный выход 38 которого соединен с выходом регистра 32, вход которого соединен с адресным входом 39 блока 2, второй управляющий выход 40 ко торого соединен с выходом младшего разряда 35 адреса, причем управляющий вход 41 блока 2 соединен с управляющим входом регистра 32.

Блок 5 формирования адреса микрокоманд (фиг. 4) содержит регистр 42 адреса микрокоманд, состоящий из старшей 43 и младшей 44 частей, дешифратор 45 адреса, группу 46 элементов ИЛИ, первую 47, вторую 48, треть 49 группы элементов И, выходы которы соединены с входами соответствующих элементов 46 ИЛИ, а первые входы которых соединены соответственно с nepBtoM 50, вторым 51-, третьим-52 адресными входами блока 5. Управляющий 53 выход блока 5 соединен с выходом дешифратора 45, вход которого соединен с выходом старшей 43 части регистра 42. Вход регистра .42 соединен с выходом группы элементов ИЛИ 46, а выход - с адресным выходом 54 блока 5, управляющий вход 55 которого соединен с вторыми

входами групп 47, 48 И 49 элёменч.

тов и.

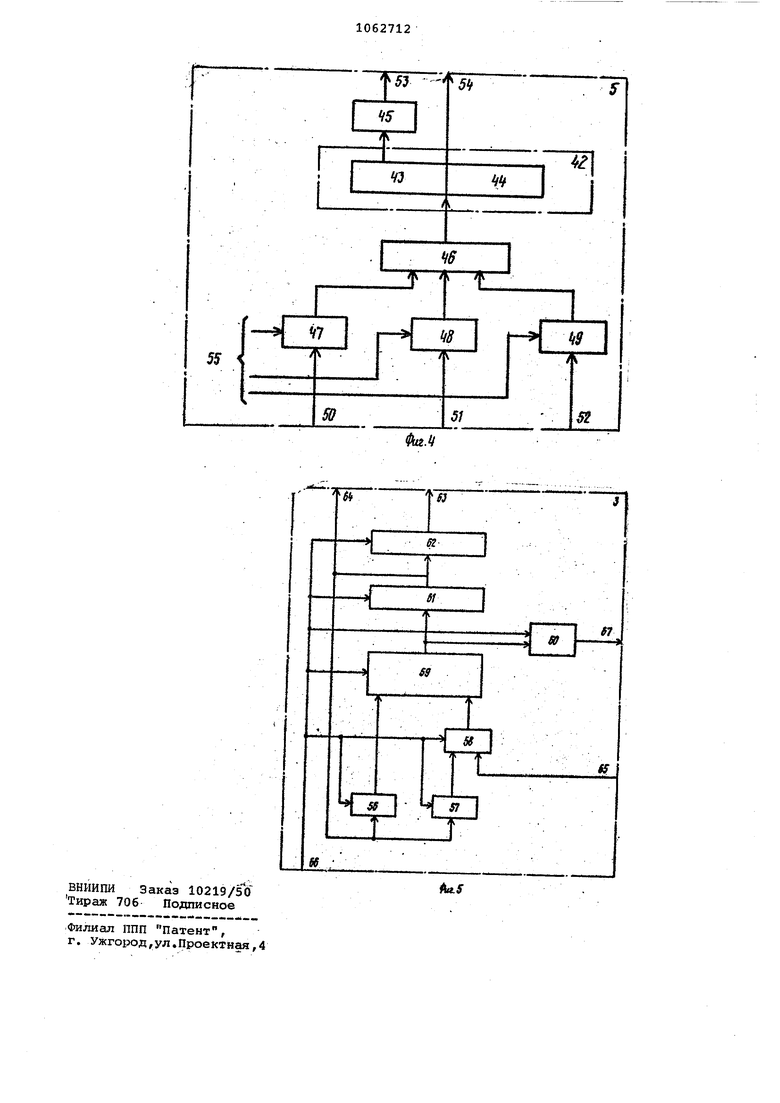

Блок 3 обработки (фиг. 5) содержит п€;рвый узел 56 регистров, второй узел 57 регистров, коммутатор 58 сумматор 59, узел 60 сравнения, сдви гатель 61 и регистр 62 данных, выход которого, соединен с информационным выходом 63 блока 3, первый адресный выход 64 которого соединен со входами регистра 62, узлов 56 и 57 к выходом сдвигателя 61. Вход сдвигателя 61 соединен со входом узла 60 и выходом сумматора 59, первый и второй информационные .входы которого соединены соответственно с выходом узла 56 и выходом коммутатора 58, Первый.и второй информационные входы коммутатора 58 соединены соответственно с выходом узла 57 и информационным входом 65 блока 3, управляющий вход 66 которого соединен с управляющими входами узлов 56 и 57, .сумматора 59, коммутатора 58, сдвигателя 61, регистра 62 и узла 60, выход которого соединен с вторым адресным выходом 67 блока 3. Для технической реализации блока 3 обработки могут быть применены микросхемы серии К155. При этом узлы 56 и 57 могут быть выполнены на микросхемах памяти К155 РУ2, коммутатор 58 - на микросхемах К155 ЛР1, сумматор 59 - на микросхемах К155.ИПЗ, регистр 62 данных - на триггерах К155 . Сдвигатель 61 может быть выполнен на микросхемах К155 КП2,

реализуя при этом четыре операции, например: прямую передачу информации, сдвиг влево и вправо на один разряд, а также циклический сдвиг на один байт. Узел 60 представляет собой совокупность комбинационных схем, обеспечивающих выработку соответствующих признаков. Так, например для выработки признаков нуля результата и переполнения этот блок будет включать соответственно элемент ИЛИ для всех разрядов результата и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ для переносов из старшего и предыдущего разрядов результата.

Блок 3 обработки может быть выполнен также на базе микропроцесссорного элемента К589 ИК02. При этом выход регистра аккумулятора является информационным выходом блока 3, выход регистра адреса - первым адресным выходом, выходы сигналов переноса Со и переполнения СПо - вторым адресным выходом. Управляющий вход блока 3 является входом дешифратора кода операций, а информационный вход является входной информационной магистралью В.

. Рассмотрим работу микропрограммно го процессора. В текущий момент времени ра регистр 9 поступает очередна микрокоманда. Ее операционная часть

8подается на вход дешифратора 7, который вырабатывает совокупность сигналов, управляющих работой блоков

I,4 и 10, блоков 2 и 3 и регистра

II.Адресная часть 12 микрокоманды поступает на вход блока 5, который формирует адрес очередной микрокоманды с учетом признаков ветвлений, поступающих по шине условий из блока 3. При формировании начальных адресов микропрограмм в блок 5 подается также код операции командного слова из регистра 11. В зависимости от сформированного кода адреса очередно микрокоманды, который анализируется блоком 5, обращение происходит либо

к блоку 4, либо по второму адресному входу к блоку 10.

В первом случае считанная информация поступает в регистр 9 из блока 4 через первый и второй информационные входы коммутатора 6 по прямому значению сигнала на управляющем выходе блока 5. Во втором случае из блока 10 в соответствии с описанной выше его структурой считывается двойное слово, которое поступает в регистр

9через третьи и четвертые информационные входы коммутатора 6 по инверсному значению сигнала на упра1вляющем выходе блока 5. Если в текущей микрокоманде задана необходимость обращения за данными или очередным командным словом, что определяет дешифратор 7, адрес с первого выхода ло.ка 3 поступает в блок 2, который анализирует адрес и, в зависимости от его значения., осуществляет обращение к блоку 1, или по первому адресному входу к блоку 10. В связи с этим информация будет считываться соответственно либо с выхода блока -1, либо с первого или второго выходов блока 10. Последнее определяется частностью адреса блока 10. Чере коммутатор 13 считанная информация поступает на регистр 11, если считывается очередное командное- слово, или в блок 3, если считываются данные. Управление коммутатором 13 осуществляется сигналами на его первом и втором управляющих входах, поступающими с выходов блока 2. При наличии сигнала на первом управляющем входе коммутатор 13 осуществляет передачу информации с выхода блока 1. При отсутствии сигнала на первом управляющем входе коммутатор 13 осуществляет передачу информации с первого или второго выхопа.. Ьлока iO в зависимости от четности адреса блока 10, что определяется сигналом на .втором управляющем входе коммутатора 13.

Таким образом, при обращении по первому адресному входу блок 10 Является продолжением адресного пространства блока 1, а при обращении по второму адресному входу - про должением адресного пространства блока 4. Следовательно, в блоке 10 могут храниться как команды и данные, так и микропрогра 1мы, причем загрузка микропрограмм, как и любой другой информации, в блок оперативной памяти осуществляется при обращении по первому адресному входу. Поскольку ббъем блока 10 относительно невелик по сравнению с общим объемом главной памяти, он может быт выполнен в виде полупроводникового запоминающего устройства с высоким быстродействием, равным быстродействию блока 4. С другой стороны, при обращении по второму адресному входу из блока 10 считывается двойное слово, что позволяет выбрать разрядность микрокоманды и блока 4 равной, двойной разрядности блока 1.

В соответствии с описанным принципом работы процессора и приведенными на фиг. 2-5 функциональными схемами блоков 10, 2, 5 и 3 эти блоки работают следующим образсял. Блок 10 оперативной памяти (фиг. 2) Сможет работать в трех режимах: режиме записи данных, команд или микрокоманд, режиме чтения дан ных или команд, режиме чтения микрокс 1анд.

Работа блока 10 в режиме записи возможна только по входу 26 блока

В случае, если в дешифраторе 36 блока 2 определяется, что адрес обращения к-памяти принадлежит блоку 10 При этом единичный уровень .сигнал с выхода 37 блока 2 поступает на вход 28 блока 10, разрешая прохождение адреса со входа 26 блока 10 че|рез коммутатор 17 на вход накопителя 14 и разрешая также прохождение сигнала обращения памяти (чтения или записи), приходящего с выхода дешифратора 7 на вход 24 блока 10 и далее через элементы 20 и 23 на вход выборки накопителя 14. Сигнал записи -при этом проходит с выхода дешифратора 7 через вход 24 блока 1 и элемент 18 на вход строба, записи накопителя 16 или через элемент 19 на вход строба записи накопителя 15, в зависимости,от разряда четности адреса, поступающего с управляющего выхода коммутатора 17. При его единичном значении открываетс элемент 18, а при нулевом значении - элемент 19. Таким образом, при наличии сигнала записи, если заданный адрес принадлежит блоку 10 по коду адреса на выходе. 26 записывается информация с информационного входа 25, причем загЛсь осуществляется либо в накопитель 15, либо в (Накопитель 16 в зависимости от разряда четности адреса.

Работа блока 10 в режиме чтения данных или команд происходит следующим образс 1. В случае, если в дешифраторе 36 блока 2 определяется, что адрес обращения к памяти принадлежит блоку 10, единичный уровень сигнала на входе 28 блока 10 разрешает прохождение адреса со входа 26 блока 10 через коммутатор 17 на вход накопителя 14, а также разрешает прохождение сигнала обращения со входа 24 блока 10 через элементы 20 и 23 на вход выборки накопителя 14. На выходах 30 и 31 накопителя 14 появляется считанная информация. Режим чтения микрокоманд из блока 10 выполняется в случае, когда в дешифраторе 45 блока 5 определяется, что сформированный на регистре .42 адрес микрокоманды принадлежит блоку 10. При этом единичный уровень сигнала с выхода 53 дешифратора 45 поступает на вход 29 блика 10 разрешая прохождение адреса микрокоманды со входа 27 блока 10 через коммутатор 17 на вход накопителя 14 и разрешая прохождение сигнала выборки микрокоманд, приходящего с выхода, дешифратора 7 на вход 24 блока 10 и далее через элементы 21 и 23 на вход выборки накопителя.14. На вмхоАах 30 и 31 накопителя 14 появляется считанная микрокоманда.

В блоке 2 управления адресацией главной памяти ((фиг. З) осуществляется прием адреса с адресного входа 39 на регистр 32 под управлением сигнала на входе 41. Дешифратор 36 осуществляет анализ содержимого старшей части 33 регистра 32 и в случае его соответствия адресу, при надлежащему блоку 10, формирует единичный сигнал на выходе 37. С выхода 40 блока выдается младший разряд 35, являющийся признаком четности адреса слова. С адресного выхода 38 блока выдается содержимое регистра 32.

В блоке 5 формирования адреса мирокоманд (фиг. 4) под управлением сигналов на входе 55 осуществляется прием адреса микрокоманды на регист 42 через элемент 46 со входов 51 и 52 кт путем дизъюнктивного впксывания со входов 50 и 52. Дешифратор 45 осуществляет анализ содержимого старшей 43 части регистра 42 ij; в случае его соответствия адресу принадлежащему блоку 10, формирует единичный сигнал на выходе 53. С выхода 54 выдается содержимое регис па 42 адреса микрокоманд. ,

Блок 3 обработки (фиг. 5) в зависимости от выполняемой микрокоманда под воздействием управляюйих сигналов на входе 66 может осущестБлять арифметико-логическую операцию в сумматоре 59 над одним или двумя операндами, поступающими из узлов 56 и 57 либо со входа 65, вырабатывать признаки результата в узле 60, осуществлять сдвиг результата арифметико-логической операции на сдвигателе 61, заносить результат операций в узлы 56 и 57 или в регистр 62. Результат операции выдается также через выход 64 блока 3 на регистр 32 в блок 2. С выхода 63 выдается содержимое регистра 62, а с выхода 67 - признаки результата операции.

Указанные особенности позволяют повысить быстродействие микропро - граммного процессора по сравнению с известными процессорами за счет увеличения разрядности микрокоманд и отсутствия потерь времени под считывание микрокоманд из блока оперативной памяти.

Использование памяти двойной разрядности /32 разряда) в данном процессоре позволяет одновременно выполнить до шести операций .{пересылка, арифметико-логическая операция, сдвиг, обращение кпамяти, установка признаков и проверка условий). Использование быстрой оперативной памяти для хранения микропрограмм в данном процессоре в несколько раз повышает скорость их выполнения.

I;

ЧЗп

w

$

w

г/

25

J t

W

/7

77

4f

/tf

r/7

7У

-Й

fZ

Г-

Ц

75

7/

) r f 7

Л

/

HO

J

J5

J J

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США 3792441, ,кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 3859636, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

Авторы

Даты

1983-12-23—Публикация

1982-10-18—Подача