1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в цифровых измерительных устройствах, в системах автоматического контроля и диагностики, телеметрических системах и т. п.

По основному авт. св. № 517997 известен двухканальный аналого-цифровой преобразователь, содержащий в каждом канале устройство сравнения, делитель напряжения, входы которого соединены с ключами, и триггерный регистр, входы которого соединены с входами ключей, нулевые входы- с элементами совпадения, элементы запрета, а в каждом разряде -триггер, два элемента запрета, элемент ИЛИ и элемент совпадения. При этом единичный вход триггера подключен к соответствующему выходу одного из триггеров данного разряда, а нулевой - к выходу элемента совпадения, входы которого соединены с единичными выходами триггеров смелшого младшего разряда. Выход триггера подключен к первым входам элементов совпадения и запрета данного разряда, вторые входы которых соединены попарно и подключены к выходам элементов запрета, своими выходами подключенных к выходам устройств сравнения. Третьи входы элементов запрета соединены с единичными выходами соответствующих триггеров данного разряда, а выходы через элемент ИЛИ - с единичными входами триггеров смежного младшего разряда ,2.

Недостаток устройства состоит в невысокой надежности работы устройства и достоверности получаемой информации.

Целью изобретения является увеличение достоверности контроля на каждом такте преобразования.

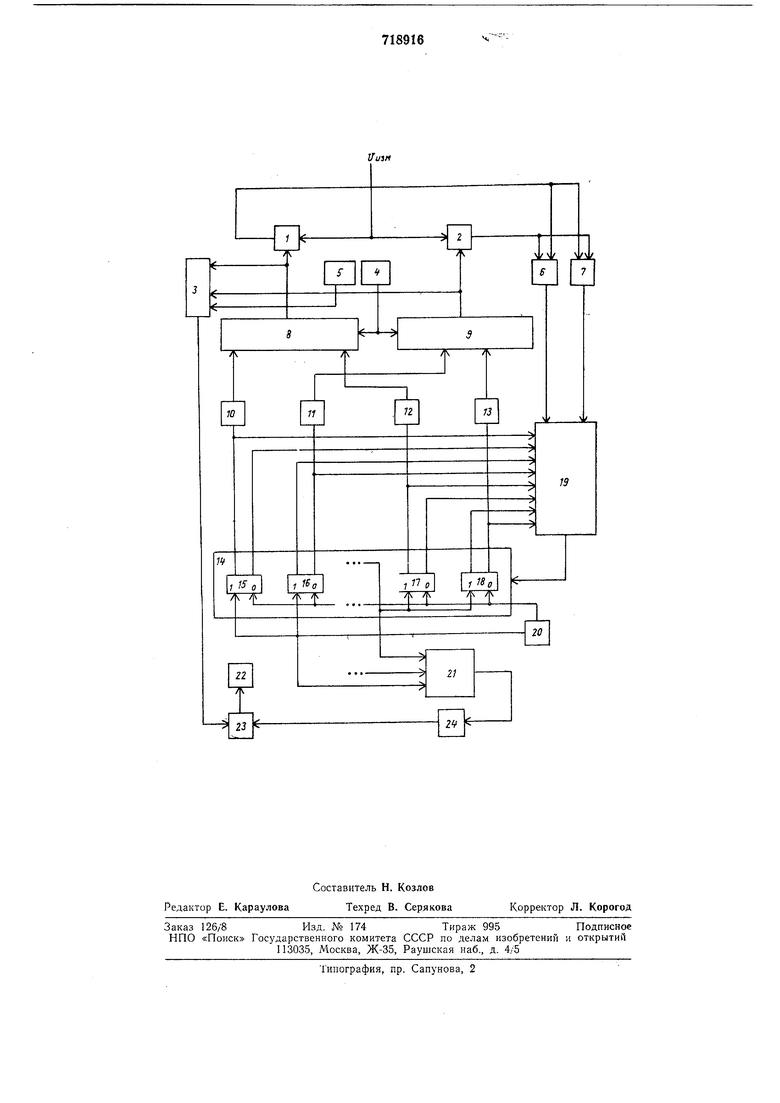

Предлагаемый двухканальный преобразователь содержит в каждом канале устройство сравнения, делитель напряжения, входы которого соединены с ключами, и триггерный регистр, входы которого соединены с входами ключей, нулевые входы - с элементами совпадения, а также дополнительные элементы запрета, а в каждом разряде - дополнительный триггер, два элемента запрета, элемент ИЛИ и дополнительный элемент совпадения. При этом единичный вход дополнительного триггера подключен к соответствующему выходу одного из триггеров данного разряда, а нулевой - к выходу дополнительного элемента совпадения, входы которого соединены с единичными выходами триггеров смежного младшего разряда. Выход дополнительного триггера подключен к первым входам элементов совпадения и запрета данного разряда, вторые входы которых соединены попарно и подключены к выходам дополнительных элементов запрета, своимп входами подключенных к выходам устройств сравнения. Третьи входы элементов запрета соединены с единичными выходами соответствующих триггеров данного разряда, а выходы через элемент ИЛИ - с единичными входами триггеров смежного младшего разряда. Осооенностью устройства является то, что в него введены донолнительные устройства сравнения и источник эталонного напряжения, элементы ИЛИ, И и элемент задержки, блок логики, вход которого соединен с выходом элемента И, один вход которого через элемент задержки и элемент ИЛИ подключен к единичным входам первого и второго триггеров каждого разряда триггерного регистра, второй вход через дополнительное устройство сравнения соединен с выходами делителей напряжения и выходом дополнительного источника эталонного напряжения. На чертеже представлена функциональная схема устройства. Устройство содержит устройства 1, 2 сравнения, дополнительное устройство 3, источник 4 эталонного напряжения t/ai, дополнительный источник 5 эталонного напряжения t/эт - мл.р., элементы 6, 7 запрета, делители 8, 9 напряжения, ключи 1и- 13, триггерный регистр 14 с триггерами 15-18, логическую схему 19, устройство 20 управления, элемент ИЛИ 21, блок 22 логики, элемент И 23, элемент 24 задержки. Измеряемое напряжение поступает на первые входы схем 1 и 2, вторые входы которых подключены к выходам делителей 8 и 9 соответственно. Входы ключей 10, 12 соответственно соединены с единичными выходами триггеров 15, 17, регистра 14, входы ключей 11, 12 - соответственно с нулевыми выходами триггеров 16, 18 регист ра 14. Единичные и нулевые выходы триггеров 15-18 соответственно соединены с входами логической схемы 19, остальные входы которой соответственно связаны с выходами элементов 6, 7 запрета, входы которых подключены к выходам двух устройств сравнения. Блок 19 управляет работой регистра 14. Устройство работает следуюш,им обраВ исходном состоянии триггеры 15-18 регистра 14 устанавливаются от устройства 20 импульсом «установка «О и компенсационное напряжение на втором входе устройства 1 сравнения равно нулк), а компенсационное напряжение на втором входе устройства 2 сравнения - максимальному компенсационному напряжению. Во время нреобразования компенсационные напряжения изменяются противофазно. В процессе поразрядного уравновешивания нанряжения на выходах делителей 8 и 9 .приближаются по амплитуде к величине напряжения t/изм н в последнем такте уравновешивания становятся равными этому напряжению с погрешностью, не превышаюш,ей величины младшего разряда компенсационного напряжения. На каждом такте преобразования производится контроль работы преобразователей кода в напряжение. При этом единичные эходы триггеров 15, 16 и 17, 18 попарно соединены между собой и соответственно подсоединены к входам элемента 21. Сигнал с выхода элемента 21 через элемент 24 поступает на вход элемента 2б, который производит опрос устройства 3. При работоспособном состоянии преобразователей на выходе устройства 3 импульс отсутствует. При неработоспособном состоянии преобразователей (например, обрыв или КЗ резисторов, ключей) на выходе устройства 3 формируется импульс, который через элемент 23 поступает в блок 22 как импульс «не годен, который индицируется, регистрируется, используется для восстановления устройства (при наличии резерва) для реконфигурации схемы и т. п. При этом увеличивается достоверность контроля на Каждом такте преобразования в целом. Формула изобретения Двухканальный аналого-цифровой преобразователь по авт. св. № 517997, отличаюш,нйся тем, что, с целью повышения достоверности контроля на каждом такте преобразования, в него введены дополнительные устройства сравнения и источник эталонного напряжения, элементы ИЛИ, И и элемент задержки, блок логики, вход которого соединен с выходом элемента И, один вход которого через элемент задержки и элемент ИЛИ подключен к единичным входам первого и второго триггеров каждого разряда триггерного регистра, второй вход через дополнительное устройство сравнения соединен с выходами делителей напряжения и выходом дополнительного источника эталонного напряжения. ., Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 517997, кл. Н ОЗК 13/17, 1976.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухканальный аналого-цифровой преобразователь | 1973 |

|

SU517997A1 |

| Аналого-цифровой преобразователь с самоконтролем | 1980 |

|

SU886236A2 |

| Двухканальный аналого-цифровой преобразователь | 1983 |

|

SU1106010A1 |

| Двухканальный аналого-цифровой преобразователь | 1981 |

|

SU995314A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство параллельно-последователь-НОгО АНАлОгО-цифРОВОгО пРЕОбРАзОВА-Ния C САМОКОНТРОлЕМ | 1979 |

|

SU815904A1 |

| Устройство аналого-цифрового преобра-зОВАНия | 1979 |

|

SU809554A1 |

| Аналого-цифровой преобразователь с цифровой коррекцией погрешностей | 1978 |

|

SU788374A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1388989A2 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1991 |

|

RU2020751C1 |

Авторы

Даты

1980-02-29—Публикация

1978-07-10—Подача