(34) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ПОСЛЕДОВАТЕЛЬНЫМ ДОСТУПОМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с последовательным доступом | 1982 |

|

SU1070606A2 |

| Ассоциативно-адресное оперативное запоминающее устройство | 1987 |

|

SU1451773A1 |

| Запоминающее устройство | 1977 |

|

SU733021A1 |

| Устройство для приема информации | 1983 |

|

SU1088051A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| Устройство для коррекции ошибок | 1987 |

|

SU1541677A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

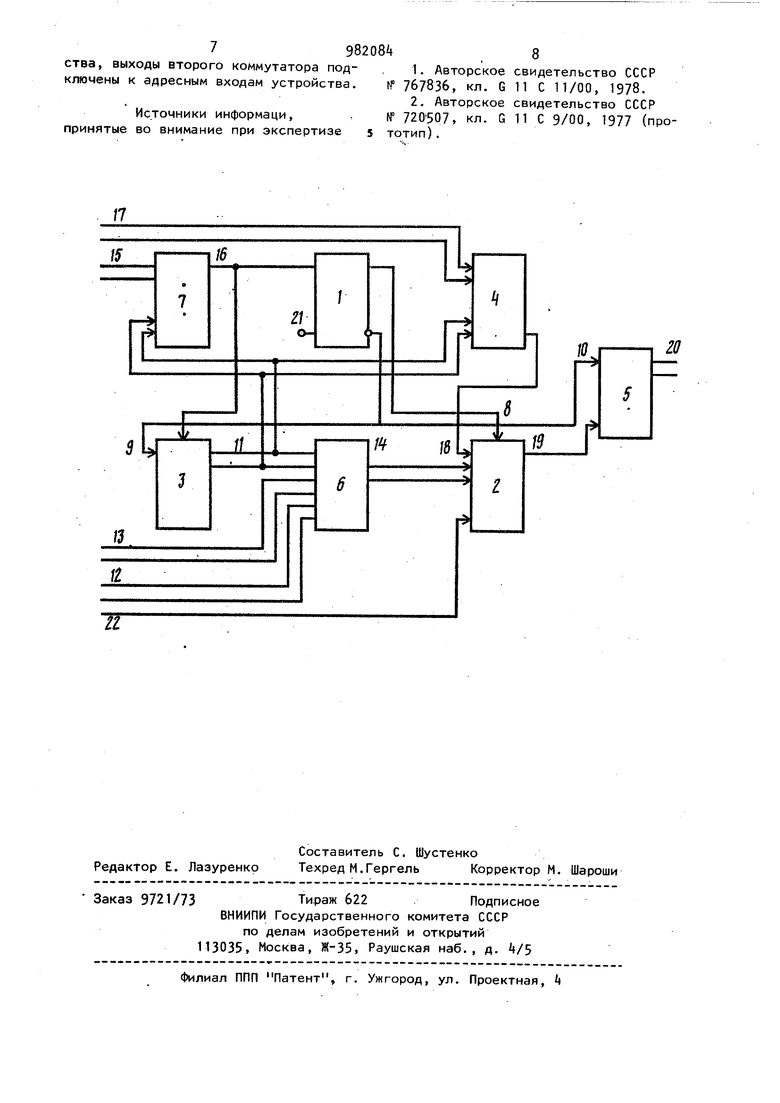

Изобретение относится к вычислительной технике, а именно к запомина.ющим устройствам. Известно запоминающее устройство, содержащее две матрицы памяти, входные и выходные элементы И, блок управления, входной и вых.одной регистр, два дешифратора, первый и второй счетчики 1 Недостатком данного устройства являются ограниченные функциональные возможности, связанные с постоянной адресностью запоминающего устройства и постоянной разрядностью обрабатываемых слов. Наиболее близким техническим решением к изобретению является запоминающее устройство, содержащее блок памяти последовательного типа, информационные входы и выходы которого подключены соответственно к входным и выходным кодовым шинам, счетчик чисел выходы которого подключены к соответствующим входам первого элемента И, выход каторого подключен к управляющему входу блока памяти последовательного типа и входу второго элемента И, выход которого подключен к одному тановочному входу триггера, другой установочный вход кот.орого подключен к шине считывания и тактовую шину, также оно содержит два элемента ИЛИ, инвертор и формирователь пачек импульсов, один из входов которого подключен к шине записи, другой вход - к тактовой шине, один из входов которого подключен к шине записи, другой вход - к тактовой шине, один из входов формирователя пачек импульсов подключен к входу первого элемента ИЛИ и входу второго элемента И, а выход первого элемента ИЛИ подключен к тактовому входу блока памяти последовательного типа, другой выход формирователя пачек импульсов подключен к входу второго элемента ИЛИ и через инвертор - к входу второго элемента И, другие входы первого и второго элементов ИЛИ подключены к шине считывания С 23Однако это устройство не может быть использовано в системах с изменяющей ся разрядностью и адресностью. , Цель изобретения - расширение области применения устройства за счет возможности изменения разрядности и адресности запоминающего устройства. Поставленная цель достигается тем, что запоминающее устройство с последовательным доступом,, содержащее накопитель, информационный вход которого подключен к выходу первого коммутатйра, управляющий вход накопителя к одному из выходов генератора синхро сигналов, выходнакопителя подключен к одному из входов регистра, другой вход которого подключен к другому выходу генератора синхросигналов и к одному из входов адресного счетчика, выходы регистра являются выходами уст ройства, одни входы первого коммутатора являются информационными входами устройства, а другие входы первого коммутатора подключены к выходам адресного счетчика, содержит схему сравнения, одни вход4| которой являются управляющими входами устройства, другие входы схемы сравнения подключены к выходам адресного счетчика, а выход схемы сравнения подключен к дру гому входу адресного счетчика и к вхо ду генератора синхросигналов, и второй коммутатор, одни из информацион-г. ных входов которого подключены к выходам адресного счетчика, другие информационные входы и управляющие входы второго коммутатора являются .соответственно адресными входами и управляющими входами устройства, выходы второго коммутатора подключены к адресным входам устройства. На чертеже изображена схема запоминающего устройства с последовательным доступом. Устройство содержит генератор 1 синхросигналов, накопитель 2, адресный счетчик 3, информационный коммутатор k, регистр 5, адресный коммутатор 6 и схему 7 сравнения. Прямой и инверсный выходы генератора 1 синхросигналов соответственно подключены к управляющему входу 8 на копителя 2, являющимся входом выбора кристалла одноразрядного накопителя 2 и управляющим входам 9 и 10 соответс венно адресного счетчика 3 и регистра 5. Выходы 11 адресного счетчика 3 соединены с группой информационных входов адресного коммутатора 6, с одним из входов схемы 7 сравнения и с управляющими входами коммутатора 4. Вторая группа входов и управляющие входы коммутатора 6 соответственно подключены к адресным входам 12 устройства и входам 13 управления адресностью. Выходы 14 коммутатора соединены с адресными входами накопителя 2, управляющие входы 15 и выход 16, схема 7 сравнения соединены соответственно с входами управления начальной установки и входами начальной установки генератора 1 синхросигналов и адресного счетчика 3. Информационные входы коммутатора 4 подключены к информационным входам 17, а его выход соединен с информационным входом 18 накопителя 2. Выход накопителя 2 соединен с информационным входом регистра 5, выходы которого соединены с выходными шинами 20. Запуск генератора 1 синхросигналов осуществляется по входу 21, а управление операциями записи-чтения - по входу 22. Запоминающее устройство с последовательным доступом имеет три режима работы: режим записи информации, режим чтения информации и режим хранения. Пусть одноразрядный накопитель 2 имеет п адресных входов. Перед началом работы на шине начальной установки 15 и шине управления адресностью 13 формируются коды управления, в соответствии с которыми из общего числа п адресных вхЬдов- накопителя 2 непосредственно к шине адреса обращения 12 подключается через коммутатор 4 (n-k) адресных входов, а К оставших- . ся - к выходам адресного счетчика 3. В режиме записи на вход 21 подается сигнал признака запуска, в соответствии с которым генератор 1 синхросигналов формирует серию синхросигналов на своих прямом и инверсном выходах. Сигналы с инверсного выхода поступают на счетный вход адресного счетчика 3 в соответствии с которыми на его выходах 11 формируется последовательный ряд К-разрядных двоичных кодов. Эти коды через адресный коммутатор 6 поступают на К адресных входов одноразрядного накопителя 2, на (n-k) оставшиеся входы которого через коммутатор 6 поступает неизмен598ный код по входам 12 адреса обращения Код, поступающий по входам Т2 в режиме обращения, является статическим адресом, определяющим 2k адресную область ячеек памяти одноразрядного накопителя 2, к которым осуществляется динамическое обращение в соответствии с последовательностью К-разрядных кодов динамического адреса обращения. Информационный коммутатор подключает к информационному вхЪду 18 соответ ствующий бит записываемого слова с .входов 17. Одновременно с поступлением каждого бита информации на информационный вход 18 и на управляющий вход 8 подается сигнал с прямого выхода генератора синхросигналов 1, ра.з решающий выбор кристалла, а на вход записи-чтения поступает сигнал призна ка записи. Схема 7 сравнения при совпадении кодовых комбинаций на его вхо дах 15 и на выходах счетчика 3 на выходе 16 вырабатывает сигнал начальной установки для генератора 1 синхросигналов и адресного счетчика 3.Кмоменту формирования сигнала начальной установки в накопителе 2 заключена запись 2k разрядного слова по 2{n-k) ад ресу. В режиме чтения на вход 21 также подается сигнал признака запуска, в соответствии с которым генератор синхросигналов 1 формирует серию синхросигналов на своих прямом и инверсном выходах. В это же время на вход 22 подается сигнал признака чтения. Сигналы с инверсного выхода генератора 1 синхросигналов поступают на счетный вход 9 адресного счетчика 3 и на вход 10 регистра 5. В соответствии с синхросигналом на выходах 11 адресного счетчика 3 формируется последовательный ряд К-разрядных двоичных кодов. Эти коды через переключатель адресных шин поступают на К-адресных входов накопителя 2, а на (n-k) оставшиеся входы которого через коммутатор 6 поступает неизменный код адреса с входов 12 адреса обращения. По этому адресу производится чтение К-разрядно го слова. Считанная информация с выхода 19 в последовательном коде поступает на вход регистра 5 и с помощью управляющего входа подается на выходы 20. Схема 7 сравнения при совпадении кодовых комбинаций на его входах 15и на выходах счетчика 3 на выходе 16формирует сигнал начальной установки, что является признаком окончания it чтения. По завершении режима режима чтения по адресу 2 в регистре 5 размещено считанное 2 разрядное слово, которое поступает на выходы 20. Предлагаемое запоминающее устройство с последовательным доступом обладает более широкой областью применения по сравнению с известными и может быть использовано в тех устройствах, где возникает необходимость побитового изменения разрядности обрабатываемых слов, например в лабораторных условиях при проектировании и от ладке новых средств вычислительной техники. Данное свойство запоминающего устройства С последовательным доступом позволяет снизить затраты на макетирование каждого нового типа запоминающего устройства. Формула изобретения Запоминающее устройство с последовательным доступом, содержащее накопитель , информационный вход которого подключен к выходу первого коммутатора, управляющий вход накопителя - к одному из выходов генератора синхросигналов, выход накопителя подключен к одному из входов регистра, другой вход которого подключен к другому выходу генератора синхросигналов и к одному из входов адресного счетчика, , выходы регистра являются выходами устройства, одни входы первого коммутатора являются информационными входами устройства, а другие входы первого коммутатора подключены к выходам адресного счетчика, отличающееся тем, что, с целью расширения области применения за счет возможности изменения разрядности и адресности запоминающего устройства, оно содержит схему сравнения, одни входы которой являются управляющими входами устройства, другие входы схемы сравнения подключены к выходам адресного счетчика, выход схемы сравнения подключен к другому входу адресного счетчика и входу генератора синхросигналов, и второй коммутатор, одни из информационных входов которого подключены к выходам адресного счетчика, другие информационные входы и управляющие входы второго коммутатора являются соответственно адресными входами и управляющими входами устрой79820848

ства, выходы второго коммутатора под- , 1. Авторское свидетельство СССР ключены к адресным входам устройства. 767836, кл. G 11 С 11/00, 1978.

Источники информаци, . N 720507, кл. G 11 С 9/00, 1977 (пропринятые во внимание при экспертизе s тотип).

Авторы

Даты

1982-12-15—Публикация

1981-05-28—Подача