1

Изобретение относится к импульсной технике и может быть использовано в автоматике и вычислительной технике.

Известно пересчетное устройство с коэффициентом счета 2 + 1, со- 5 держсццее счетчик на последовательно соединенных.триггерах, дополнительный триггер, дешифратор и инвертор til . Ему свойственна недостаточно высокая надежность.10

Наиболее близким к изобретению по технической сущности является делитель частоты следования импульсов, реализующий метод безвентильного проектирования делителей с коэффициен- 5 том деления К 2 + 1,содержащий последовательно соединенные триггеры, число которых зависит от величины коэффициента делений и дополняющий I-Kt-триггер, причем счетные 20 входы дополняющего триггера и триггера младшего разряда объединены с тактовым входом делителя, прямой выход триггера младшего разряда связан с 1-входом триггера последующего разря-25 да, а инверсный выход дополнительного триггера соединен с 1-входом триггера младшего разряда М ,

Целью изобретения является расши12ение диапазона коэффициента деления зо

при одновременном повышении надежности.

Для этого в делителе частоты следования импульсов, содержащем триггеры, инверсный выход младшего разряда каждого из которых соединен со счетным входом триггера последующего разряда, и дополнякнций триггер,счетный вход которого соединен со счетным входом триггера млгщшего разряда и с тактовым входом устройства, дополняющий триггер выполнен на 0 триггере, О вход которого соединен с прямым выходом триггера младшего разряда, а входы установки единицы этих триггеров соединены соответственно с инверсным выходом триггером старшего разряда и прямым выходом 0 триггера.

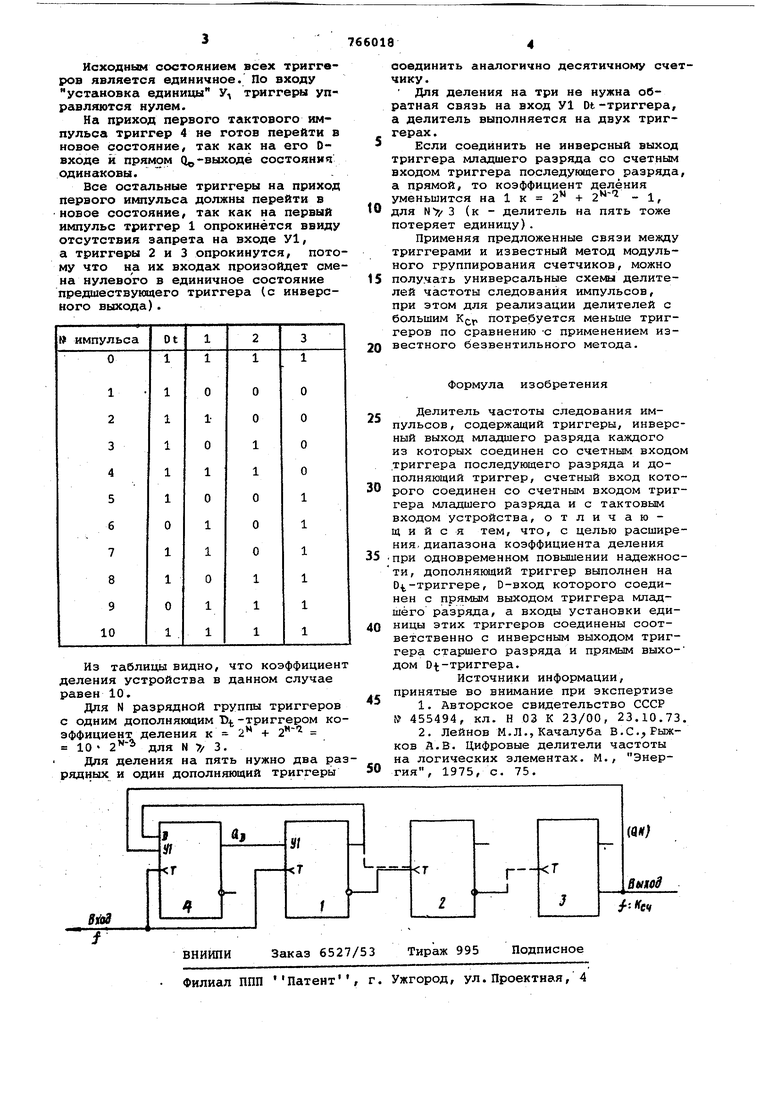

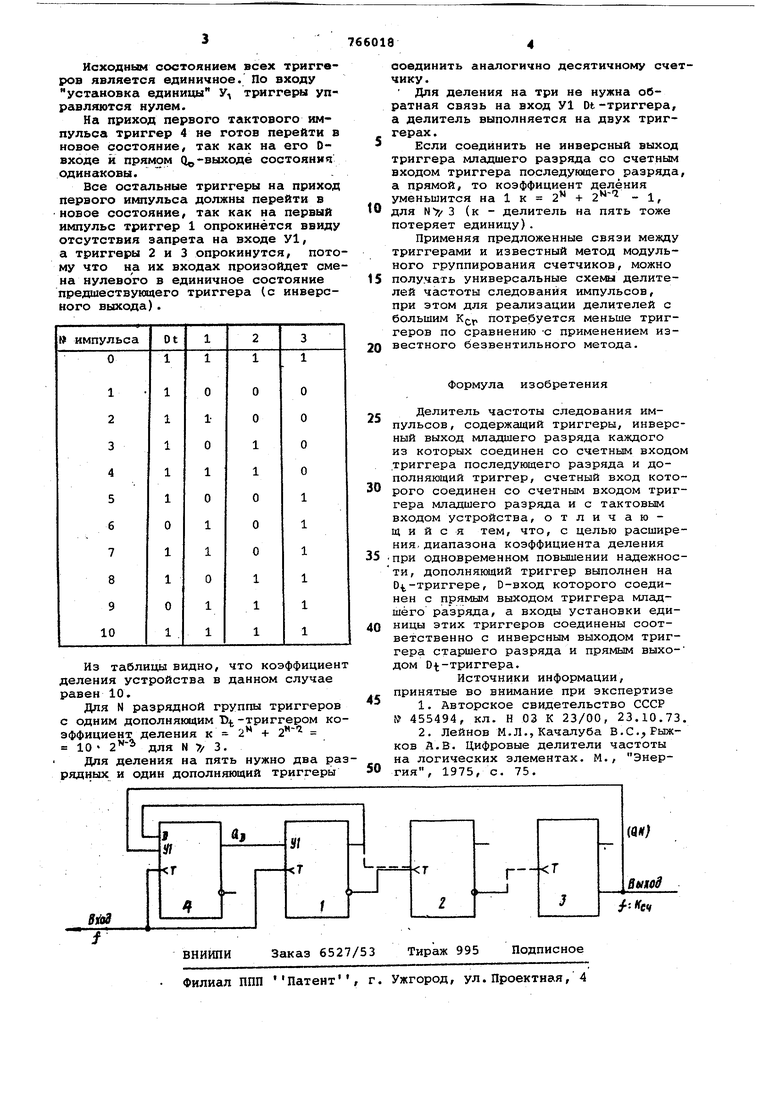

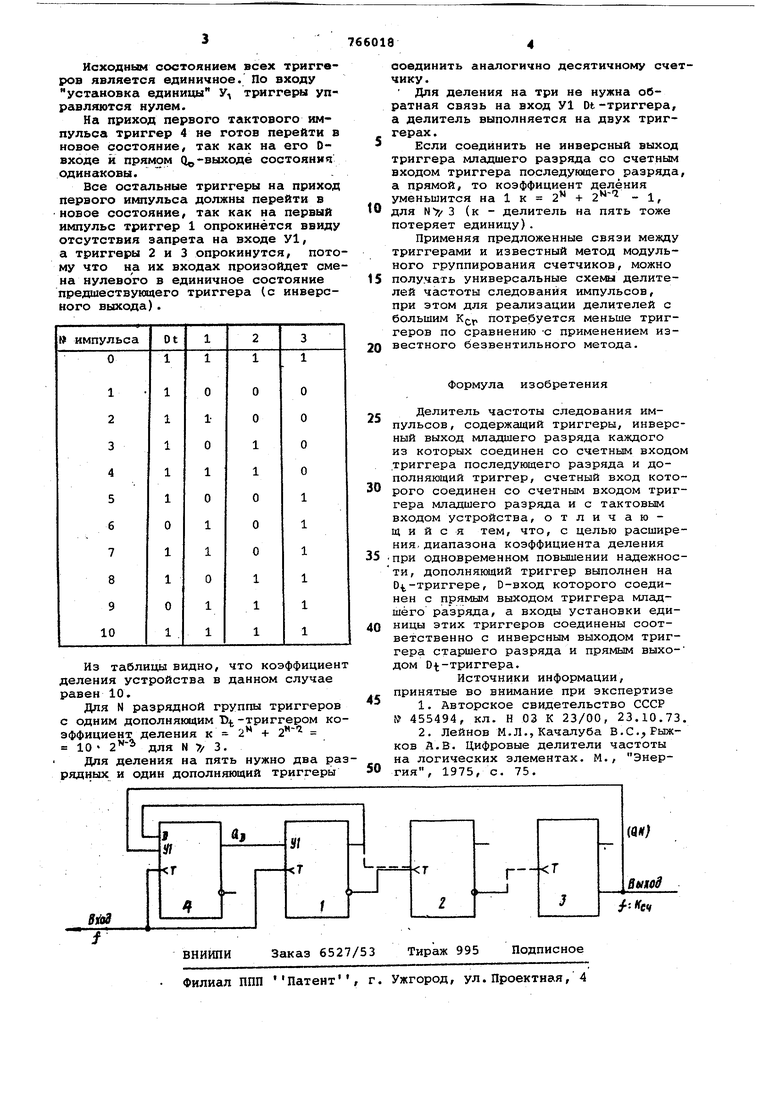

На чертеже изображена структурная электрическая схема делителя частоты следования импульсов.

Он содержит триггеры 1, 2 и 3 первого (младшего), второго, третьего (№ ) разряда, триггер 4 дополняющий ,

Работу устройства рассмотрим на примере делителя частоты следования импульсов, содержащего три разрядных и один дополняющий триггер.

Исходньо4 состоянием всех триггеров является единичное. По входу установка единицы У, триггеры управляются нулем.

На приход первого тактового импульса триггер 4 не готов перейти в новое состояние, так как на его Dвходе к прямом Q -выходе состояния одинаковы.

Все остальные триггеры на приход первого импульса должны перейти в новое состояние, так как на первый импульс триггер 1 опрокинется ввиду отсутствия запрета на входе У1, а триггеры 2 и 3 опрокинутся, потому что на их входах произойдет смена нулевого в единичное состояние предшествукяцего триггера (с инверсного выхода).

Из таблицы видно, что коэффициент деления устройства в данном случае равен 10.

Для N разрядной группы триггеров с одним дополняющим -триггером коэффициент деления к 2 + 2 10 для N / 3.

Для деления на пять нужно два разрядных и один дополняющий триггеры

соединить аналогично десятичному счечику.

Для деления на три не нужна обратная связь на вход У1 Dt-триггера, а делитель выполняется на двух триггерах .

Если соединить не инверсный выход триггера младшего разряда со счетным входом триггера последующего разряда а прямой, то коэффициент деления уменьшится на 1 к 2 + - 1, для 3 (к - делитель на пять тоже потеряет единицу).

Применяя предложенные связи между триггерами и известный метод модульного группирования счетчиков, можно получать универсальные схемы делителей частоты следования импульсов, при этом для реализации делителей с большим К(;р потребуется меньше триггеров по сравнению с применением известного безвентильного метода.

Формула изобретения

Делитель частоты следования импульсов , содержащий триггеры, инверсный выход младшего разряда каждого из которых соединен со счетным входом триггера последующего разряда и дополняющий триггер, счетный вход которого соединен со счетным входом триггера младшего разряда и с тактовым входом устройства, отличающийся тем, что, с целью расширения, диапазона коэффициента деления при одновременном повышении надежности, дополняющий триггер выполнен на 0 -триггере, D-вход которого соединен с прямым выходом триггера младшего разряда, а входы установки единицы этих триггеров соединены соответственно с инверсным выходом триггера старшего разряда и прямым выходом D-t-триггера.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР

455494, кл. Н 03 К 23/00, 23.10.73.

2.Лейнов М.Л., Качалуба В.С.Рыжков и.В. Цифровые делители частоты на логических элементах. М., Энергия , 1975, с. 75.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| Делитель частоты с переменным коэффициентом деления | 1980 |

|

SU921097A1 |

| Устройство для коррекции шкалы времени | 1985 |

|

SU1247828A2 |

| Делитель частоты следования импульсов | 1982 |

|

SU1045400A1 |

| Устройство для определения медианы случайного процесса | 1986 |

|

SU1352502A2 |

| Умножитель частоты следования периодических импульсов | 1980 |

|

SU980094A1 |

| Умножитель частоты | 1983 |

|

SU1151959A1 |

| Управляемый делитель частоты следования импульсов | 1987 |

|

SU1478323A1 |

| Быстродействующий управляемый делитель частоты | 1989 |

|

SU1707762A1 |

| Переключатель ламп иллюминации | 1990 |

|

SU1817265A1 |

Авторы

Даты

1980-09-23—Публикация

1978-10-06—Подача