1

Изобретение относится к области контрольно-измерительной техники и может быть использовано при создании устройство для контроля различных траметров логических схем.

Известно устройство для контроля амплитудно-временных,, параметров логических сигналов, содержащее бпок управления, формирователь, источник опорного напряжения, генератор стробирующих сигналов и элемент сравнения 1 . Недостатком этого устройства являются низкое быстродействие и ограниченные функциональные возможности.

Наиболее близким к изобретению по технической сущности является устройство, содержащее блок управления, выходы которого соединены со входньгми зажимами контролируемой схемы, выходные зажимы которой соединены с входами многоканального блока контроля, каждый из каналов которого содержит первый элемент НЕ, вход которого соединен с одним из выходов блока управления, компараторы нуля и единиць, первые входы которых соединень с выходными зажимами контролируемой схемы, а вторые - с соответствующими

входами блока управления, первый элемент И, | входы которого соединены с выходами компараторов нуля и единицы соответственно, а выход - через второй элемент НЕ с одним из входов второго элемента И и третий элемент НЕ, выход которого соединен с одним из входов третьего элемента И, другой вход которого соединен с выходом основного триггера, первый вход которого соединен с выходом блока управления 121.

10

Недостатком этого устройства является невысокая точность а, следовательно, и качество контроля.

Целью изобретения является повышение качества контроля.

15

Для этого в известном многоканальном устройстве для контроля логических схем, содержащем блок управления, выходы которого соединены со входными зажимами конт20ролируемой схемы, выходные зажимы которой соединены с входами многоканального блока контроля, каждый из каналов которого сойержкт первый элемент НЕ, вход которого соединен с

одним из выходов блока управления, комгарагоры нуля и единицы, первые входы которых соединены с вы-ходными зажимами контролируемой схемы, а вторые - с соответствующими выходами блока управления, первый элемент И, входгл которого соединены с выходами компараторов нуля и единицы соответственно, а выход - через воторой элемент НЕ, с одним из входов второго элемента И, и третий элемент НЕ, выход которого соединен с одним из входов третьего элемента И, другой вход которого соединен с выходом основного триггера, первый вход которого соединен с выходом блока управления, в каждь Й канал многоканального блока контроля введены элемент 2И-ИЛИ и три дополнительных триггера, первые входы которых соединены с выходами соответствующих элементов И, вторые - с срответствуюашм выходом блока управления, вход которого соединен с выхода ади дополнительных триггеров, при этом входы элемета 2И-ИЛИ соединены с выходами соответственно компараторов нуля и е;дашщы, первого элемента НЕ и блока управлегшя, а выход - с входами соответственно третьего элем та НЕ и вторым входом основного триггера.

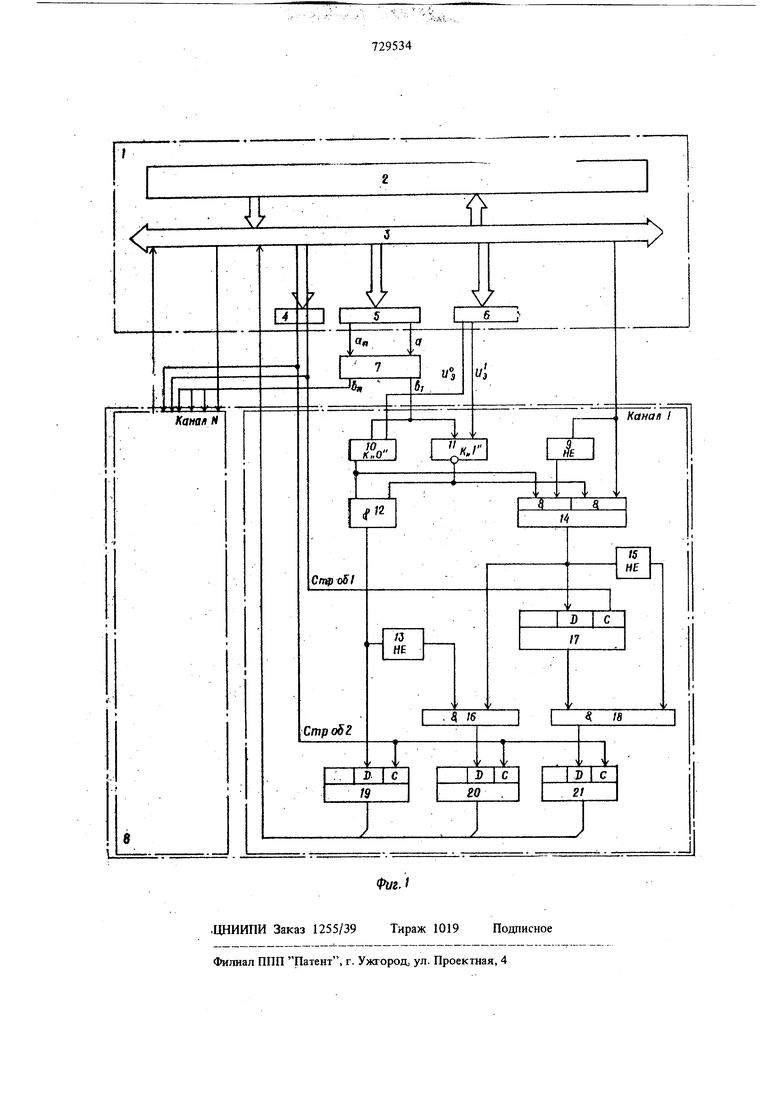

На чертеже представлена функциональная схема устройства.

Устройство содержит- блок управлешш 1, включающий УВМ 2, магистраль 3, программируемый генератор 4, блок входных воздействий 5 и блок эталонных уровней 6, контролируемую схему 7 и многоканальный блок контроля 8, каждый из каналов которого В1слючает первый элемент НЕ 9, компаратор нуля 10, компаратор единицы 11, первый элемент И 12, второй элемент НЕ 13, элемент 2И-ИЛИ .14, третий элемент НЕ 15, второй элемент И 16, основной триггер 17, третий элемент И 18 и три дополтштельных триггера 19, 20 и 21 (соответствеиго уровень, функционирование и задержка распространения).

Устройство работает следующим образом. .

Сигналы для контроля логической схемы с блока 5 входных воздействий подаются на входы а,... ап кош-ролируемой схемы 7. УВМ 2 управляет .работой блока 5 входных воздействий через магистраль 3, Исследуемые логические сигналы с выходов контролируемой схемы 7 подаются на первые входы комшраторов 10, 11 нуля и единицы соответствующих каналов. На вторые входы компараторов 10, 11 с блока 6 этэлогшых уровней подаются эталонньге уровни опорного напряжения (Из и Ид ), в пределах которых кОнтролируется выходной логический сигнал.

. УВМ 2 ;управяяет работой блока 6 эталонных уровней через магистраль 3. В зависимости от ожидаемого сигнала на выходе контролируемой схемы 7 УВМ 2 вырабатывает сигнал эталонной реакции (ЭР), который через магистраль 3 подается на входы элементов 9 и 14 соответствующих каналов. Контроль выходных сигналов осуптествляется при помощи двух стробирующих сигналов строб I и строб 2, вьтрабатываемых программируемым генератором 4 Временное расположение стробируюнпос импульсов в контрольном такте Т определяется программой с помощью -УВМ 2 через магистраль 3. Строб 1 предназначен для контроля задержки распространения логических сигналов (сз,р.).. поэтому его временное расположение определяется ожидаемой задержкой распространения. Строб 2 располагается всегда в конце контрольного такта.

Контроль выходного логического сигнала начинается с того, что после подачи сигналов с блока 5 входных воздействий на входы а... ... а,), задания зталоншлх уровней Иэ и Иэ на компараторах 10, И нуля и единицы блоком 6 эталонных уровней, задания соответствующих параметров сигналов строб I и строб 2 генератору 4 и выработки соответствуютцего сигнала эталонной реакции УВМ 2, на контролируемую схему 7 подается синхроимпульс, который осутцествляет передачу входных воздействий совходных шин ш контролируемую схему 7, на выходах в ...в которой через время задержки г э.р. появится логический сигнал.

Возможны шесть вариаетов изменения состояния логических сигналов на выходе контролируемой схемы.

Вариант 1. Изменение состояния логического сигнала не произошло.

Вариант 2. Изменение состояния логического сигнала до промежуточного значения про-. изощло за время . з.р.) но новое эталонное значение не достигнуто.

Вариант 3. Изменение состояния логического сигнала до промежуточного знaчeшfя произошло за время . з.р. ио новое эталонное значение не достигнуто.

Вариант 4. Изменение состояния логического сигнала до промежуточного значения произошло за время сз.р.. Новое эталонное значение сигнала получено за время ..р.

Вариант 5. Изменение состояния логического сигнала до промеж точного значения произошло за время tjj3M . Новое эталонное значение сигнала получено за время t 1щ j.p.

Вариант ё. Изменение состояния логического сигнала до промежуточного значения тфоизошло за время t .p. Новоеэталонное значение сигнала полугено за время зм.г.. Перешсленные изменения состояния логических сигналов можно классифицировать, как а).вариант 1 - брак, функционирования, так как контролируемая схема вообще не реагировалана входное воздействие; б)вариант 2 и 3 - брак по уровню, так как изменение состояния логического сигнала произошло, но сигнал на выходе контролируемой схемы не достиг нового эталонного значения; в)вариант 4 и 5 - брак по задержке распространения сигнала, так как новое эталонное значение выходного сигнала получено за время больше ожидаемого; г)вариант б показывает, как должен изменяться выходной логический сигнал, удовлетворяющий заданным условиям (случай годной схемы). Рассмотрим вариант изг енения состояния логического сигнала из 1 в 0. В момент времени tj на выходе компаратора 10 нуля - I, на выходе компаратора И единиц -- О, на выходе , элемента 2И-ИЛИ 14 I. Логическая единица с выхода элемента 2И-ИЛИ 14 сигналом строб Г заносится в триггер 17. В момент времени tj выходные сигналы компараторов 10, 11 нуля и единицы не изменяется, поэтому на выходе элемента И 12 0.,Этот сигнал, пройдя элемент НЕ 13, в виде будет подан на первый вход элемента И 16, на втором входе которого имеется также сигнал I с выхода элемента 2И-ИЛИ 14, поэтому на выходе элемента И 16 - также сигнал Г.. Епн ничный сигнал с выхода элемента 2И-ИЛИ 14, пройдя элемент НЕ 15, установит на выходе элемента И 18 сигнал 0. Вследствие этого сигн строб 2 установит: триггер 19 уровень в нулевое состояние, триггер 20 функционирование - в еди шчное, триггер 21 .задержка распространения - в нулевое. Установление триггера 20 функционирование в единичное состо яние сигнализирует о том., что. контролнруема схема бракуется но функционированию. Единичное состояние триггера 20 функцио нирование через магистраль 3 воспринимается УВМ 2 как сигнал прерывания. Рабочая гфог76 рамма прерывается и УВМ 2 переключается а программу, oбcJryж шaющyю прерывание. Работа устройства в ocтaль гыx случаях прослеживается аналогична.; Формула изобретения Многокана.гП)Ное устройство для контроля логижских схем, содержащее блок управления, выходы которого соединены со входными зажимами контролируемой схемы, выходные зажимы которой соединены с входами многоканального блока контро.г1я, каждый из каналов которого содержит первый элемент НЕ, вход которого соединен с одним из выходов блока управления, компараторы нуля и единицы, первые входы которых соединены с выходными зажимами контролируемой схемы, а вторые - с соответствующими выходами блока управления, первый элемент И, входы которого соединены с выходами комшраторов нуля и единицы соответственно, а выход - через второй элемент НЕ с одним из выходов второго эпемеггга И и третий элемент НЕ, выход которого соединен с одним из входов третьего элемента И, другой вход которого соединен с выходом основного триггера, гкрвый вход которого соединен с выходом блока управления, отлнчаюшее- с я тем, что, с целью повышения качества контроля, в каждый канал многоканального блока контроля введены элемент 2И-ИЛИ и три дополнительных триггера, первые входы которых соединены с выходами соответствующих элементов И, вторые - с соответствующим выходом блока управления, вход которюго соединен с выходами дополнительных триггеров, при этом входь элемента 2И-ИЛИ соединены с выходами соответственно компараторов нуля и единицы, первого элемента НЕ и блока управления, а выход - с входами соответственно гретьего элемента НЕ и вторым входом основного триггера. Источники информации, принятые во внимание при экспертизе 1.Авторское сввдетельство СССР № 411399, кл. G 01 R 31/28, 197.8 (аналог.). 2.Патент Великобритании 1.282.228, кл. G 01 R 31/28, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля больших интегральных схем | 1983 |

|

SU1193608A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Устройство для функционального контроля больших интегральных схем | 1990 |

|

SU1809398A1 |

| Устройство для контроля правильности электрического монтажа | 1984 |

|

SU1216782A1 |

| Устройство для контроля субблока логического блока | 1986 |

|

SU1327111A1 |

| Устройство для контроля больших интегральных схем | 1986 |

|

SU1348835A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для функционального контроля цифровых интегральных схем | 1986 |

|

SU1337838A1 |

| Устройство для компенсации реактивной мощности | 1990 |

|

SU1746463A1 |

| Многоканальное устройство тестового контроля логических узлов | 1982 |

|

SU1049839A1 |

Авторы

Даты

1980-04-25—Публикация

1977-08-05—Подача