1

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах контроля больших интегральных схем (БИС).

Целью изобретения является повышение достоверности контроля за счет создания новых вариантов комбинаций тестов.

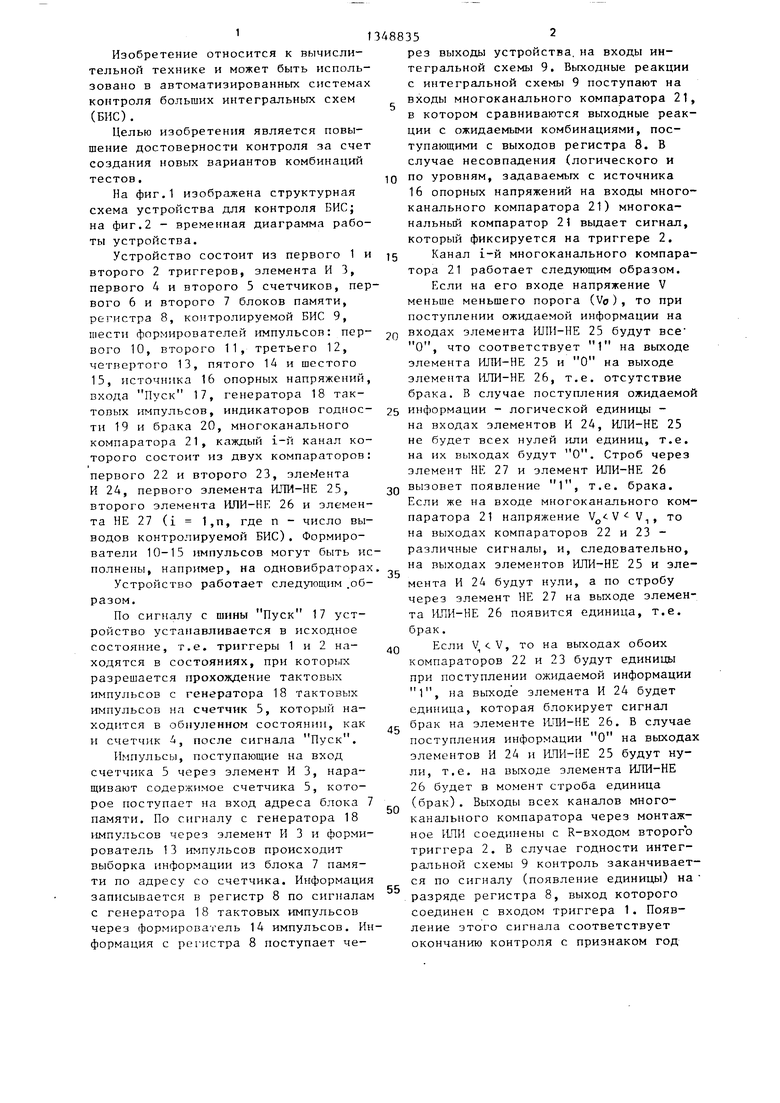

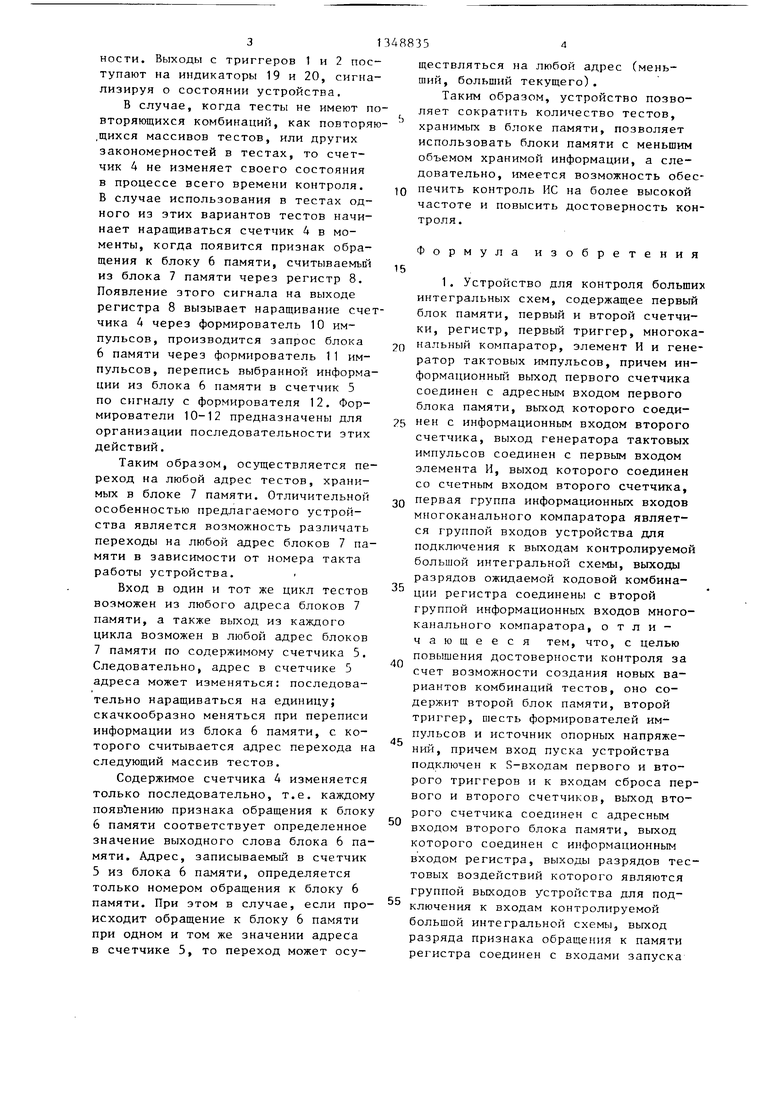

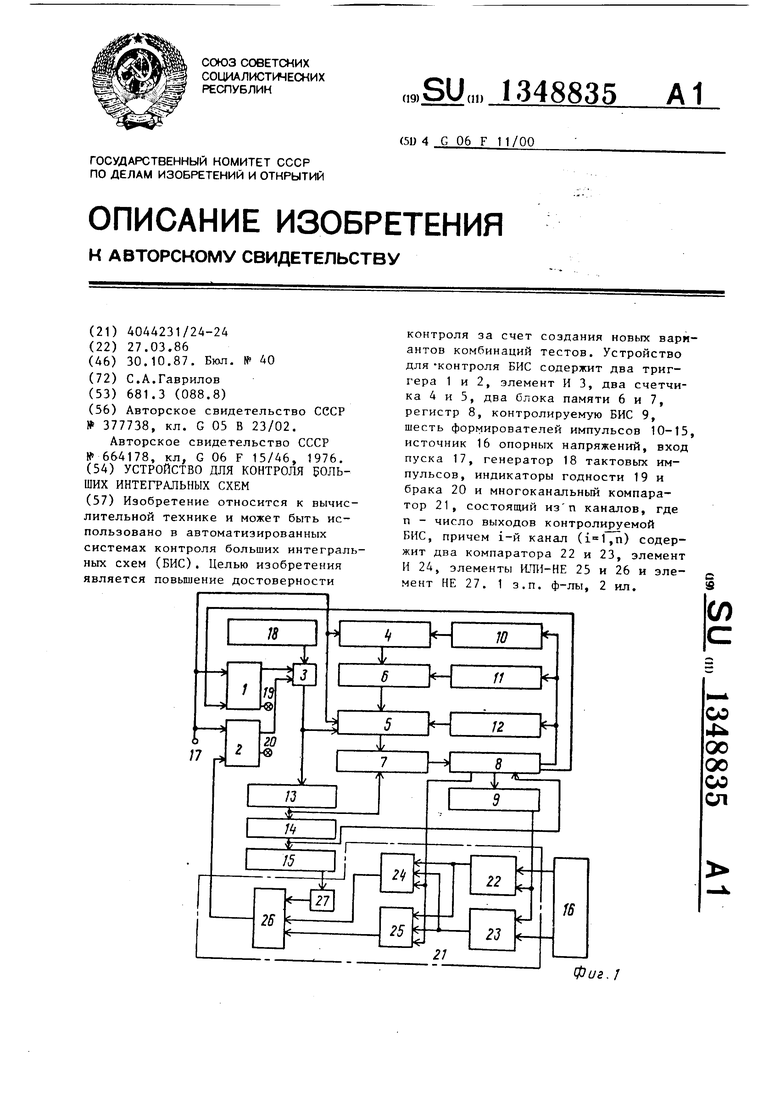

На фиг.1 изображена структурная схема устройства для контроля БИС; на фиг.2 - временная диаграмма работы устройства.

Устройство состоит из первого 1 и второго 2 триггеров, элемента И 3, первого 4 и второго 5 счетчиков, пер вого 6 и второго 7 блоков памяти, регистра 8, контролируемой БИС 9, шести формирователей импульсов: первого 10, второго 11, третьего 12, четвертого 13, пятого 1Д и шестого 15, источн 1ка 16 опорных напряжений, входа Пуск 17, генератора 18 тактовых импульсов, индикаторов годности 19 и брака 20, многоканального компаратора 21, каждый i-й канал которого состоит из двух компараторов: первого 22 и второго 23, И 24, первого элемента ИЛИ-НЕ 25, второго элемента ИЛИ-НЕ 26 и элемента НЕ 27 (1 1,п, где п - число выводов контролируемой БИС). Формирователи 10-15 импульсов могут быть ис полнены, например, на одновибраторах

Устройство работает следующим .образом.

По сигналу с шины Пуск 17 устройство устанавливается в исходное состояние, т.е. триггеры 1 и 2 находятся в состояниях, при которых разрешается прохождение тактовых импульсов с генератора 18 тактовых импульсов на счетчик 5, который находится в обнуленном состоянии, как и счетчик 4, после сигнала Пуск.

Импульсы, поступающие на вход счетчика 5 через элемент И 3, наращивают содержимое счетчика 5, которое поступает на вход адреса блока 7 памяти. По сигналу с генератора 18 импульсов через элемент И 3 и формирователь 13 импульсов происходит выборка информации из блока 7 памяти по адресу со счетчика. Информация записывается в регистр 8 по сигналам с генератора 18 тактовых импульсов через формирователь 14 импульсов. Информация с регистра 8 поступает че488352

рез выходы устройства, на входы интегральной схемы 9. Выходные реакции с интегральной схемы 9 поступают на входы многоканального компаратора 21, в котором сравниваются выходные реакции с ожидаемыми комбинациями, поступающими с выходов регистра 8. В случае несовпадения (логического и

10 по уровням, задаваемых с источника 16 опорных напряжений на входы многоканального компаратора 21) многоканальный компаратор 21 выдает сигнал, который фиксируется на триггере 2.

15 Канал i-й многоканального компаратора 21 работает следующим образом.

Если на его входе напряжение V меньше меньшего порога (Vo), то при поступлении ожидаемой информации на

2Q входах элемента ИЛИ-НЕ 25 будут все О, что соответствует 1 на выходе элемента ИЛИ-НЕ 25 и О на выходе элемента ЦГТИ-НЕ 26, т.е. отсутствие брака. В случае поступления ожидаемой

25 информации - логической единицы - на входах элементов И 24, ИЛИ-НЕ 25 не будет всех нулей или единиц, т.е. на их выходах будут О. Строб через элемент НЕ 27 и элемент ИЛИ-НЕ 26

20 вызовет появление 1, т.е. брака. Если же на входе многоканального компаратора 21 напряжение ,, то на выходах компараторов 22 и 23 - различные сигналы, и, следовательно, на выходах элементов ИЛИ-НЕ 25 и элемента И 24 будут нули, а по стробу через элемент НЕ 27 на выходе элемента ИЛИ-НЕ 26 появится единица, т.е. брак.

0 Если , то на выходах обоих компараторов 22 и 23 будут единицы при поступлении ожидаемой информации 1, на выходе элемента И 24 будет единица, которая блокирует сигнал

35

брак на элементе ПИ-НЕ 26. В случае поступления информации О на выходах элементов И 24 и 11ПИ-НЕ 25 будут нули, т.е. на выходе элемента ИЛИ-НЕ 26 будет в момент строба единица (брак). Выходы всех каналов многоканального компаратора через монтажное РШИ соединены с R-входом второго триггера 2. В случае годности интегральной схемы 9 контроль заканчивается по сигналу (появление единицы) на разряде регистра 8, выход которого соединен с входом триггера 1. Появление этого сигнала соответствует окончанию контроля с признаком год

3

ности. Выходы с триггеров 1 и 2 поступают на индикаторы 19 и 20, сигнализируя о состоянии устройства.

В случае, когда тесты не имеют повторяющихся комбинаций, как повторяю ,щихся массивов тестов, или других закономерностей в тестах, то счетчик А не изменяет своего состояния в процессе всего времени контроля. В случае использования в тестах одного из этих вариантов тестов начинает наращиваться счетчик 4 в моменты, когда появится признак обращения к блоку 6 памяти, считываемъпИ из блока 7 памяти через регистр 8. Появление этого сигнала на выходе регистра 8 вызывает наращивание счетчика А через формирователь 10 импульсов, производится запрос блока

6памяти через формирователь 11 импульсов, перепись выбранной информации из блока 6 памяти в счетчик 5

по сигналу с формирователя 12. Формирователи 10-12 предназначены для организации последовательности этих действий.

Таким образом, осуществляется переход на любой адрес тестов, хранимых в блоке 7 памяти. Отличительной особенностью предлагаемого устройства является возможность различать переходы на любой адрес блоков 7 памяти в зависимости от номера такта работы устройства.

Вход в один и тот же цикл тестов возможен из любого адреса блоков 7 памяти, а также выход из каждого цикла возможен в любой адрес блоков

7памяти по содержимому счетчика 5. Следовательно, адрес в счетчике 5 адреса может изменяться: последовательно наращиваться на единицу; скачкообразно меняться при переписи информации из блока 6 памяти, с которого считывается адрес перехода н следующий массив тестов.

Содержимое счетчика 4 изменяется только последовательно, т.е. каждом появ тению признака обращения к блок 6 памяти соответствует определенное значение выходного слова блока 6 памяти. Адрес, записываемьи в счетчик 5 из блока 6 памяти, определяется только номером обращения к блоку 6 памяти. При этом в случае, если происходит обращение к блоку 6 памяти при одном и том же значении адреса в счетчике 5, то переход может осу488354

ществляться на любой адрес (меньший, больший текущего).

Таким образом, устройство позволяет сократить количество тестов, хранимых в блоке памяти, позволяет использовать блоки памяти с меньшим объемом хранимой информации, а следовательно, имеется возможность обеспечить контроль ИС на более высокой частоте и повысить достоверность контроля.

Ь

10

5

0

5

0

5

0

5

0

5

Формула изобретения

1. Устройство для контроля больших интегральных схем, содержащее первый блок памяти, первый и второй счетчики, регистр, первьй триггер, многоканальный компаратор, элемент И и генератор тактовых импульсов, причем ин- формационньш выход первого счетчика соединен с адресным входом первого блока памяти, выход которого соединен с информационным входом второго счетчика, выход генератора тактовых импульсов соединен с первым входом элемента И, выход которого соединен со счетным входом второго счетчика, первая группа информационных входов многоканального компаратора является группой входов устройства для подключения к выходам контролируемой большой интегральной схемы, выходы разрядов ожидаемой кодовой комбинации регистра соединены с второй группой информационных входов многоканального компаратора, отличающееся тем, что, с целью повышения достоверности контроля за счет возможности создания новых вариантов комбинаций тестов, оно содержит второй блок памяти, второй триггер, шесть формирователей импульсов и источник опорных напряжений, причем вход пуска устройства подключен к S-входам первого и второго триггеров и к входам сброса первого и второго счетчиков, выход второго счетчика соединен с адресным входом второго блока памяти, выход которого соединен с информационным входом регистра, выходы разрядов тестовых воздействий которого являются группой выходов устройства для подключения к входам контролируемой большой интегральной схемы, выход разряда признака обращения к памяти регистра соединен с входами запуска

первого, второго и третьего формирователей импульсов, выходы которых соединены соответственно со счетным входом первого счетчика, входом чтения первого блока памяти и входом записи второго счетчика, выход разряда признака конца контроля регистра соединен с R-входом первого триггера, прямой выход которого соединен с вторым входом элемента И, третий вход которого соединен с прямым выходом второго триггера, инверсные вы ходы первого и второго триггеров являются соответственно выходами годности и брака устройства, выход многоканального компаратора соединен с R-входом второго триггера, выход эле мента И соединен с входом запуска четвертого формирователя импульсов, выход которого соединен с входом запуска пятого формирователя импульсов и входом чтения второго блока памяти, выход пятого формирователя импульсов соединен с входами записи регистра и шестого формирователя импульсов, выход которого соединен с входом синхронизации многоканального компаратора, первый и второй входы опорного напряжения которого соединены с выходами соответственно верхнего и нижнего порогов источника опорных напряжений.

2. Устройство по П.1, отличающееся тем, что многоканальный компаратор содержит п канаД8835°

лов, где п - число выходов контролируемой большой интегральной схемы, причем каждый i-й канал многоканального компаратора (i 1,п) содержит первый и второй компараторы, элемент И, элемент НЕ, первый и второй элементы ИЛИ-НЕ, причем i-й вход первой группы информационны){ входов много10 канального компаратора подключен к первым информационным входам первого и второго компараторов, второй ин- формационньш вход первого компаратора подключен к первому входу опорного

15 напряжения многоканального компаратора, второй информационный вход второго компаратора подключен к второму входу опорного напряжения многоканального компаратора, выход первого

2Q компаратора соединен с первыми вхо-- дами элемента И и первого элемента ИЛИ-НЕ, выход второго компаратора соединен с вторыми входами элемента И и первого элемента ИЛИ-НЕ, третьи

25 входы элемента И и первого элемента ИЛИ-НЕ подключены к i-му входу второй группы информационных входов многоканального компаратора, выходы элемента И и первого элемента ИЛИ-НЕ

3Q соединены соответственно с первым и вторым входами второго элемента ИПИ-НЕ, третий вход которого через элемент НЕ подключен к входу синхронизации многоканального компаратора, выход второго элемента ИЛИ-НЕ подключен к выходу многоканального компаратора.

35

Редактор Н.Слободяник

Составитель Д.Ванюхин Техред А.Кравчук

Заказ 4803/49Тираж 670Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

в-.в«---- -

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор В.Бутяга

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля интегральных схем | 1983 |

|

SU1171795A1 |

| Устройство контроля интегральных схем | 1986 |

|

SU1370634A1 |

| Устройство контроля интегральных схем | 1987 |

|

SU1479899A1 |

| Устройство контроля интегральных схем | 1987 |

|

SU1430914A1 |

| Устройство для контроля цифровых объектов | 1983 |

|

SU1160373A1 |

| Устройство контроля интегральных схем | 1982 |

|

SU1049838A1 |

| Устройство для контроля интегральных схем | 1978 |

|

SU744579A1 |

| Система для автоматического контроля больших интегральных схем | 1976 |

|

SU664178A1 |

| Устройство для контроля контатирования интегральных схем | 1982 |

|

SU1049912A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1608697A1 |

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах контроля больших интегральных схем (БИС). Целью изобретения является повышение достоверности контроля за счет создания новых вариантов комбинаций тестов. Устройство для -контроля БИС содержит два триггера 1 и 2, элемент И 3, два счетчика 4 и 5, два блока памяти 6 и 7, регистр 8, контролируемую БИС 9, шесть формирователей импульсов 10-15, источник 16 опорных напряжений, вход пуска 17, генератор 18 тактовых импульсов, индикаторы годности 19 и брака 20 и многоканальный компаратор 21, состоящий из п каналов, где п - число выходов контролируемой БИС, причем i-й канал (,n) содержит два компаратора 22 и 23, элемент И 24, элементы ИЛИ-НЕ 25 и 26 и элемент НЕ 27. 1 з.п. ф-лы, 2 ил. S оо N( 00 00 со ел Фиг.

| ОПИСАНИЕ ИЗОБРЕТЕНИЯ | 0 |

|

SU377738A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Система для автоматического контроля больших интегральных схем | 1976 |

|

SU664178A1 |

Авторы

Даты

1987-10-30—Публикация

1986-03-27—Подача