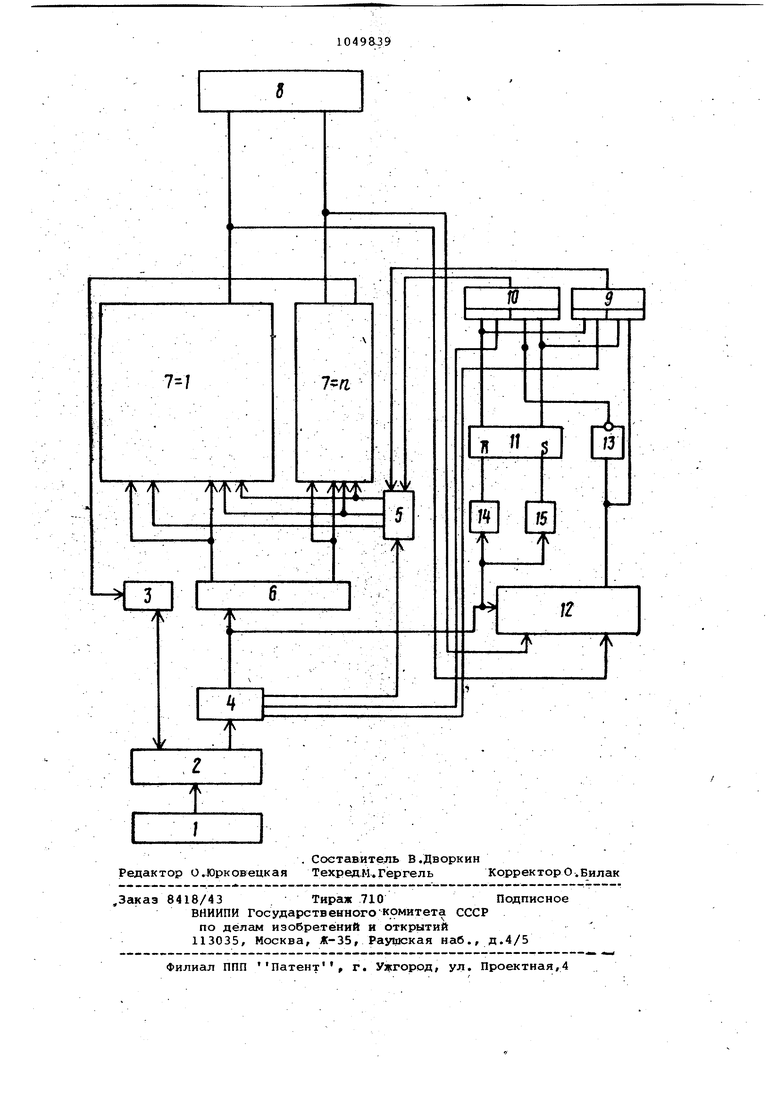

Изобретение относится к контроль но-иэмерительной технике и может быть использовано для контроля логи ческих узлов ЦВМ. Известно устройство для контроля логических микросхем, содержащее блок памяти, блок управления, генератор стимулирующих воздействий, коммутатор, блок сравнения, блок памяти неисправностей, блок формиро вания сигнала ошибки, регистр подпрограмм, регистр сбоев, регистр цикла,регистр возврата, адресный ко мутатор, регистр масок,блок хранения масок, блок формирования масок l . Недостатком устройства, являются низкая достоверность контроля и огр ниченные функциональные возможности обусловленные тем, что оно не обеспечивает маскирование (блокировку) сравнения эталонных и полученных реакций по отдельным заданным выхо дам контролируемой логической микро схемы, на каждом из слов контролирукхцего теста, осуществляет лишь пословную блокировку сравнения на всех выходах микросхемы, что снижает достоверность контроля из-за полног отсутствия контроля микросхемы на значительном количестве слов теста по некоторым их выходам. Наиболее близким к изобретению является многоканальное устройство тестового контроля логичесасих узлов содержащее блок памяти, соединенный выходом с входом коммутатора, соединенного первым выходом с первым входом блока управления, вторым выходом - с входом блока приема и накопления информации,соединенного первым выходом с первым входом формирователя сигналов,.вторым выходом - с входом дешифратора адреса, выходы которого соединены с соответствуклй,ими первыми входами блоков контроля, соединенных вторыми, третьими и четвертыми входами соответственно с первым, вторым и третьим выходами формирователя сигналов,первыми выхо дами -с вторым входом блока управления, вторыми выходами - с соответствующими клеммами для подключения входов контролируемого логического узла 2 . Недостатком известного устройства является 6граниченная область .применения, что обусловлено отсутствием возможности маскирования (блокировки) сравнения эталонных и полученных реакций по -отдельным и различным на каждом слове теста выходам контро лируемой микросхемы. Отсутствие маежирования приводит к невозможности контроля широкого класса микросхем, состояния которых на отдельных и разных выходах не определены в различных словах теста. Цель изобретения - расширение области применения устройства. Поставленная цель достигается тем, что в многоканальное устройство тестового контроля логических узлов, , содержащее блок памяти, соединенный выходом с входом коммутатора, соединенного первым выходом с первым входом блока управления, вторым выходом - с входом блока приема и накопления информации, соединенного первым выходом с первым входом формирователя сигналов, вторым выходомс входом дешифратора адреса, выходы которого соединены с соответствующи.ми первыми входами блоков контроля, соединенных вторыми, третьими и четвертыми входами соответственно с первым, вторым и третьим выходами формирователя сигналов, первыми выходами - с вторым входсм блока управления, вторыми выходами - с сот ответствующими клеммами для подключения контактов контролируемого логического узла, введены мультиплексор, первый дешифратор признака, второй дешифратор признака, триггер, элемент , НЕ, первый элемент 2И-ИЛИ, второй элемент 2И-ИЛИ, соединенный выходом с вторым входом формирователя сигналов, третий вход которого соед инен с выходом первого элемента 2ИИЛИ, соединенного первым входом с. первым входом второго элемента 2И- ИЛИ и с первым выходом триггера,со диненного вторым выходом с вторым входом первого элемента 2И-ИЛИ и с вторым второго элемента 2ИИЛИ, третий вход первого элемента 2И-ИЛИ соединен с выходом мультиплексхэра и с входом элемента НЕ, соединенного выходом с третьим входом второго элемента 2И-ИЛИ, четвертый вход которого соединен с третьим выходом блока приема и н.акоплени информации, четвертый выход которого соединен с вторым входом первого элемента 2И-ИЛИ,R -вход триггера соедаи- , нен с выходом первого дешифратора признака,выход которого соединен с вторым выходом блока приема и накопления информации,с первым входом мультиплексора,с входом второго дешифратора признака,выход которого соединен с S- входом триггера,вторые входы мультиплексора соединены с клеммами для подключения контролируемого логического узла На чертеже приведена блок-схема : устройства., Многоканальное устройство контроля логических узлов содержит блок 1 памяти,соединенный выходом с входом коммутатора 2, соединенного первым выходом с входом блока 3.-управления, вторым выходом - с входом блока 4 приема и накопления информации,, сое- диненного первым выходом с первьал входом фор1 ирователя 5 сигналов, вторым выходом - с входом дешифратор ра 6 адреса, выходы которого соеди-;йены с соответствующими первыми входами блоков 7-1 - 7- ц контроля, соединенньвс вторыми, третьими и четвертыми входами соответственно с первым, вторым и третьим выходами формирователя 5 сигналов, первыми выходами - с вторь входом блока 3 управления, вторьми входами -с соответствующими клеммами для подключения контактов коятррлируемого логического узла 8. Выход первого элаие та 9 2И-ИЛИ соединен с третьим входом формирователя 5 сигналов второй Ёход которого соединен с выходом- вто рого элемента 10 2И-ИЛИ, соединенного первом-входом с первьм входс 1 первого элемента 9 2И-ИЛИ и с первы выходом триггера 11, соединенного вторьм выходом с вторым, входом первого элемента 9 2И-ИЛИ и вторым входом второго элемента 10 2И-ИЛИ, тре тий вход первого элемента 9 2И-ИЛИ соединен с выходом мультиплексора 1 и входом элемента 13 ЯЕ соединенно го выходом с третьим входом второго элемента 10 2И-ИЛИ, четвертый вход которого соединен с третьим выходом блока 4 приела и накопления информа ции, четвертый выход которого соеди нен с четвертым входом первого элемента 9 2И-ИЛИ, R -вход триггера 11 соединен с выходом первого д01гаф ратора 14 признака, вход .которого соединен с вторым выходом блока 4 приема и накопления инфорвмацйи, с первым входом мультиплексора 12г с входом второго дешифратора 15 признака, выход которого соединен с 6- входом триггера 11, вторые входы мультиплексора 12 соединены с ми для подключения контролируемого логического узла 8. Устройство работает следующим образом. Количество блоков 7 контроля (Н) соответствует числу контактов контр лируемого логического узла 8. В исходном соотношении (после задания сигнала установки) триггер И находится в состоянии, разрешающем прохождение сигналов с выходов блока 4 приема и накопления информации через элементы 9 и 10 2И-ИЛИ на формирователь 5 сигналов.. В рех:име коммутации с блока 3 уп равления в коммутатор 2 подается на Чсшьный адрес необходимрй програь и сигнал 3aifp6c ni6 начашьнетлу адресу-коммутатор 2 выбирает из Оло ка 1 необходимую программу контроля и кокмутации. В программе записан коммутационный тест, который обеспечивает необходимые соединения контактов узла 8с блоком 7 так, что на входные контакты узла 8 поступают тестов.ые воздействия, а его выходные реакции с выходных контактов сравниваются с эталонными,реакциями блока 7. . Информация,-считанная с блока 1 памяти, через коммутатор 2 поступает на блок 4 приема и накопления информации, который формирует ()разрядное слово, (EorfjH) - разрядов определяют адрес контакта, а остальные три - управляющие сигналы Запись 0, Запись и Опрос. Управляющий сигнал Опрос подается на формирователь 5 сигналов, а адресные сигналы - на дешифратор б адреса. Управляющие сигналы ЗаписьО и Запись 1 поступают на форми.рователь 5 через открытые триггер 11, элементы 10 и 9 2И-Ш1И и пред- . ставляют собой йарафазный код логического сигнала, записываемого в соответствзпощий адресу -j -го контакта блок 7-4 . Если в блок 7- i необходимо запиг сать сигнал О, по двум выходам ЗаписьО и Запись с блока 4 вьздается код 10, если 1 - код 01. В режиме коммутации формирователь 5 -сигналов вьлрабатывает сигнал Ксжмутациипо приходу сигнала письО. . При. принадлежности 1-го контакта логического узла 8 к входу по его адресу, заданному даиифратором б, поступает с формирователя 5 сигнал Коммутация, по которому соответствукхций блок 7-} переходит .в режим выдачи входных-воздействий на -тый контакт узла 8. - . При принадлежности -го контакта узла 8 к выходам Коммутационный тест не действует на блок 7 контроля. Признаком конца коммутационного теста является появление первого по времени сигнала.. Опрос , после которого устройство переходит- в режим контроля., Для контроля узла 8 по j -му слову теста с блока 1 памяти поступают последовательно во времени на дешифратор 6 адреса входных контактов, уотарые должны изменить логический уровень по сравнению с ( J -1) тестовым словом, совместно с сигналом ЗаписьО или Запись., после ввода совокупности адресов этих изменений с информацией пись с блока памяти поступают адреса выходных контактов, состояния которых определены в тесте и которые должны изменить логический уровень : о сравнению с ( j -) тестовым словом. Зат&л с.блока 1 памяти поступает в данном j -том слове теста приэнгис, показывающий, что.вводимые далее адраса хай.актеризу1от выходы логического узла, состояния которых в данном слове теста не определены. Поступающий с блока 1 признак расшифровьшается дешифратором 14, который переключает триггер 11 по 1 -входу в сое тоянИе, разрешающее прохождение сигналов с мультиплексора 12 через элементы 9 и 10 2И-ИЛИ. Триггер 11,переключившись, запрвщаетг-) прохождение сигналов Запись Запись с выходов &Л9 ка 4 на входы формирователя 5, в результате чего запись тестовой ИИфррмации и-з блока 1 в блоки 7 7-П прекрагцается. Одновременно триггер 11 разрешает прохождение информации с выхода логического узла 8, выбранного мультиплексором 12 по адресу, заданному с выхода блока 4 приема и накопления, на вход злаиента 13 ЯЕ и злемента 9 2И-ИЛЙ и далее через элементы 9 и 10 2И-ИЛИ и формирователь 5 сигналов - на входы блоков 7-1 7-.:./- : ,. , . -/ . В результате в блоки 7-1 контроля по каждому -му выходу узла 8,состойние которого не определено, в теств записанном в блоке 1, зар сбшается определенное логическое состогяяие, С:у1аествующее на в ыход;е логннеского узла 8 после задания; на его входы входных воздействий.;Элемент 13: о&еспечийа1ет получение парафазнбго кода|. необзсодимогодля записи нуля или единицы в блок 7- . , В оответствии с тем, -что на один блока 7-i контроля поступает логический сигнал.с выхода -го логи ческого узла 8, а ка другой его вход поступает логическое состояние того же « -го выхода, блок 7 i не задает сигнал Не годен по данному i -му выходу, что и является маск:ированием сравнения по выходам с неопределенными в тесте состояниями логическогр узла 8. По окончании ввода адреса выхо дов, имеющих неопрепеленные состояния, в ланНом слове теста вводится признак, поступающий на вход лешифратора 15 и переключаюоАий триггер 11 в «сходное состояние (разрешающее прохождение информации с блока 4 на форйийроватеяь 5) . После ввода информации в блок 7- 1 по всем вьрсодам логического узла 8 и исходной установки триггер 11 с блока. 1 памяти поступает сигнал Опросна блок 3 управления, где анализируются сортояния выходов блоков , ;Вьщаюи1ИК результат коятро чя по всем i контактам -узла:-.:18, .. ; ; ;, -,;;; .:.; :.-.. : - Сигнал Яе; годен вьщэется в vfoM случ;ае, если хотя бы один из уровней выходных сигналов логического узла В не соответствует уроЕ1Ню эталояньк cHiiniaJiOB задайных на блоки 7-1 - 7 --ii; .: Л ,/:/;. - . . TaKwi образцом, введение мул тдаплексо 12 элеме нта 13 ЙЕ злемеи товЭ и 10 2Й-ИЛИ/триггёр1а 11у .iter , шифра с № 14 -и 15 позв «ляёт завлогкировать цо KaLJW3 i|y Седову та в от- дельности к сравненйё по тем выходам логи-Чёскрг Узл 8, состоянял Кото рьк не определены в тестеу что прэволяе крнтролировать широкую номенклатуру логических узлов и расЦдаряет область применения устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для формирования тестов субблока логического блока | 1987 |

|

SU1513453A1 |

| Устройство тестового контроля цифровых блоков | 1985 |

|

SU1315982A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для контроля неисправностей | 1987 |

|

SU1564626A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1545222A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1013960A1 |

МЙОГОКАЯАЛЬЙОЁ УСТРОЙСТВО. , ТЕСТОВОГО КОЙТРОЛЯ ЛОГИЧЕСКИХ УЗЛОВ, содержащее блок памяти, соеди.н«гиьй1 выходом с входом коммутатора, соеди ненного первым выходом q входсм блока управления, вторым вьвсодом -//, с входом блока приема и накопления. и)фор«4ации, соединенного первым -sfff ходом с первым входом формирователя, сигналов, вторым выходом - с вхоЯ9 дешифратора адреса, выходы соединены с соответствукади ет первы ми входами блоков контроля, сочедииеииых вторыми, третьимии четвертыми вх адами (Соответственно с первымвторым и третьим выходами формир сщДтеля-сигиалов, первыкй выходами « вторьм входом блока управлеЯйЯ, fiipdf рыми выходами - с соотдетствуюц. клеммами для подключения конта т я контролируемого логического уэдаГ аю« е ее я тем, О, с , целью расширения области йриманения, ,в него введены мультиплексор, первь деш

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля логических блоков | 1976 |

|

SU637820A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1983-10-23—Публикация

1982-07-05—Подача