113

Изобретение относится к контроль- но-измерител1 нон технике и может быть использовано в устройствах контроля динамического функционирования больших интегральных схем.

Целью изобретения является повышение точности контроля путем исключения зон неопределенного состояния узлов устройства.

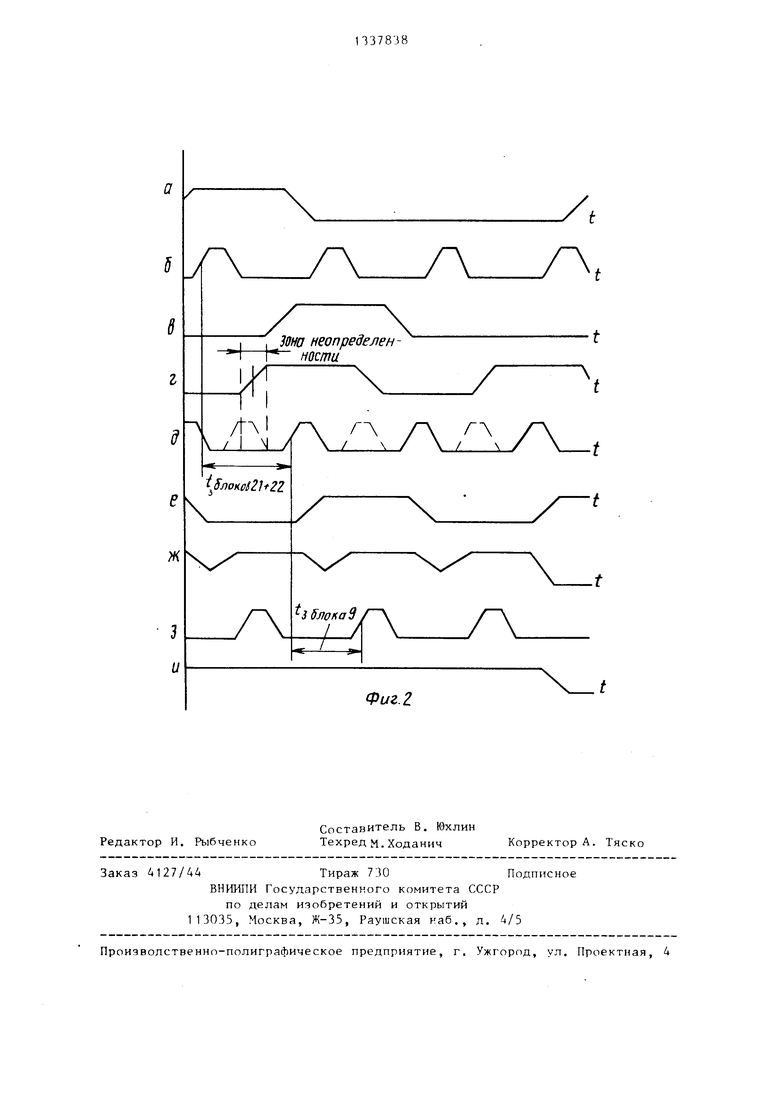

На фиг. 1 изображена схема устройства для функционального контроля цифровых интегральных схем по одному выводу; на фиг. 2 - временные диаграммы, поясняющие работу устройства.

Устройство содержит блок 1 аналоговых компараторов, состоящий из первого и второг о компараторов, выполненных на усилителях 2 и 3, первый и второй элементы памяти, выполненные на триггерах 4 и 5 соответственно, триггеры 6-8, первый элемент 9 задержки, первый коммутатор 10, выполненный на элементах И 11, 12 ИЛИ 13, информационный вход 14, первый, второй и третий управляющие входы 15-17 устройства, выход 18 устройства, источники 91 (Uoni 20 С опг опорных напряжений, BTOpoi i элемент 21 задержки, второй коммутатор 22, четвертый управляющий вход 23 устройства.

Объепиненные входы усилителей 2 и 3 блока 1 аналоговых компараторов являются информационр|ым входом 14 устройства, вторые входы усилителей 2 и 3 соединены с источниками 19 и 20 опорных напряжений, гчадающих програм- мируем 1е значения логических уровней

1

и

О соответгтненно, выходы усилителей 2 и 3 сое;; 1;(гены с первыми входами триггеров и 5 памяти, вторые входы которых соединены с первым управляющим входом i 5 устройства, входом второго эле - ента 21 задержки и первым входом второго коммутатора 22, второй вход которого соединен с выходом второго элемента 21 задержки третий вход - с четвертым управляющим входом 23 устройства, а выход - с входом первого элемента 9 задержки и С-входами триггеров 7 и 8. Выходы триггеров 4 и 5 соединены с первыми входами логических элементов И 11, 12, образующих первый и второй входы первого коммутатора 10, выходы триггера 7 соединены с вторыми входами элементов И 11, 12, образующих третий и четвертый входы первого коммутатора 10, выходы элементов И 11,

8382

12 через элемент И, 1И 13 соединены с выходом первого коммутатора 10, соединенного с D-входом первого триггера 6, С-вход которого соединен с выходом первого элемента 9 задержки, R-вход - с выходом триггера 8, выход триггера 6 является выходом 18 устройства, первые входы триггеров 7

Q и 8 соединены с управляющими входами 1 6 и 1 7 .

Вход 15 спутк ит для подключения источника строб-импульсов вход 16 - для подключения источника эталонной

t, информации, вход 17 -для подключения источника управляющих сигналов записи - считывания информации, вход 23 - для подключения источника управляющих сигналов, в качестве которого может

Q быть использован блок памяти, подключенный к информационной шине ЭВМ, а выход 18 - для подключения средств обработки информации - результата контроля.

5 Устройство для функционального контроля цифровых интегральных схем работает следующим образом.

На информационный вход 14 устрой-- ства поступает выходной сигнал с ис0 пытуемой микросхемы с заданной частотой контроля (фиг. 2а). В блоке 1 . аналоговых компараторов происходит сравнение выходных сигналов микросхемы с логическими уровнями 1 и О, задаваемыми источниками 19 и 20 опорных напряжений. На управляющий вход 16 и, следовательно, на первый вход триггера 7 поступает сигнал эталонной информации (фиг. 2г), на управляющий вход 17 постоянно поступает сигнал

5

10

45

0

35

разрешения контроля, управляющий работой выходного трит гера 6. На управляющий вход 23 подается сигнал управления работой второго коммутатора 22, Этот сигнал управляет работой второго блока коммутатора 22 таким образом, что на его выход проходит строб- импульс либо непосредственно с входной клеммы 15 (фиг. 2д, пунктиром), если его местоположение на временной диаграмме работы устройства не приходится на зону неопределенности эталонной информации, либо через второй блок 21 задержки, величина которой выбирается несколько больше максимально возможной величины зоны неопределенности эталонной информации.

С приходом строб-импульса на управляющий вход 15 (фиг. 26) и, следовательно, на вторые вход1.1 тригтеров 4 и 5 в последние записывается информация, установленная в данный момент на выходах усилите:тей 2 и 3 соответственно (фи1 . 2в) ,

Эталонная информация (фиг. 2г) записывается в триггер 7 (на С-вход триггера 7 поступает в данном случае строб-импульс, задержанный элементом 21 задержки, так как в случае подачи на С-вход триггера 7 незадержанного строб-импульса триггер 7 будет находиться в неопределенном состоянии вследствие того , что время смены эталонной информации совпадает с моментом действия строб-импульса), с выхода которого она поступает в первый коммутатор 10 (фиг , 2е, информация на прямом выходе), разрешая прохождение сигналов с выходов триггеров 4 и 5 на вход выходного триггера 6. Строб-импульс с выхода второго коммутатора 22 через первый элемент задержки (значение которой выбирается несколько большим величины времени переключения триггера 7 и элементов первого коммутатора 10) поступает на второй вход триггера 6 (фиг. 2з), разрешая запись информации с выхода первого коммутатора 10 (фиг. 2ж). Если контролируемая информация на выводе испытуемой схемы соответствует по своим логическим уровням заданным значениям О и 1, а также соответствует своему ожидаемому местоположению, фиксируемому строб-импульсом, и длительность импульса соответствует длительности эталонного сигнала, то на выходе триггера 6 сигнал отсутствует. Это означает, что контролируемая цифровая микросхема функционирует верно (фиг. 2и). В противном случае на выходе триггера 6 формируется сигнал несоответствия выходной информации контролируемой микросхемы заданным требованиям, т.е. сигнал Брак.

Таким образом, в устройстве обеспечивается запись эталонной информации и управляющей и формации в соответствующие триггеры памяти в момен

5

0

5

0

5

0

5

0

ты времени, когда данная информация достоверна. Тем самым исключается зона недостоверности контроля, что позволяет проводить испытания с повышенной частотой контроля, вплоть до 100 МГц (при длительности строб-импульса 3,4 не).

Формула изобретения

Устройство для функционального контроля цифровых интегральных схем, содержащее блок аналоговых компараторов-, включающий первый и второй компараторы, объединенные входы которых являются информационным входом устройства, а выходы соединены с соответствующими первыми входами первого и второго элементов памяти, выходы которых подключены соответственно к первому и второму входам первого коммутатора, выход которого соединен с D-входом первого триггера, выход которого является выходом устройства, объединенные вторые входы элементов памяти являются первым управляющим входом устройства, первый элемент задержки, выход которого подключен к С-входу первого триггера, второй триггер, D-вход которого является вторым управляющим входом.устройства, а инвертирующий и прямой выходы подключены соответственно к третьему и четвертому входам первого коммутатора,третий триггер, D-вход которого является третьим управляющим входом устройства, а выход соединен с R-входом первого триггера, отличающееся тем, что, с целью повышения точности контроля, в него введены второй элемент задержки и второй коммутатор, первый вход которого соединен с первым управляющим входом устройства и с входом второго элемента задержки, выход которого подключен к второму входу второго коммутатора, выход которого соединен с входом первого элемента задержки и С-входом второго и третьего триггеров, третий вход второго коммутатора является четвертым управляющим входом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для функционального контроля больших интегральных схем | 1983 |

|

SU1109687A1 |

| Устройство для функционального контроля цифровых интегральных схем | 1987 |

|

SU1430915A1 |

| Устройство для функционального контроля больших интегральных схем | 1990 |

|

SU1809398A1 |

| Устройство для функционального контроля больших интегральных схем | 1985 |

|

SU1291905A1 |

| Устройство для функционального контроля больших интегральных схем | 1990 |

|

SU1798743A1 |

| МНОГОКАНАЛЬНОЕ АКУСТИКО-ЭМИССИОННОЕ УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ИЗДЕЛИЙ | 1995 |

|

RU2105301C1 |

| Устройство для автоматического контроля больших интегральных схем | 1984 |

|

SU1205083A1 |

| Устройство для функционального контроля больших интегральных микросхем | 1988 |

|

SU1583887A1 |

| МНОГОКАНАЛЬНОЕ АКУСТИКО-ЭМИССИОННОЕ УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ИЗДЕЛИЙ | 1997 |

|

RU2150698C1 |

| Устройство для контроля больших интегральных схем памяти | 1980 |

|

SU926727A1 |

Изобретение позволяет повысить точность контроля интегральных схем. Устройство содержит блок 1 аналоговых компараторов,выполненный на усилителях 2 и 3, элементы памяти, выполненные на триггерах 4 и 5, элемент 9 задержки, триггеры 6-8, источники 19 и 20 опорных напряжений и .компаратор 10, выполненный на элементах И 11 и 12 и элементе ИЛИ 13..Введением элемента 21 задержки и коммутатора 22 обеспечивается запись эталонной и управляемой информапии в со- ответствуюсдие триггеры 4 и 5 в моменты времени, когда данная информация достоверна. Тем самым исключается зона недостоверности контроля, что позволяет проводить испытания с повышенной частотой контроля, вплоть до 100 МГц, при длительности строб-импульса 3, 4 НС. 2 ил. сл

| Авторское свидетельство СССР W 1149194, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для функционального контроля больших интегральных схем | 1983 |

|

SU1109687A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-09-15—Публикация

1986-04-07—Подача