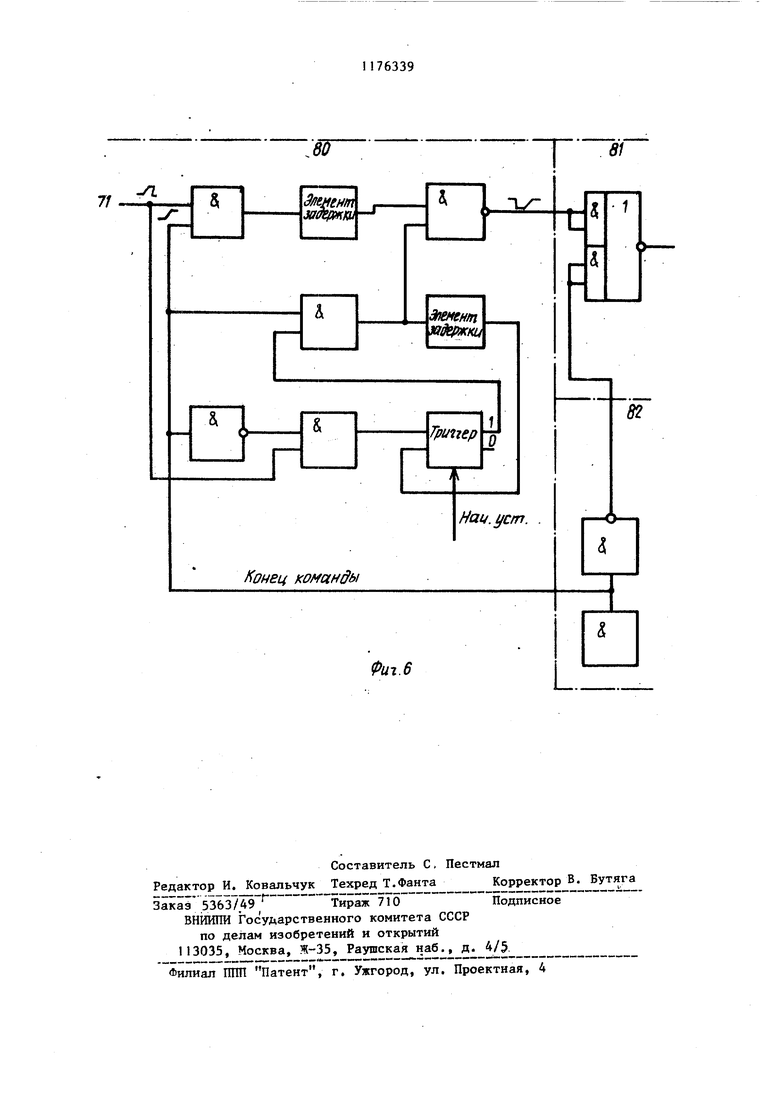

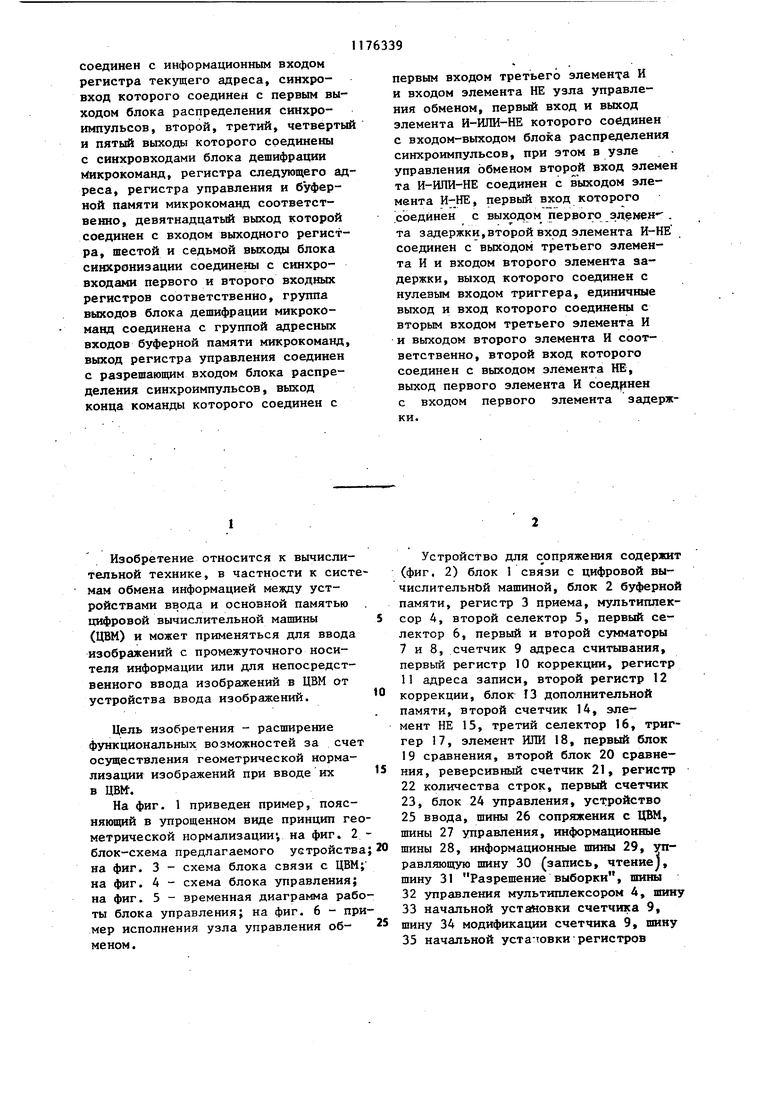

мент ИЛИ, элемент НЕ, причем девятьй выход блока управления соединен с установочными -входами первого и вто рого регистров коррекции, выходы ко торых соединены с первыми входами первого и второго сумматоров соответственно, йторые входы которых со динены с первым и втЬрым выходами регистра адреса записи соответственно, второй и третий инфо)ма1щонные входы которого соединены с вторым и третьим информационными входами мультиплексора и с выходами первого и второго сумматоров соотве ственно, второй выход регистра адреса записи соединен с входом первого селектора, выход которого соединен с первым входом элемента ИЛИ и с входом прямого счета реверсивного счетчика, вход обратного счета которого соединен со счетным входом первого счетчика и с выходом второг селектора, вход которого соединен с выходом счетчика адреса считывания, четвертый выход блока управле ния соединен с первым нулевым входо триггера, выход которого соединен с входом разрешения считьгоания блока управления, десятый выход которого соединен с входом режима блока дополнительной памяти, вход разрешения выборки которого соединен с одиннадцатым выходом блока управления, двенадцатый выход которого соединен со счетным входом второго счетчика, выходкоторого соединен с адресным входом блока дополнитель ной памяти, йервый и второй выходы которого соединены с информациЬнным входами первого и второго регистров коррекции соответственно, информационный выход блока связан с цифровой вычислительной машиной соединен с информационными входами блока дополниТельной памяти и регистра количества строк, выход которого соединен с первыми входами первого и второго блоков сравнения, вторые входы которых соединены с выходами реверсивного счетчика и первого счетчика соответственно, установочный вход которого соединен с тринад цатым выходом блока управления, четырнадцатый выход которого соединен с установочным входом реверсивного счетчика, вход записи регистра количества строк соединен с пятнадцатым выходом блока управления, шес 9 надцатый выход которого соединен с вторым входом элемента ИЛИ, выход ко торого соединен с установочным входом второго счетчика, выход первого блока сравнения соединен с входом элемента НЕ и единичным входом триггера, второй нулевой вход которого соединен с выходом третьего селектора, первый и второй входы которого соединены с выходами элемента НЕ и второго блока сравнения соответственно, при этом блок управления содержит два входных регистра, регистр управления, регистр текущего адреса, регистр следующего адреса, выходной регистр, блок дешифрации команд, буферную память микрокоманд, блок распределения синхроимпульсов, узел управления обменом, состоящий из трех элементов И, элемента НЕ, двух элементов задержки, элемента И-НЕ, триггера и элемента И-ИЛИ-НЕ, причем первый, второй входы первого входного регистра, первый, второй выходы буферной памяти микрокоманд образуют первую группу управляющих входоввыходов блока управления, третий выход буферной памяти микрокомавд, информационный вход второго входного регистра, третий, четвертый входы первого входного регистра, первые входы первого и второго элементов И узла управления обменом, тактовый вход и вход пуска блока распределения синхроимпульсов образуют вторую группу управляющих входов-выходов блока управления, пятый вход первого входного регистра является-входом разрешения считывания блока управления, четвертый и пятый выходы буферной памяти микрокоманд являются первым и вторым выходами блока управления, выход выходного регистра является третьим выходом блока управления, с шестого по восемнадцатый выходы буферной памяти микрокоманд являются с четвертого по шестнадцатый выходами блока управления соответственно, при этом Б блоке зшравления выходы первого, второго входных регистров и регистра текущего адреса соединены с первым, вторым и третьим входами блока дешифрации команд соответственно, первый и второй выходы которого соединены с информационнь1ми входами регистра упраэления и регистра следующего адреса соответственно, выход которого

соединен с информационным входом регистра текущего адреса, синхровход которого соединен с первым выходом блока распределения синхроимпульсов, второй, третий, четверты и пятый выходы которого соединены с синхровходами блока дешифрации Микрокоманд, регистра следующего адреса, регистра управления и буферной памяти микрокоманд соответственно, девятнадцатый выход которой соединен с входом выходного регистра, шестой и седьмой выходы блока синхронизации соединены с синхровходами первого и второго входных регистров соответственно, группа выходов блока дешифрации микрокоманд соединена с группой адресных входов буферной памяти микрокоманд выход регистра управления соединен с разрешающим входом блока распределения синхроимпульсов, выход конца команды которого соединен с

первым входом третьего элемента И и входом элемента НЕ узла управления обменом, первый вход и выход элемента И-ИЛИ-НЕ которого соединен с входом-выходом блока распределения синхроимпульсов, при этом в узле управления обменом второй вход элеме та И-ИПИ-НЕ соединен с выходом элемента И-НЕ, первый вход которого .соединен с выходом первого эдемен- .

та задержки,второй вход элемента И-НЕ соединен с выходом третьего элемента И и входом второго элемента задержки, выход которого соединен с нулевым входом триггера, единичные выход и вход которого соединашл с вторым входом третьего элемента И и выходом второго элемента И соответственно, второй вход которого соединен с выходом элемента НЕ, выход первого элемента И соединен с входом первого элемента задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1124379A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1984 |

|

SU1234843A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| АДАПТЕР КАНАЛ - КАНАЛ | 1991 |

|

RU2024050C1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

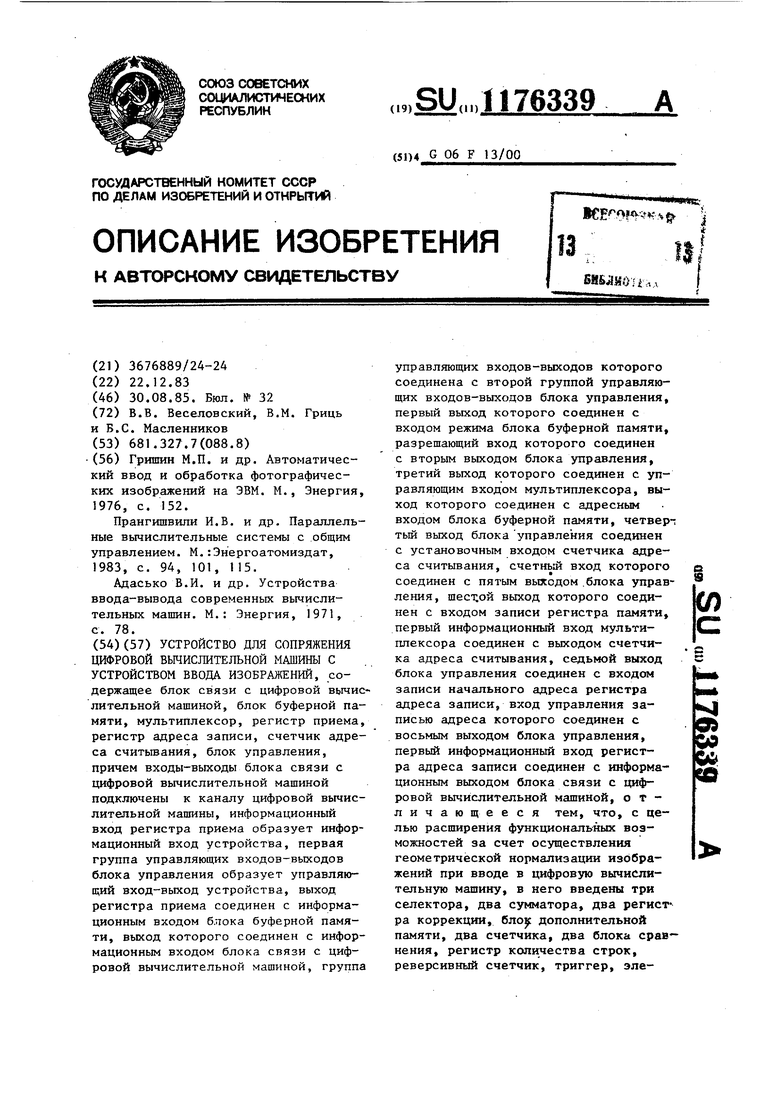

УСТРОЙСТВО ДДЯ СОПРЯЖЕНИЯ ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С УСТРОЙСТВОМ ВВОДА ИЗОБРАЖЕНИЙ, содержащее блок связи с цифровой вьгаислительной машиной, блок буферной памяти, мультиплексор, регистр приема, регистр адреса записи, счетчик адреса считьгоания, блок управления, причем входы-выходы блока связи с цифровой вычислительной машиной подключены к каналу цифровой вычислительной машины, информационный вход регистра приема образует информационный вход устройства, первая группа управляющих входов-выходов блока управления образует управляющий вход-выход устройства, выход регистра приема соединен с информационным входом блока буферной памяти, выход которого соединен с информационным входом блока связи с цифровой вычислительной машиной, группа управляющих входов-выходов которого соединена с второй группой управляющих входов-выходов блока управления, первый выход которого соединен с входом режима блока буферной памяти, разрешающий вход которого соединен с вторым выходом блока управления, третий выход которого соединен с управляющим входом мультиплексора, выход которого соединен с адресным входом блока буферной памяти, четвер-; тый выход блока управления соединен с установочным входом счетчика адреса считывания, счетньй вход которого § соединен с пятым выходом .блока управ(Л ления, щес1;ой выход которого соединен с входом записи регистра памяти, первый информационный вход мультиплексора соединен с выходом счетчика адреса считывания, седьмой выход блока управления соединен с входом записи начального адреса регистра адреса записи, вход управления записью адреса которого соединен с восьмым выходом блока управления, первый информационный вход регистра адреса записи соединен с информационным выходом блока связи с цифровой вычислительной машиной, отличающееся тем, что, с целью расширения функциональных возможностей за счет осуществления геометрической нормализации изображений при вводе в цифровую вычислительную машину, в него введены три селектора, два сумматора, два регистра коррекции, бло дополнительной памяти, два счетчика, два блока сравнения, регистр количества строк, реверсивный счетчик, триггер, эле-

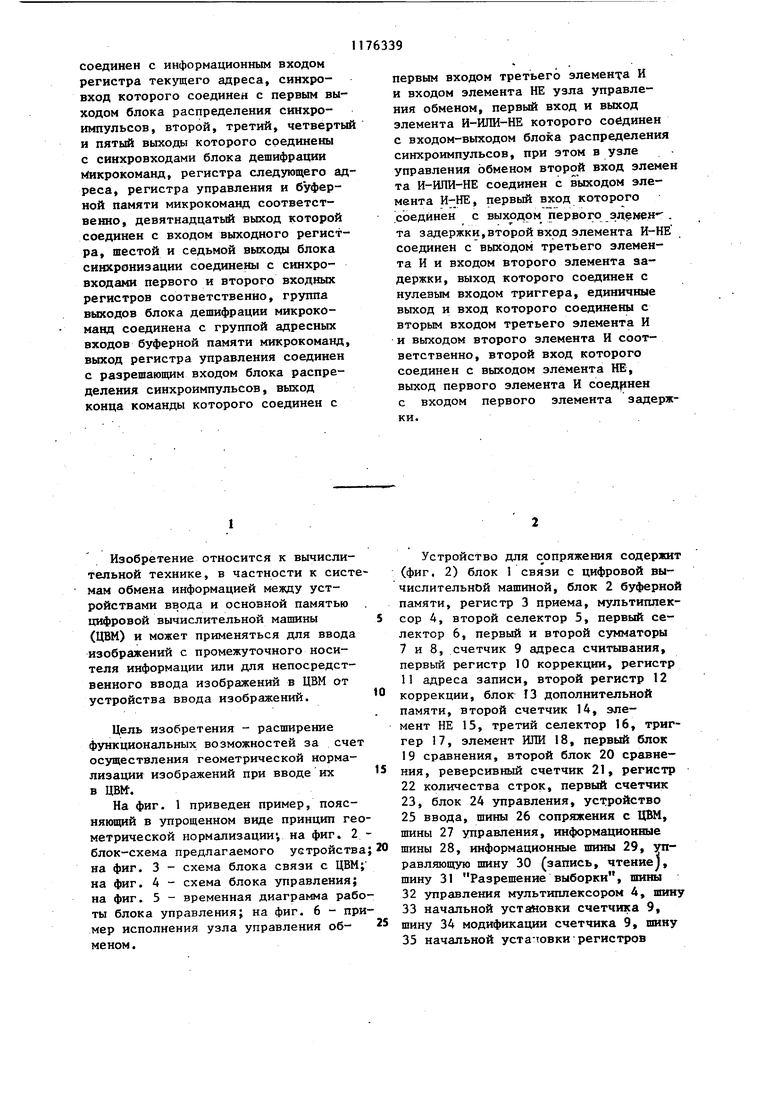

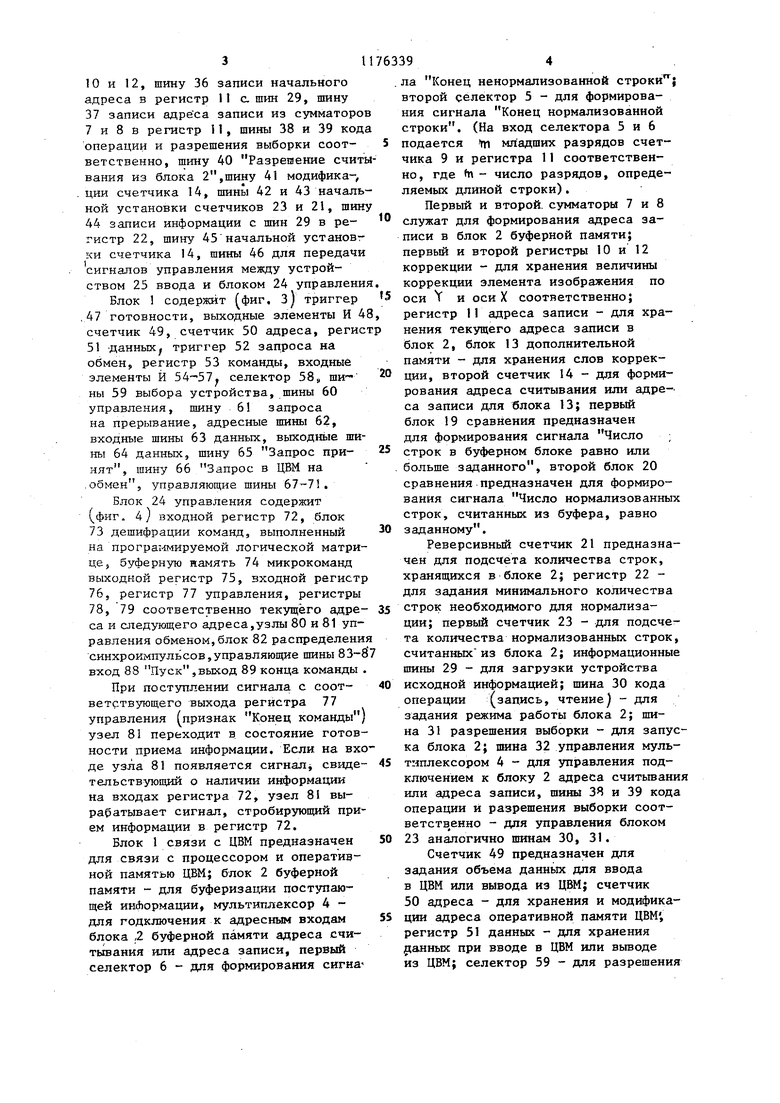

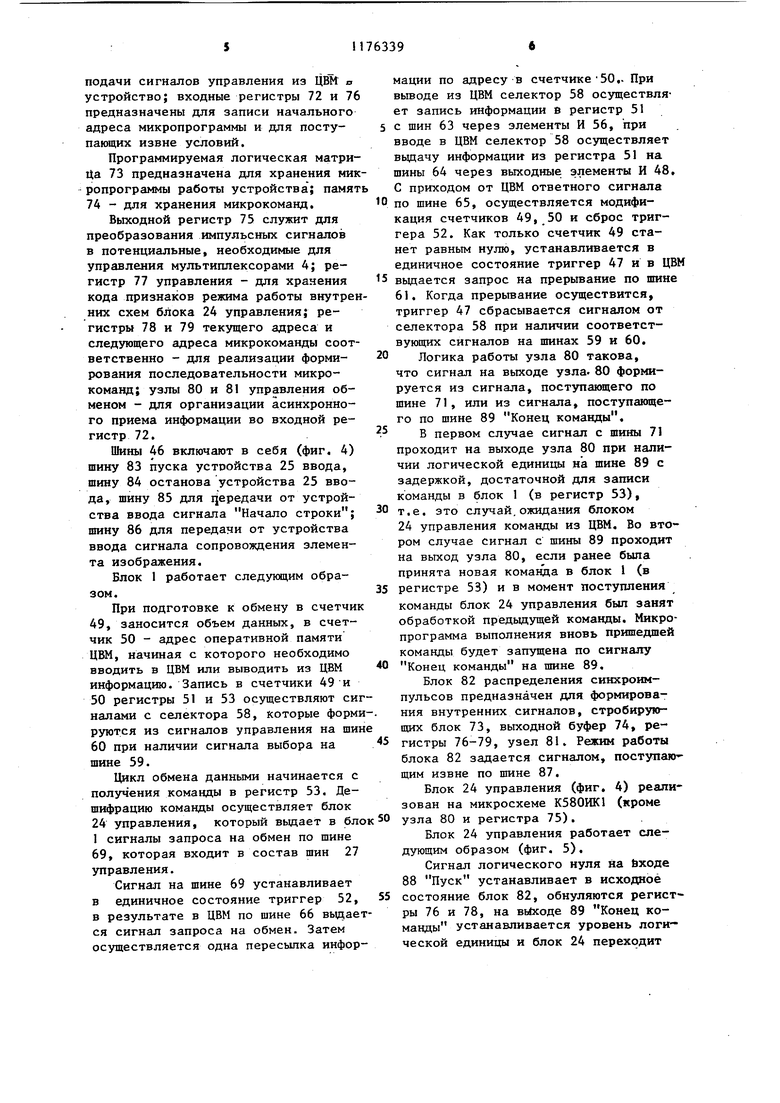

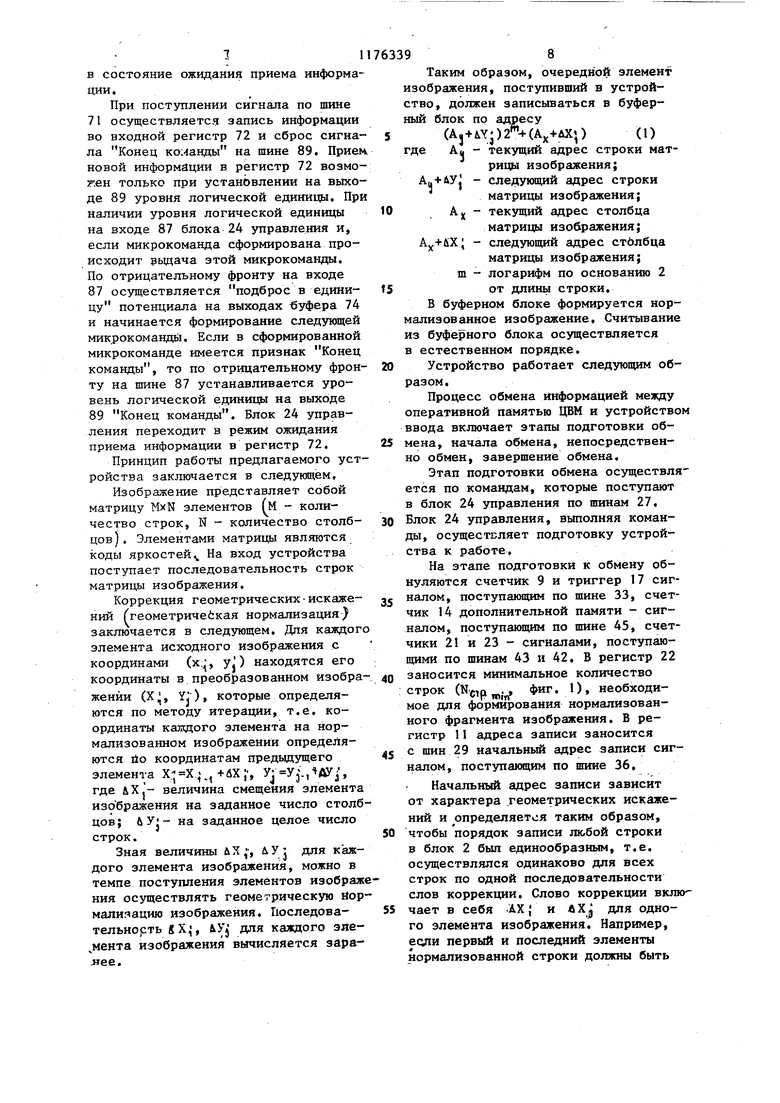

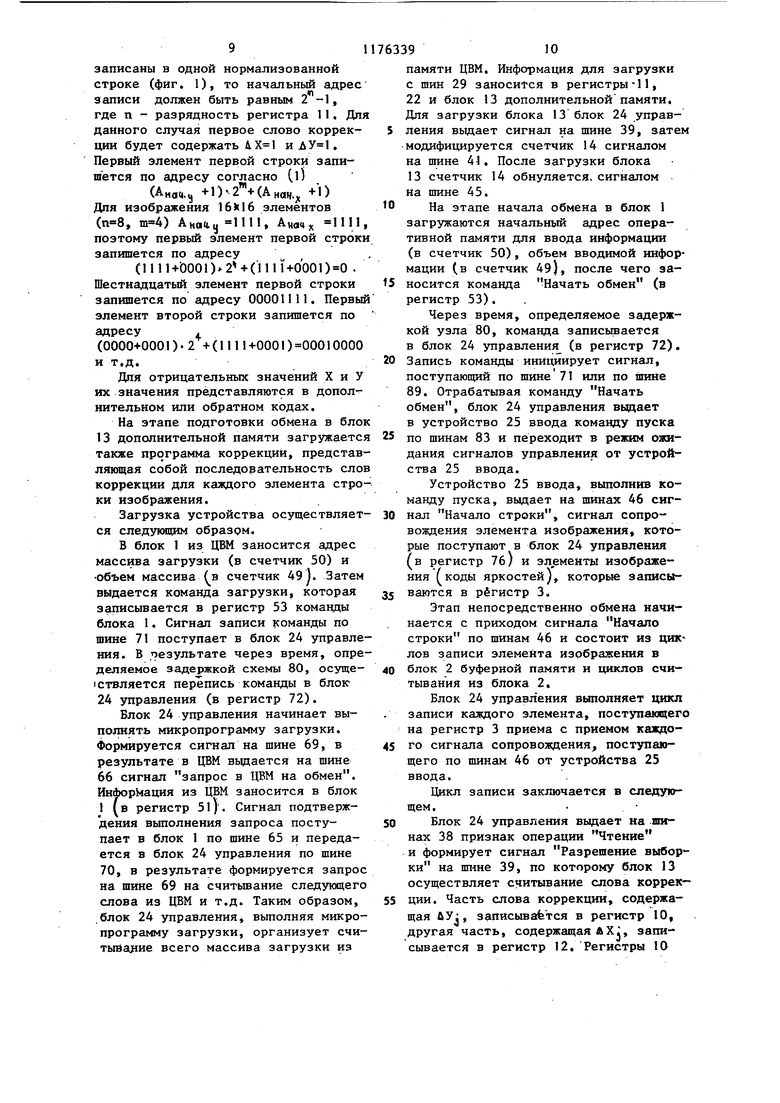

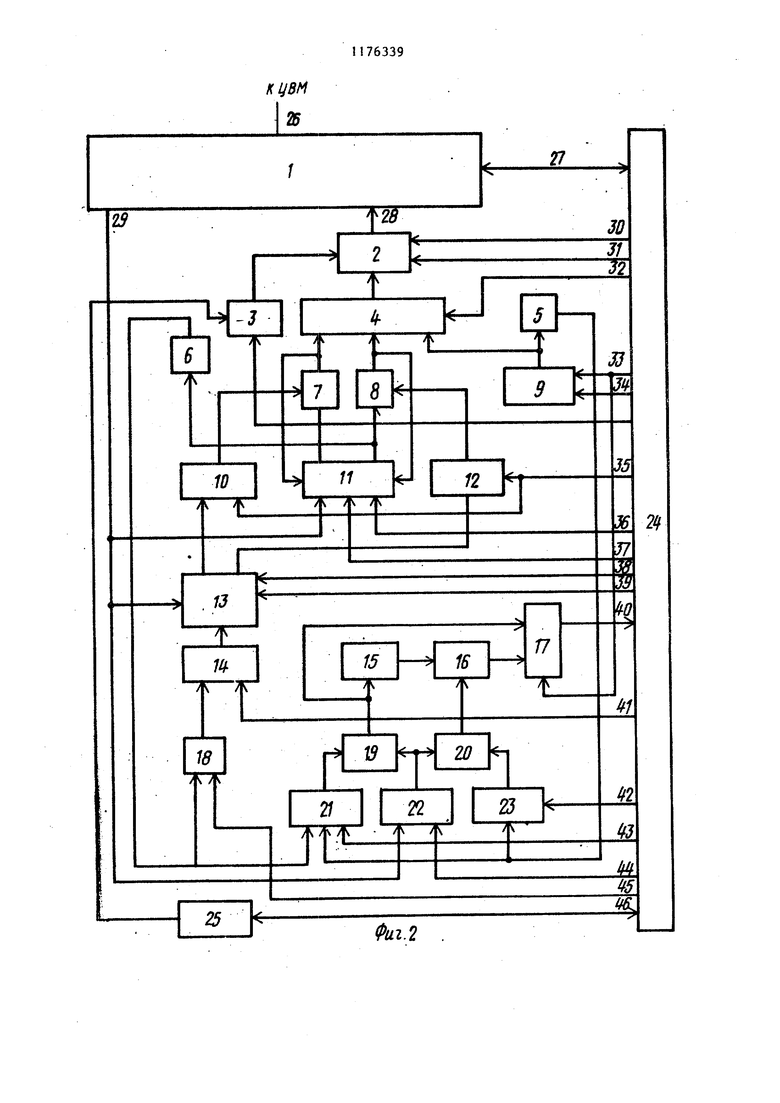

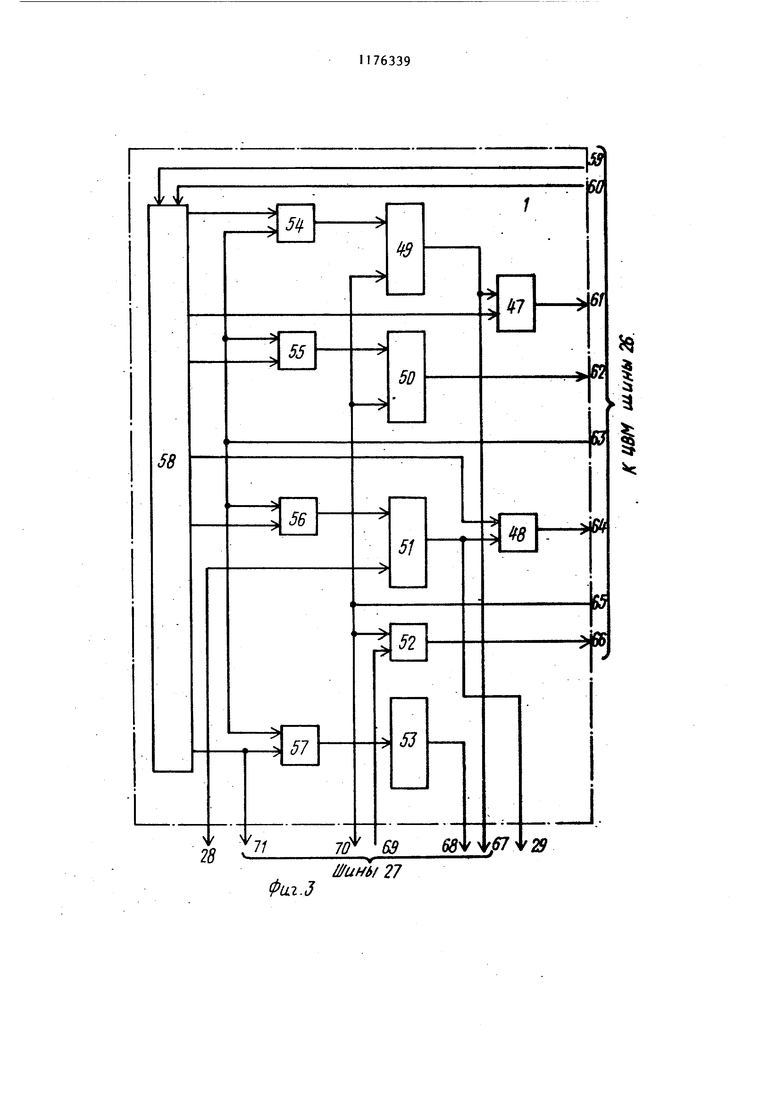

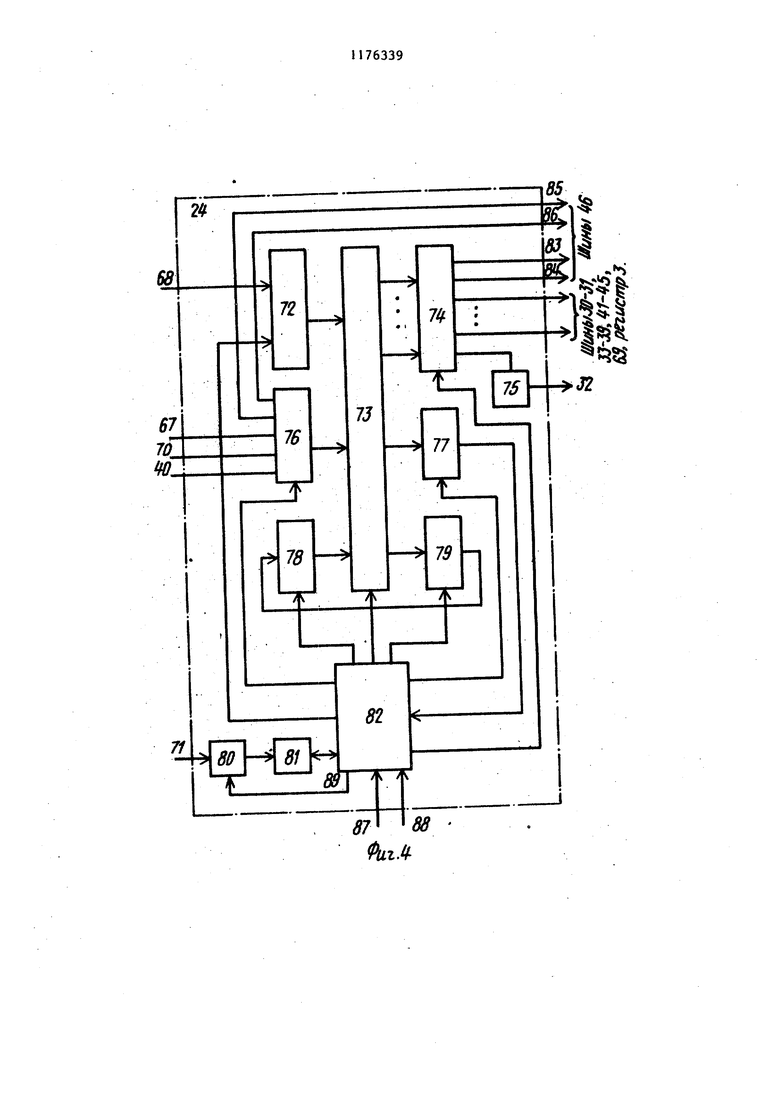

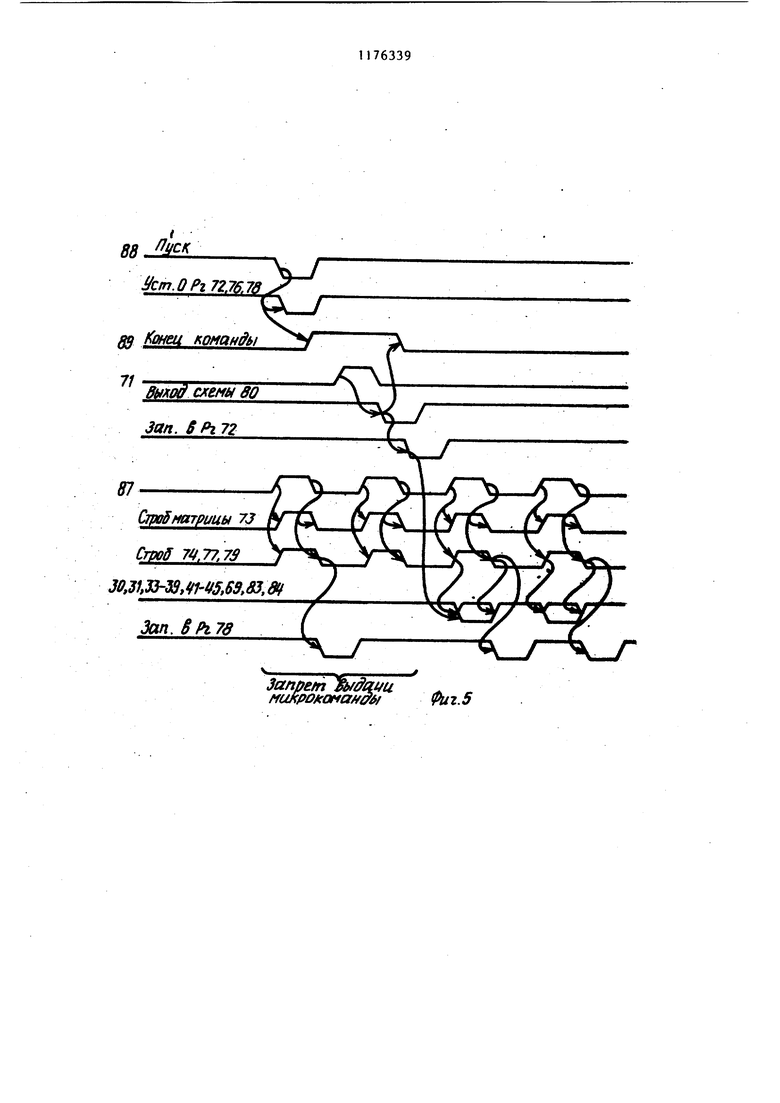

Изобретение относится к вычислительной технике, в частности к систе мам обмена информацией между устройствами ввода и основной памятью цифровой вычислительной машины (ЦВМ) и может применяться для ввода изображеиий с промежуточного носителя информации или для непосредственного ввода изображений в ЦВМ от устройства ввода изображений. Цель изобретения - расширение функциональных возможностей за счет осуществления геометрической нормализации изображений при вводе их в ЦВМ. На фиг. 1 приведен пример, поясняющий в упрощенном виде принцип гео метрической нормализации; на фиг. 2 блок-схема предлагаемого устройства на фиг. 3 - схема блока связи с ЦВМ; на фиг. 4 - схема блока управления; на фиг. 5 - временная диаграмма рабо ты блока управления; на фиг. 6 - при мер исполнения узла управления обменом. Устройство для сопряжения содержит (фиг. 2) блок 1 связи с цифровой вычислительной машиной, блок 2 буферной памяти, регистр 3 приема, мультиплексор 4, второй селектор 5, первый селектор 6, первый и второй сумматоры 7 и 8, счетчик 9 адреса считывания, первый регистр 10 коррекции, регистр 11 адреса записи, второй регистр 12 коррекции, блок 13 дополнительной памяти, второй счетчик 14, элемент НЕ 15, третий селектор 16, триггер 17, элемент ИЛИ 18, первый блок 19 сравнения, второй блок 20 сравнения, реверсивный счетчик 21, регистр 22 количества строк, первый счетчик 23, блок 24 управления, устройство 25 ввода, шины 26 сопряжения с ЦВМ, шины 27 управления, информационные шины 28, ииформационные шины 29, управляющую шину 30 (запись, чтение, шину 31 Разрешение выборки, шины 32управления мультиплексором 4, шину 33начальной установки счетчика 9, шину 34 модификации счетчика 9, шину 35 начальной установки регистров 10 и 12, шину 36 записи начального адреса в регистр П с. шин 29, шину 37 записи адреса записи из сумматоро 7 и 8 в регистр П, шины 38 и 39 код операции и разрешения выборки соответственно, шину 40 Разрепение счит вания из блока 2,шину 41 модифика-, . ции счетчика 14, шины 42 и 43 началь ной установки счетчиков 23 и 21, шин 44 записи информации с шин 29 в регистр 22, шину 45начальной установг ки счетчика 14, шины 46 для передачи сигналов управления между устройством 25 ввода и блоком 24 управлени Блок 1 содержит Гфиг. З) триггер ,47 готовности, выходные элементы И 4 счетчик 49, счетчик 50 адреса, регис 51 -данных, триггер 52 запроса на обмен, регистр 53 команды, входные элементы И 54-57. селектор 58„ ши ны 59 выбора устройства, шины 60 управления, шину 61 запроса на прерывание, адресные шины 62 входные шины 63 данных, выходные шины 64 данных, шину 65 Запрос принят, шину 66 Запрос в ЦВМ на .обмен, управляющие шины 67-71, БЛОК 24 управления содержит (фиг. 4) входной регистр 72, блок 73 дешифрации команд, выполненный на програх-мируемой логической матрице, буферную намять 74 микрокоманд выходной регистр 75, входной регистр 76, регистр 77 управления, регистры 78, 79 соответственно текущего адреса и следующего адреса,узлы 80 и 81 управления обменом,блок 82 распределени синхроимпульсов,управляющие шины вход 88 Пуск,выход 89 конца команды . При поступлении сигнала с соответствующего выхода регистра 77 управления (признак Конец команды) узел 81 переходит в состояние готовности приема информации. Если на вхо де узла 81 появляется сигналj свидетельствующий о наличии информации на входах регистра 72, узел 81 вырабатывает сигнал, стробирующий прием информации в регистр 72, Блок 1 связи с ЦВМ предназначен для связи с процессором и оперативной памятью ЦВМ; блок 2 буферной памяти - для буферизации поступающей информации, мультиплексор 4 для подключения к адресным входам блока ,2 буферной памяти адреса считьшания Ш1И адреса записи, первый селектор 6 - для формирования сигна 394 ла Конец ненормализованной строки ; второй селектор 5 - для формирования сигнала Конец нормализованной строки, (На вход селектора 5 и 6 подается т младших разрядов счетчика 9 и регистра 11 соответственно, где fn - число разрядов, определяемых длиной строки), Первый и второй, сумматоры 7 и 8 служат для формирования адреса записи в блок 2 буферной памяти; первый и второй регистры 10 и 12 коррекции - для хранения величины коррекции элемента изображения по оси V и оси X соответственно; регистр 11 адреса записи - для хранения текущего адреса записи в блок 2, блок 13 дополнительной памяти - для хранения слов коррекции, второй счетчик 14 - для формирования адреса считывания или адреса записи для блока 13; первый блок 19 сравнения предназначен для формирования сигнала Число ; строк в буферном блоке равно или больше заданного, второй блок 20 сравнения предназначен для формирования сигнала Число нормализованных строк, считанных из буфера, равно заданному, Реверсивньй счетчик 21 предназначен для подсчета количества строк, хранящихся в блоке 2; регистр 22 для задания минимального количества строк необходимого для нормализации; первый счетчик 23 - для подсчета количества нормализованных строк, считанных из блока 2; информационные шины 29 - для загрузки устройства исходной информацией; шина 30 кода операции (запись, чтение - для задания режима работы блока 2; шина 31 разрешения выборки - для запуска блока 2; шина 32 управления мультиплексором 4 - для управления подключением к блоку 2 адреса считывания или адреса записи, шины ЗЯ и 39 кода операции и разрешения выборки соответств енно - для управления блоком 23 аналогично шинам 30, 31, Счетчик 49 предназначен для задания объема данных для ввода в ЦВМ или вывода из ЦВМ; счетчик 50 адреса - для хранения и модификации адреса оперативной памяти ЦВМ , регистр 51 данных - для хранения {(анных при вводе в ЦВМ или вьгаоде из ЦВМ; селектор 59 - для разрешения подачи сигналов управления из ЦБК а устройство; входные регистры 72 и 7 предназначены для записи начального адреса микропрограммы и для поступающих извне условий. Программируемая логическая матри ца 73 предназначена для хранения ми ропрограммы работы устройства; памя 74 - для хранения микрокоманд, Выходной регистр 75 служит для преобразования импульсных сигналов в потенциальные, необходимые для управления мультиплексорами 4; регистр 77 управления - для хранения кода признаков режима работы внутре них схем блока 24 управления; регистры 78 и 79 текущего адреса и следующего адреса микрокоманды соот ветственно - для реализации формирования последовательности микрокоманд; узлы 80 и 81 управления обменом - для организации асинхронного приема информации во входной регистр 72. Шины 46 включают в себя (фиг. 4) шину 83 пуска устройства 25 ввода, шину 84 останова устройства 25 ввода, шину 85 для передачи от устройства ввода сигнала Начало строки ; шину 86 для передачи от устройства ввода сигнала сопровождения элемента изображения. Блок 1 работает следующим образом. При подготовке к обмену в счетчи 49, заносится объем данных, в счетчик 50 - адрес оперативной памяти ЦВМ, начиная с которого необходимо вводить в ЦВМ или выводить из ЦВМ информацию. Запись в счетчики 49 и 50 регистры 51 и 53 осуществляют си налами с селектора 58, которые форм руются из сигналов управления на ши 60 при наличии сигнала выбора на шине 59. Цикл обмена данными начинается с получения команды в регистр 53. Дешифрацию команды осуществляет блок 24 управления, который вьщает в бл 1 сигналы запроса на обмен по шине 69, которая входит в состав шин 27 управления. Сигнал на шине 69 устанавливает в единичное состояние триггер 52, в результате в ЦВМ по шине 66 вьщае ся сигнал запроса на обмен. Затем осуществляется одна пересылка инфор мации по адресу в счетчике50,. При вьгооде из ЦВМ селектор 58 осуществляет запись информации в регистр 51 с шин 63 через элементы И 56, при вводе в ЦВМ селектор 58 осуществляет выдачу информации из регистра 51 на шины 64 через выходные элементы И 48. С приходом от ЦВМ ответного сигнала по шине 65, осуществляется модификация счетчиков 49, 50 и сброс триггера 52. Как только счетчик 49 станет равным нулю, устанавливается в единичное состояние триггер 47 и в ЦВМ выдается запрос на прерывание по шине 61. Когда прерьшание осуществится, триггер 47 сбрасывается сигналом от селектора 58 при наличии соответствующих сигналов на шинах 59 и 60. Логика работы узла 80 такова, что сигнал на выходе узла. 80 формируется из сигнала, поступающего по шине 71, или из сигнала, поступающего по шине 89 Конец команды. В первом случае сигнал с шины 71 проходит на выходе узла 80 при наличии логической единицы на шине 89 с задержкой, достаточной для записи команды в блок 1 (в регистр 53), т.е. это случай,ожидания блоком 24 управления команды из ЦВМ. Во втором случае сигнал с шины 89 проходит на выход узла 80, если ранее была принята новая команда в блок 1 (в регистре 53) и в момент поступления команды блок 24 управления был занят обработкой предыдущей команды. Микропрограмма выполнения вновь пришедшей команды будет запущена по сигналу Конец команды на шине 89. Блок 82 распределения синхроимпульсов предназначен для формирования внутренних сигналов, стробирующих блок 73, выходной буфер 74, регистры 76-79, узел 81. Режим работы блока 82 задается сигналом, поступаю-щим извне по шине 87. Блок 24 управления (фиг. 4) реализован на микросхеме К580ИК1 (кроме узла 80 и регистра 75). Блок 24 управления работает следующим образом (фиг. 5). Сигнал логического нуля на йходе 88 Пуск устанавливает в исходное состояние блок 82, обнуляются регистры 76 и 78, на 89 Конец команды устанавливается уровень логической единицы и блок 24 переходит 1 в состояние ожидания приема информа ции. При поступлении сигнала по шине 71 осуществляется запись информации во входной регистр 72 и сброс сигна ла Конец команды на шине 89. Прие новой информации в регистр 72 возмо у:ен только при установлении на выхо де 89 уровня логической единицы. Пр наличии уровня логической единицы на входе 87 блока 24 з равления и, если микрокоманда сформирована происходит выдача этой микрокоманды. По отрицательному фронту на входе 87 осуществляется подброс в единицу потенциала на выходах буфера 74 и начинается формирование следующей микрокоманды. Если в сформированной микрокоманде имеется признак Конец команды, то по отрицательному фрон ту на шине 87 устанавливается уровень логической единицы на выходе 89 Конец команды. Блок 24 управления переходит в режим ожидания приема информации в регистр 72. Принцип работы предлагаемого уст ройства заключается в следующем. Изображение представляет собой матрицу MxN элементов fM - количество строк, N - количество столбцов). Элементами матрицы являются коды яркостей На вход устройства поступает последовательность строк матрицы изображения. Коррекция геометрических- искажений Ггеометричейкая нормализация) заключается в следующем. Для каждог элемента исходного изображения с координами (x.j, yj) находятся его координаты в преобразованном изобра жении (X , Yj), которые определяются по методу итерации, т.е. координаты каждого элемента на нормализованном изображении определяются йо координатам предьщущего элемента Х. Х ,, + йХ ;, У| У., j, где iXJ- величина смещения элемента изображения на заданное число столб цов; UУ- на заданное целое число строк. Зная величины &X;, &yj для каждого элемента изображения, можно в темпе поступления элементов изображ ния осуществлять геометрическую йор малияацию изображения. Последовательность SX;, У} для каждого эяе мента изображения вычисляется заралее. 98 Таким образом, очередной элемент изображения, поступивший в устройство, должен записьгааться в буферный блок по адресу (Aj+iY.)2(A -b&X;) (1) где Аи - текущий адрес строки матрицы изображения; Ay+iyj - следующий адрес строки матрицы изображения; х текущий адрес столбца матрицы изображения; A +fiXj - следующий адрес стблбца матрицы изображения; m - логарифм по основанию 2 от длины строки. В буферном блоке формируется нормализованное изображение. Считывание из буферного блока осуществляется в естественном порядке. Устройство работает следующим образом. Процесс обмена информацией между оперативной памятью ЦВМ и устройством ввода включает этапы подготовки обмена, начала обмена, непосредственно обмен, завершение обмена. Этап подготовки обмена осуществляется по командам, которые поступают в блок 24 управления по шинам 27. Блок 24 управления, выполняя команды, осуществляет подготовку устройства к работе. На этапе подготовки к обмену обнуляются счетчик 9 и триггер 17 сигналом, поступающим по шине 33, счетчик 14 дополнительной памяти - сигналом, поступакндим по шине 45, счетчики 2 и 23 - сигналами, поступающими по шинам 43 н 42, В регистр 22 заносится минимальное количество строк (Nctp да{ 1), необходимое для формирования нормализованного фрагмента изображения. В регистр 1I адреса записи заносится с шин 29 начальный адрес записи сигн:алом, поступающим по шине 36. Начальный адрес записи зависит от характера геометрических искажений и определяется таким образом, чтобы порядок записи любой строки в блок 2 был единообразным, т.е. осуществлялся одинаково для всех строк по одной последовательности слов коррекции. Слово коррекции вклю чает в себя .АХ и Xj для одного элемента изображения. Например, если первый и последний элементы нормализованной строки должны быть

91

записаны в одной нормализованной строке (фиг, 1), то начальный адрес записи должен быть равным 2-1, где п - разрядность регистра 11. Для данного случая первое слово коррекции будет содержать Д. . Первый элемент первой строки запишется по адресу согласно (l)

(Анам.,, -И)(А„ач. +О Дпя изображения 16kl6 элементов (, ) Анапу 1111, lllli поэтому первый элемент первой строки запишется по адресу

(inivoooo 2U(:nn+oooi)o.

Шестнадцатый элемент первой строки запишется по адресу 00001111. Первый элемент второй строки запишется по адресу ,

(0000+0001).2 +(1П1+0001)00010000 и т.д.

Дпя отрицательных значений X и У их значения представляются в дополнительном или обратном кодах.

На этапе подготовки обмена в блок 13 дополнительной памяти загружается также программа коррекции, представляющая собой последовательность слов коррекции для каждого элемента строки изображения.

Загрузка устройства осуществляется следуницим образрм.

В блок 1 из ЦВМ заносится адрес массива загрузки (в счетчик 50) и объем массива (в счетчик 49 1. Затем выдается команда загрузки, которая записывается в регистр 53 команды блока 1. Сигнал записи команды по шине 71 поступает в блок 24 управления. В пезультате через время, определяемое задержкой схемы 80, осущеютвляется перепись команды в блок 24 управления (в регистр 72).

Блок 24 управления начинает выполнять микропрограмму загрузки. Формируется сигнал на шине 69, в результате в ЦВМ вьщается на шине 66 сигнал запрос в ЦВМ на обмен. Инфор)4ация из ЦВМ заносится в блок 1 (в регистр 51). Сигнал подтверждения выполнения запроса поступает в блок 1 по шине 65 и передается в блок 24 управления по шине 70, в результате формируется запрос на шине 69 на считывание следующего слова из ЦВМ и т.д. Таким образом, блок 24 управления, выполняя микропрограмму загрузки, организует считывa иe всего массива загрузки из

910

памяти ЦВМ. Информация для загрузки с шин 29 заносится в регистры , 22 и блок 13 дополнительной памяти. Для загрузки блока 13 блок 24 управления выдает сигнал на шине 39, затем модифицируется счетчик 14 сигналом на шине 41. После загрузки блока 13 счетчик 14 обнуляется, сигналом на шине 45.

На этапе начала обмена в блок 1 загружаются начальньй адрес оперативной памяти для ввода информации (в счетчик 50), объем вводимой информации (в счетчик 49), после чего заносится команда Начать обмен (в регистр 53).

Через время, определяемое задержкой узла 80, команда записьтается в блок 24 управления (в регистр 72).

Запись команды инициирует сигнал, поступающий по шине71 или по imrae 89. Отрабатывая команду Начать обмен, блок 24 управления вьщает в устройство 25 ввода команду пуска

по шинам 83 и переходит в режим ожидания сигналов управления от устройства 25 ввода.

Устройство 25 ввода, выполнив команду пуска, выдает на шинах 46 сигнал Начало строки, сигнал сопровождения элемента изображения, которые поступают в блок 24 управления (в регистр 76) и элементы изображения (коды яркостей), которые записываются в регистр 3.

Этап непосредственно обмена начинается с приходом сигнала Начало строки по шинам 46 и состоит из циклов записи элемента изображения в

блок 2 буферной памяти и циклов считывания из блока 2,

Блок 24 управления выполняет цикл записи каждого элемента, поступающего на регистр 3 приема с приемом каждого сигнала сопровождения, поступающего по шинам 46 от устройства 25 ввода.

Цикл записи заключается в следующем.

Блок 24 управления выдает на шинах 38 признак операции Чтение и формирует сигнал Разрешение выборки на шине 39, по которому блок 13 осуществляет считывание слова коррек-

ции. Часть слова коррекции, содержащая йУ;, записывается в регистр 10, другая часть, содержащая ЛXI, записывается в регистр 12. Регистры 10 и 12 перед каждой записью информа.ции обнуляются CHPHajjoM, поступающим по шине 35, Затем содержимое регистра 10 суммируется со старшими разрядами регистра И, а содерлаадое регистра 12 - с младшими разрядами регистра 11.Количество разрядов регистра 11, подаваемых на сумматоры 7 и 8, определяется длиной строки изображения Для Ьтроки в 4096 элементов на сумматор 8 подаются 12 младших разрядов регистра 11, на сум матор 7 - остальные разряды регистра 1- 1 . На выходе сумматоров 7 и 8 формируется адрес записи, по которому необходимо записать элемент изображения в блок 2. Для записи в блок 2 блок 24 управления формирует сигнал выбора адреса на шинах 32, подключая тем самым сумматоры 7 и 8 к адресным входа блока 2 и формирует на шинах 30 приз нак операции Запись, а на шине 31 Разрешение выборки, по которому блок 2 осуществляЬт запись элемента изображения из регистра 3 приема по а,цресу, сформированному в сумматорах 7 и 8. В каждом цикле записи в соответст вующие моменты времени, определяемые микропрограммой блока 24 управления, осуществляется модификация счетчика 14 (прибавляется единица) сигналом по шине 41 и перепись нового адреса в регистр 1I из сумматоров 7 и 8 сиг налом по шине 37, При записи последнего элемента строки на выходе схемы совпадения 6 формируется сигнал Конец ненормализованной строки, который обнуляет счетчик 14 через элемент ИЛИ 19 и пр бавляет единицу к реве1 сивному счетчику 21, Реберсивный счетчик 21 определяет 45 мое

количество строк, записанных в блоке 2 буферной памяти. Блок 24 управления по условию на шине 40 следит за заполнением блока 2,

При возникновении сигнала на выхо-50 де блока 19 сравнения, что свидетельствует о том, что в блоке 2 записан фрагмент изображения, достаточный для разрешения считьгоания, по фронту сигнала устанавливается в состояние еди-55 ницы 17 разрешения считывания из бгока 2 буферной памяти. Блок 24 управления в каждом цикле обмена

в единицу триггер 17,

Если в ЦВМ передалось необходимое количе ство информации, которое задается счетчиком объема данных в блоке 1, .то на выходе счетчика 49 формируется сигнал Завершение обмена, поступанзщий по шине 67 в блок 24 управления. По сигналу Завершение обмена блок 1 формирует запрос на прерывание и вьщает его в ЦВМ по шинам 26, а блок 24 управления останавливает обмен, В устройство 25 3912 проверяет условие на шине 40,, Если триггер. 17 находится в состоянии еди-t ницы, то в каждом цикле обмена выполняется как цикл записи в блок 2, так и цикл считыван-ия из блока 2 (моменты записи и считывания из блока 2 разнесены по времени), В хщкле считывания из блока 2 блок 24 управления сигналомна шинах 32 подключает счетчик 9 к адресным шинам блока 2, формирует на шинах 30 признак операции Чтение и выдает сигнал разрешение выборки по шине 31, В результате по адресу из счетчика 9 адреса считьтания блок 2 считывает элемент изображения и выдает его в блок 1 по шинам 28 для передачи в ЦВМ, Элемент изображения записывается в регистр 51,. Цикл считывания осуществляется, если предыдущий элемент передан в ЦВМ, что определяется блоком 24 управления по условию на шине 70 Запрос принят, Цри возникновении на выходе селектора 5 сигнала Конец нормализованной строки в счетчик 23 прибавляется единица, а из реверсивного . счетчика 21 вычитается единица, Если из блока 2 считан фрагмент изображения, определяемый количеством строк в регистре 22, на выходе блока 20 сравнения формируется сигнал , который сбрасьгоает триггер 17 разрешения считывания, если в блоке 2 записано количество строк меньшее заданного в регистре 22, Сброс триггера 17 осуществляется по фронту сигнала с селектора 16, Т,е, если очередной фрагмент изображения не подготовлен для считывания, считывание приостанавливается до тех пор, пока в блок 2 не запишется необходиколичество строк и установится

ввода вьщается команда останова по шинам 46.

Реализация геометрической нормализации в устройстве для сопряжения позволяет снять функции геометрической Нормализации с процессора ЦВМ, 4ТО приводит к значительной экономии чашинного времени, т.е. повышает производительиость систех обработки изображений.

Стирка нормализоблнного U30wa:f Hufi, cvuffa i6aeffoii изоу рного S/tOKCL

.«

IffJfO SKff

жщ/я на .flUMBafffoff, запис ваеная SSi/ipeffftiaSaOK

KljBM

25

И/ины 27

Фаг.З

}Q I

яя fJjicK I/cm. О Рг 7276.7В . -JV89 Abwa/ KQMCiHffki 8ь1ш схемы во Jan. бРг72 (ро5натрииы 73 CrpoS 7.77.7S 3D,,J,if1if5.B3.83,8tf Зап.

Запрет at/u ffu/(po/(oi a//ff6/ тг.э

| Гришин М.П | |||

| и др | |||

| Автоматический ввод и обработка фотографических изображений на ЭВМ | |||

| М., Энергия, 1976, с | |||

| Способ образования азокрасителей на волокнах | 1918 |

|

SU152A1 |

| Прангишвили И.В | |||

| и др | |||

| Параллельные вычислительные системы с общим управлением | |||

| М.:Энергоатомиздат, 1983, с | |||

| Экономайзер | 0 |

|

SU94A1 |

| Адасько В.И | |||

| и др | |||

| Устройства ввода-вывода современных вычислительных машин | |||

| М.: Энергия, 1971, с | |||

| Парный автоматический сцепной прибор для железнодорожных вагонов | 0 |

|

SU78A1 |

Авторы

Даты

1985-08-30—Публикация

1983-12-22—Подача