Изобретение относится к области вычислительной техники и техники связи и может быть использовано при построении вычислительпых структур и коммутаторов цифровых систем связи.

Известны коммутаторы дискретных сигналов, содержащие коммутирующее поле, управляющий блок, регистр, триггеры и логические элементы 1.

Недостаток устройства - возможность коммутации только в соответствии с сортирующими векторами.

Кроме того, известны коммутирующие устройства дискретных сигналов, содерл-;аЩие регистр, дешифраторы, соединенные с блоком настройки и логические элементы

2.

Недостатком известного устройства являются ограниченные функциональные возможности, обусловленные большим числом управляющих сигналов, требуемых для перехода от одной программы работы к другой, сложностью наращивания емкости коммутатора, и отсутствием возможности соединения одного входа с несколькими выходами.

С целью расширения функциональных возможностей в коммутатор дискретных сигналов, содержащий регистр коммутируемых данных, К дешифраторов и блок настройки, первые выходы которого соединены с первыми входами дешифраторов, введены/С матриц памяти, управляющие входы которых соединены с выходами соответствующих дешифраторов, информационные входы - с вторыми выходами блока настройки, а выходы соединены поразрядно и подключены к выходным шинам. При этом третьи выходы блока настройки соединены

10 с входами регистра коммутируемых данных, выходы которого подключены к вторым входам соответствующих дешифраторов.

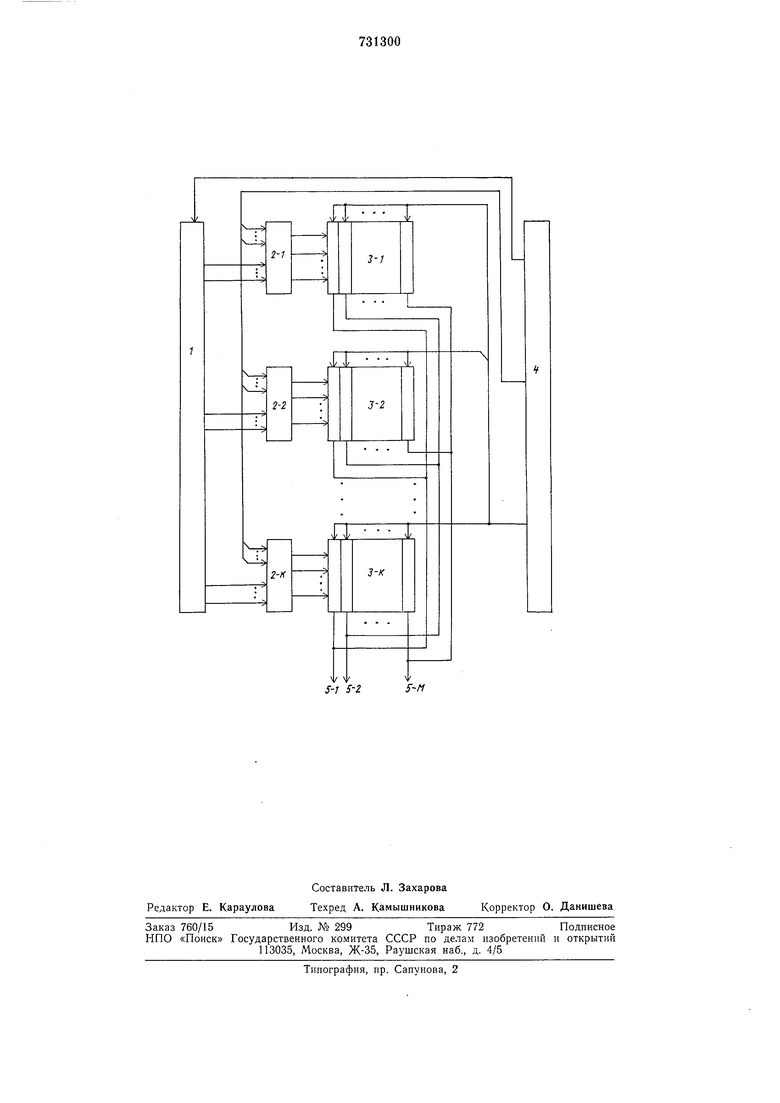

Функциональная схема устройства приведена на чертеже, где регистр 1 коммутируе15 мых данных соединен через дешифраторы

2-1-2-К с матрицами памяти 3-1-3-К,

блок 4 настройки коммутатора, выходные

шины (выходы) 5-1-5-М.

Устройство работает следующим обра20 зом.

В режиме индивидуальной настройки по каждому разряду на информационные входы матриц памяти 3-1-3-К с блока 4 иастройки подается двоичный код номера выхода, на который должен быть подключен один из входов. На вход дешифратора 2-1, соответствующего коммутируемому выходу регистра 1, подается «1, на другие входы дешифратора 2-1 подается код номера про30 граммы, с блока 4 настройки, а на остальные входы дешифратора 2-1 подаются последовательные значения двоичного ряда чисел. При получении максимального числа разрядности (п «1) настройка по данному разряду прекращается. Аналогично осуш,ествляется настройка по другим разрядам и другим программам. Для соединения одного входа с несколькимн BUxOy-iaMH номера выходов с блока 4 настройки подаются одновременно.

При групповой настройке слова настройки формируются в блоке 4 настройки но всем разрядам н настройкн осуществляется путем записи слов в матрицы памяти 3-1-3-/С.

Для работы устройства по сортирующим векторам в матрицы памяти 3-1-3-К. записывается последовательность выходов (коды выходов могут быть зашиты в матрицу постояиных запоминающих устройств).

Для настройки на выполнение системы булевых функций в матрицы 3-1-3-/С памяти записываются результаты рещений булевых функций по каждой из программ. В режиме коммутации по программе блок 4 настройки выдает код программы на входы дешифраторов 2-1-2-К, а коммутируемые сигналы выдаются из регистра 1 данных на входы дещифраторов 2-1-2-К, т. е. на входы дешифраторов 2-1-2-К будут поданы адреса соответствующих ячеек памяти, в результате чего по /-му разряду матриц памяти 3-1-3-К будет считана «1, соответствующая «1 коммутируемого выхода регистра 1 данных. При наличии «О в коммутируемом выходе регистра 1 данных считывание производиться не будет, так как при настройке по данному адресу в соответствующий разряд матрицы памяти 3-1-3-К не была записана «1. Аналогично и одновременно со считыванием по /-му разряду будет осуществляться считывание но остальным разрядам матриц памяти 3-1-3-К.

При переходе к другой программе достаточно изменить код номера программы на выходах младщих разрядов дещифраторов 2-1-2-К, причем код программы для каждого дешифратора будет одинаков.

В режиме коммутации по сортирующим векторам значения сортирующих векторов подаются на младшие разряды дещифраторов 2-1-2-К, на старшие разряды которых из регистра 1 выдаются значения коммутируемых перемеиных. Так, например, при ко.ммутации двух переменных одннм дещифратором 2 и одной матрицей 3 два старших разряда дешифратора 2 используются в качестве входов коммутируемых переменных, а 2 log2M младщих разрядов в качестве входов значений двух сортирующих векторов.

В режиме рещения системы логических уравнений на младшие разряды дешифраторов 2-1-2-К с блока 4 настройки подается номер решаемой системы логических уравнений, а на другие входы - двоичные переменные. С объединенных выходов матриц памятн 3-1-3-К будут выдаваться результаты решения логических уравнений.

Таким образом, устройство просто в управлении, кроме того, для увеличення емкости коммутатора но входам достаточно нодключить дополнительные дешифраторы с матрицами памяти, а для увеличения емкости коммутатора по выходам достаточно параллельно дешифраторам подключить дополнительные матрицы памяти. При этом в том и другом случае иет необходнмости вносить изменения в действующий коммутатор.

Формула изобретения

Коммутатор дискретиых сигналов, содержащий регистр коммутируемых данных, К дещифраторов и блок настройки, первые выходы которого соединены с нервыми входами дешифраторов, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены К матриц памяти, управляющие входы которых соединены с выходами соответствующих дешифраторов, информационные входы - с вторыми выходами блока настройки, а выходы соединены поразрядно и нодключены к выходным шинам, при этом третьи выходы блока настройки соединены с входами регистра коммутируемых данных, выходы которых нодключены к вторым входам соответствующих дешифраторов. Источники информации,

принятые во внимание нрн экспертнзе

1.Авторское свидетельство СССР № 478439, кл. Н ОЗК 17/02, 30.11.73.

2.Авторское свидетельство СССР № 482749, кл. G 06F 15/20, 14.01.72.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1976 |

|

SU613401A1 |

| Цифровая электронная вычислительная машина последовательного действия | 1975 |

|

SU532295A1 |

| Устройство для контроля радиоэлектронных объектов | 1978 |

|

SU769554A1 |

| Коммутатор | 1979 |

|

SU873410A1 |

| Однокристальный микропроцессор | 1978 |

|

SU734695A1 |

| Коммутационное устройство | 1989 |

|

SU1672464A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Ассоциативный параллельный процессор | 1980 |

|

SU955078A1 |

| Устройство для управления вводом- ВыВОдОМ | 1979 |

|

SU794631A1 |

| Устройство для сопряжения однородной вычислительной системы | 1979 |

|

SU903848A2 |

Авторы

Даты

1980-04-30—Публикация

1978-10-02—Подача