(54) КОММУТАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ ДАННЫХ ИЗМЕРЕНИЙ | 1993 |

|

RU2079892C1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ СВЕРТОЧНОГО КОДА | 1991 |

|

RU2035124C1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ РЕЗЕРВИРОВАНИЯ РАДИОСТАНЦИЙ | 1990 |

|

RU2018939C1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Устройство для цифровой записи воспроизведения речевой информации | 1990 |

|

SU1771533A3 |

| Адаптивный приемник информации с рассредоточенных объектов | 1991 |

|

SU1807508A1 |

| Коммутирующее устройство | 1980 |

|

SU932615A1 |

| Устройство для записи-считывания звуковых сигналов | 1989 |

|

SU1712964A1 |

Изобретение относится к автоматике и коммутационной технике.

Известны коммутаторы, содержащие дешифраторы и блоки памяти, а также управляющие и информационные шины. 1

К недостаткам из-вестных устройств относится низкая надежность функционирования.

Наиболее близким по технической сущности к данному является коммута- тор, содержащий дешифраторы, первая группа входов первого из которых соединены.с первой группой управляющих шин, а входы второго дешифратора подключены к первой и второй группам управляющих шин, при этом выходы каждого из дешифраторов соединены с управляющими входами соответствующего блока памяти, одноименные информационные входы которых объединены и . подключены к третьей группе управляющих шин, а также информационные входные и выходные шиныГ2,

Недостаток устройства - низкая надежность функционирования.

Целью изобретения является повышение надежности коммутатора.

Указанная цель достигается за счет того, что в коммутатор введен| 1 мультиплексоры и элементы И, выхо,11

каждого из которых соединен с соответствующей выходной Шиной, а входы подключены к одноименным выходам блоков памяти, при этом информационные входы каждого мультиплексора соединены с соответствующей группой информационных входных шин, управляющие входы - со второй группой управляющих шин, а выход подключен к

10 одному из входов второй группы первого дешифратора,

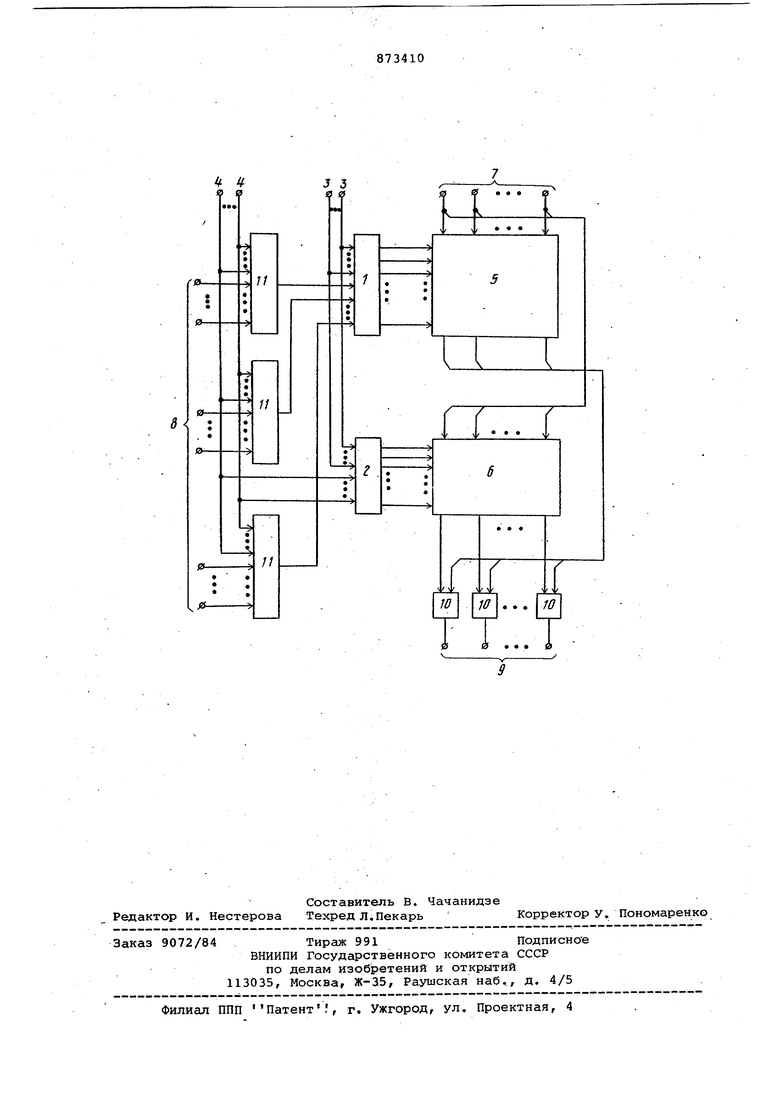

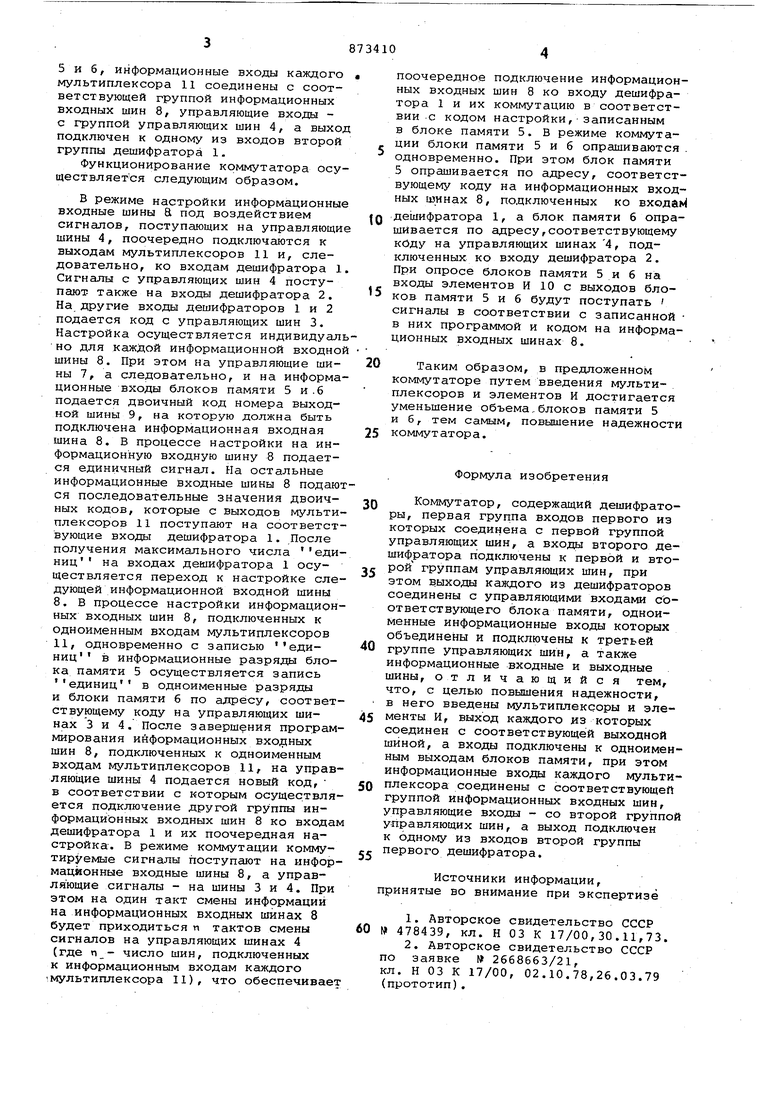

Блок-схема коммутатора представлена- на чертеже.

Она содержит дешифраторы 1 и 2,

15 первая группа входов первого из которых соединена с группой управляющих шин 3, а входы дешифратора 2 подключены к группам управляющих

20 шин 3 и 4, выходы каждого из дешифраторов 1, 2 соединены с управляющими входами соответствующего блока памяти 5,6, одноименные информационные входы которых объединены и подключены

25 к группе управляющих шин 7, информационные- входные 8 и выходные 9 шины, элементы И 10, выход каждого из которых соединен с соответствующей выходной шиной 9, а входы подключены к одноименным выходам блоков памяти

30

5 и б, информационные входы каждого мультиплексора 11 соединены с соответствующей группой информационных входных шин 8, управляющие входы с группой управляющих шин 4, а выход подключен к одному из входов второй группы дешифратора 1.

Функционирование коммутатора осуществляется следующим образом.

В режиме настройки информационные входные шины 81 под воздействием сигналов, поступающих на управляющие шины 4, поочередно подключаются к выходам мультиплексоров 11 и, следовательно, ко входам дешифратора 1. Сигналы с управляющих шин 4 поступают также на входы дешифратора 2. На другие входы дешифраторов 1 и 2 подается код с управляющих шин 3, Настройка осуществляется индивидуально для каждой информационной входной шины 8. При этом на управляющие шины 7, а следовательно, и на информационные входы блоков памяти 5 и.6 подается двоичный код номера выходной шины 9, на которую должна быть подключена информационная входная шина 8. В процессе настройки на информационную входную шину 8 подается единичный сигнал. На остальные информационные входные шины 8 подаются последовательные значения двоичных кодов, которые с выходов мультиплексоров 11 поступсшзт на соответствующие входы дешифратора 1. После получения максимального числа единиц на входах дешифратора 1 осуществляется переход к настройке следующей информационной входной шины 8. В процессе настройки информационных входных шин 8, подключенных к одноименным входам мультиплексоров 11, одновременно с записью единиц в информационные разряды блока памяти 5 осуществляется запись единиц в одноименные разряды и блоки памяти б по адресу, соответствующему коду на управляющих шинах 3 и 4. После завершения программирования ийформационных входных шин 8, подключенных к одноименным входам мультиплексоров 11, на управляющие шины 4 подается новый код, в соответствии с которым осуществляется подключение другой группы информационных входных шин 8 ко входам дешифратора 1 и их поочередная настройка. В режиме коммутации коммутируемые сигналы поступают на информационные входные шины 8, а управляющие сигналы - на шины 3 и 4. При этом на один такт смены информации на информационных входных шинах 8 будет приходиться п тактов смены сигналов на управляющих шинах 4 (где число шин, подключенных к информационным входам каждого мультиплексора II), что обеспечивает

поочередное подключение информационных входных шин 8 ко входу дешифратора 1 и их коммутацию в соответствии с кодом настройки, записанным в блоке памяти 5. В режиме коммутации блоки памяти 5 и б опрашиваются . одновременно. При этом блок памяти 5 опрашивается по адресу, соответствующему коду на информационных входных шннах 8, подключенных ко входа

Q дешифратора 1, а блок памяти б опрашивается по адресу,соответствующему коду на управляющих шинах 4, подключенных ко входу дешифратора 2. При опросе блоков памяти 5 и б на входы элементов И 10 с выходов блоков памяти 5 и б будут поступать сигналы в соответствии с записанной в них программой и кодом на информационных входных шинах 8.

0 Таким образом, в предложенном коммутаторе путем введения мультиплексоров и элементов И достигается уменьшение объема,блоков памяти 5 и 6, тем самым, повышение надежности

5 коммутатора.

Формула изобретения

Коммутатор, содержащий дешифраторы, первая группа входов первого из которых соединена с первой группой управляющих шин, а входы второго дешифратора подключены к первой и второй группам управляющих шин, при этом выхода каждого из дешифраторов соединены с управляющими входами соответствующего блока памяти, одноименные информационные входы которых объединены и подключены к третьей

группе управляющих шин, а также информационные входные и выходные шины, отличающийся тем, что, с целью повышения надежности, в него введены мультиплексоры и злементы И, выход каждого из которых соединен с соответствующей выходной шиной, а входы подключены к одноименным выходам блоков памяти, при этом информационные входы каждого мультиплексора соединены с соответствующей группой информационных входных шин, управляющие входы - со второй группой управляющих шин, а выход подключен к одному из входов второй группы

первого дешифратора.

Источники информации, ринятые во внимание при экспертизе

кл. Н 03 К 17/00, 02.10.78,26.03.79 (прототип).

« Ц3 3

0 0

//

;/

I I I

J,ф Ф

Иг

Авторы

Даты

1981-10-15—Публикация

1979-12-14—Подача