I

Изобретение относится к области вычислительной техники и может быть использовано в различных устройствах автоматики.

Известно последовательное двоично-десяттнное суммирующее устройство, содержащее накопитель, схемы задержки, схему анализа н нуль, схему коррекции результата, элемент ИЛИ, полусумматор-вычитатель, элемент И,генератор одиночных импульсов 1.

Недостатком данного устройства является недостаточное быстродействие.

Наиболее близким к данному изобретенюо техническим решением является устройство, содержащее двоично-десятичные декады, выходы разрядов которых подключены ко входам соответствующих линий задержки, в каждой декаде триггер и элемент И, причем выходы линий задержек каждой декады соединены непосредственно с первой группой элементов И, управляющие входы которых подключены к шине сдвига влево, и через элементы НЕ, за исключением выхода младшего разряда каждой декады, ко второй группе элементов И, . управляющие входы которых подключены к

шине сдвига вправо, выходы первой группы элементов И соединены со входами одноименных двоичных разрядов данной декады, а выходы второй группы элементов И соединены со входами первых трех младших разрядов данной декады, выходы линий задержек млад. ших разрядов всех декад, кроме первой и знaкoвo го разряда, соединены со входами одного и, через злемент НЕ, другого элементов И, входы которых оодсоединены к шине сдвига вправо,

to а выходы 1юдключены соответственно к единичному в нулевому входам триггера данного разряда, единичный выход которого соединен со входалга двух элементов И, вторые входы которых подключены к шине коррекции ре15зультата, а выходы соединены со входами первого и третьего разрядов предыдущей младшей декады, выход линии задержки младшего разряда каждой детсады сумматора подключен через один элемент И, другой вход которой

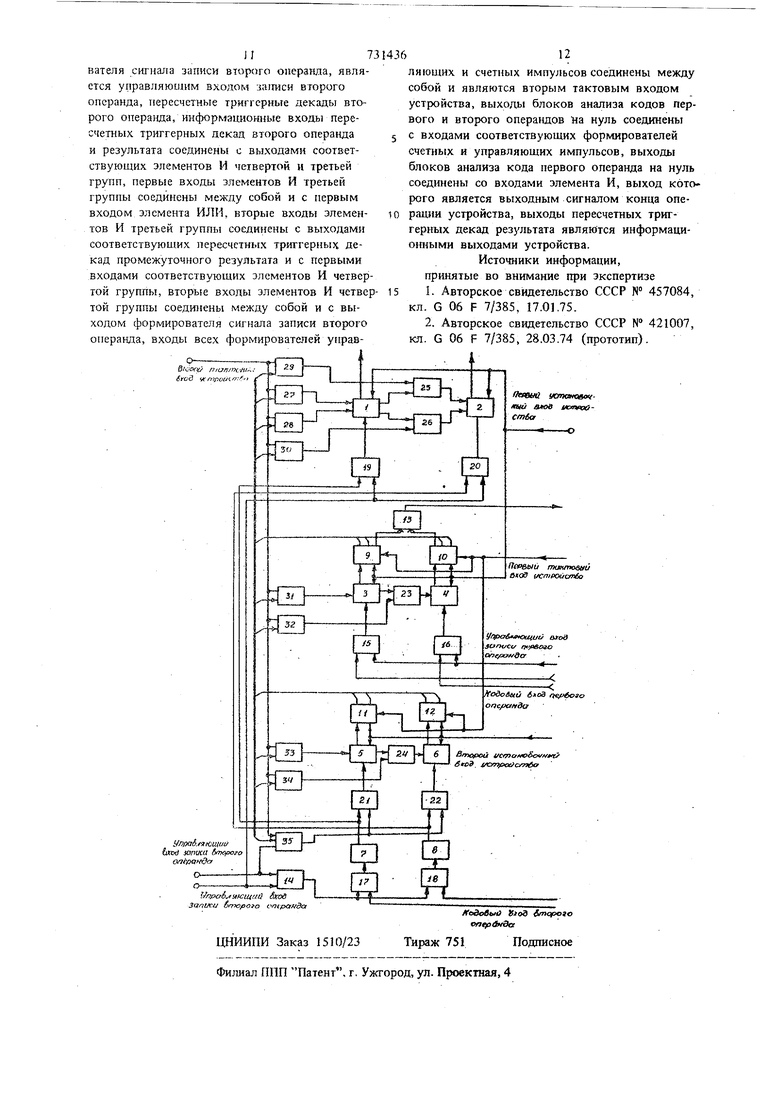

20 соединен с шиной сдвига вправо; элемент НЕ и другой элемент И, управляющий вход которой соединен с шиной переноса младшей декады, к шине переноса собственной декады 2. Однако данное устройство имеет значитель 1ый объем оборудования. Цель изобретения - сокращение оборудования. Поставленная цель достигается тем, что устройство родержит пересчетные триггерные де-. кады операндов и промежуточного результата, две группы блоков анализа операндов на нуль, формирователь управляющих сигналов, первые входы блоков анализа кодов операвдов на нуль соединены между собой и являются первым тактовым входом устройства, вторые входы блоков анализа кодов операвдов на нуль соединены с первыми выходами пересчетных триггерных декад операндов, установочные входы пересчетных триггерных декад первого операнда соединены между собой и с установо ными входами блоков анализа кода первого операнда и являются первым установочным входом устройства, установочные входы пересчегных триггерных декад второго операнда соединены между собой и с установочными входами блоков анализа кода второго операнда и являются вторым установочным входом устройства, счетные входы первых пересчетных триггерных декад операндов, первый и второй входы первой пересчетной триггерной декады результата соединены с выходами соответствующих формирователей счетных импул сов, счетные входы i-ых (i - 2, 3,...) пересчет ных декад операндов через элементы ИЛИ соответственно первой и второй групп соедипены с выходами соответствующих формирова телей сигналов переноса, счетные входы i-ых (i - 2, 3,...) пересчетных триггернь х декад результата через соответствуюише элементы ИЛИ третьей и четвертой групп соединены с соответствующими выходами переноса (i-1)-ы пересчетных триггерных декад результата, вторые входы элементов ИЛИ третьей и четвертой групп соединены с выходами соответствую щих формирователей сигналов переноса, устано вочные входы пересчетных триггерных декад результата соединены между собой и являются третьим установочным входом устройства, информационные входы пересчетных триргерных декад первого операнда и регистра соединены с выходами соответствующих элементов И первой и второй групп, первые входы которых являются соответственно входами первого и второго операндов, вторые входы элементов И первой группы соединены между собой и являются управляющим входом записи первого операнда, вторые входы элемен тов И второй группы соединены между собой и с выходом элемента ИЛИ, первый вход ко торого является управляющим входом записи второго операвда в регистр, а второй вход, 64 соединенный с первым входом формирователя сигнала записи второго операнда, является управ-. ляющим входом записи второго операнда, пересчетные триггерные декады второго опершща, информационные входы пересчетных триггерных декад второго операнда и результата соединены с выходами соответствующих элементов И четвертой и третьей групп, первые входы элементов И третьей труппы соединены между собой И с первым входом элемента ИЛИ, вторьхе входы элементов И третьей группы соединены с выходами соответствующих пересчетных триггерных декад промежуточного результата и с первыми входами соответствующих элементов И четвертой группы, вторые входы элементов И четвертой Труппы соединены между собой и с выходом формирователя сигнала записи второго операнда, входы всех формирователей управляющих и счетных . импульсов соединены между собой и являются вторым тактовым входом устройства, выходы блоков анализа кодов первого и второго операвдов на нуль соединены с входами соответствующих формирователей счетных и управляющих импульсов, выходы блоков анализа кода первого операнда на нуль соединены со входами элемента И, выход которого является выходным сигналом конца операции устройства, выходы пересчетных триггерных декад результата являются информационными выходами устройства, На чертеже показана блок-схема предлагаемого двоично-десятичного арифметического устройства. Устройство содержит пересчетные триггерные декады 1 и 2 результата, пересчетные триггерные декады 3 и 4 первого операнда, пересчетные триггерные декады 5 и 6 второго операнда, пересчетные триггерные декады 7 н 8 промежуточного результата, блоки 9 и 10 анализа кода первого операнда на нуль, блоки 11 и 12 анализа кода второго операнда на нуль, элемент 13 И конца операции, элемент 14 ИЛИ, элементы 15 и 16 И первой группы, элементы 17 н 18 И второй группы, элементы 19 н 20 И третьей группы, элементы 21 н 22 И четвертой группы, элементы 23 ИЛИ; первой группы, элементы 24 ИЛИ Второй группы, элементы 25 ИЛИ третьей группы, элементы 26 ИЛИ четвертой группы, формирователи 27 н 28 счетных импульсов peзyльтaтaJ формирователи 29 и 30 сигна/юв переноса результата, формирователь 31 счетных импульсов первого операнда, формирователь 32 сигналов переноса первого операнда, формирователь 33 счетных импульсов второго . Операвда, формирователь 34 сигналов переноса

второго операнда, формирователь 35 сигналов записи второго операнда.

Первый и второй счетные входы первой пересчетной триггерноч декады 1 результата соединены с выходами формирователей 27

и 28 счетных импульсов, счетные входы последующих i-ых (i - 2, 3,...) пересчетных триггерных декад 2 результата через элементы ИЛИ третьей и четвертой группы 25 и 26 соединены с соответствующими выходами

(i-l)-bix пересчетных триггерных декад 1 результата, вторые входы элементов ИЛИ третьей и четвертой групп 25 и 26 соединены с выходами соотве1ствующих формирователей 29 и 30 сигналов переноса. Кодовые выходы пересчетных триггерных декад 1 и 2 результата являются информационными выходами устройства.

Счетный вход первой пересчетной триггерной декады 3 первого операнда соединен с выходом формирователя 31 счетных импульсов, счетные входы последующих i-ых (i - 2, .3,...) пересчетных триггерных декад 4 первого операнда через элеменгы 23 ИЛИ первой группы соединены с соответствуюищми выходами переноса (i-1)-ых пересчетных триггерных декад 3 первого операнда, вторые входы элементов 23 ИЛИ первой группы соединены с выходами соответствуюпхих формирователей 32 сигналов переноса.

Перв;ые входы блоков 9-12 анализа кодов операндов на нуль, соединены собой и являются первым тактовым входом устройства. Вторые входы блоков 9-12 анализа кодов операндов на нуль согдинены с кодовыми выходами соответствующих нересчетных триггерных декад 3,4 первого и 5, 6 второго операнда. Установочные входы пересчетных триггерных декад 3,4 первого операнда соединены между собой, с установочными входами блоков 9, 10 анализа кодов первого операнда и являются первым установочным входом устройства.

Счетный вход первой пересчетной триггерной декады 5 второго операнда соединен с выходом формирователя 33 счетных импульсов, счетные входы последующих i-ых (i - 2, 3,...) пересчетных триггерных декад 6 второго операнда через элементы 24 ИЛИ второй группы соединены с соответствующими выходами переноса (i-l)-bix пересчетных триггерных декад 5 второго операнда, вторые входы элементов 24 ИЛИ второй группы соединены с выходами соответствующих формирователей 34 сигналов переноса. Установочные входы пересчетных триггерных декад 5 и 6 второго операнда соединены между собой и с установочными входами блоков И и 12 аналпза кодов второго операвда и являются вторым установочным входом устройства.

Информационные входы переспетных триггерных декад 3 и 4 первого операнда 7 и 8 регистра промежуточного результата соединены с выходам соответствуюпдих элементов 15,

16И первой I группы, и 17, 18 второй группы. Первые входы элементов 15, 16 И первой группы представляют собой кодовый вход первого операнда. Первые входы элементов

17и 18 И второй группы представляют собо кодовый вход второго операнда. Вторые входы элементов 15, 16 И первой группы соедщтены между собой и являются управляющим входом записи первого операнда. Вторые входы элементов 17, 18 И второй группы, средшшны тежду собой и с выходом элемента 14 ИЛИ, первый вход которого является управляющим входом записи второго операнда в декады 7 и 8 промеж точного регистра, а второй вход, соедине1шый с первым входом формирователя 35 сигнала записи второго операнда, является управляющем входом записи второго операнда в псресчетные триггерные декады 11 и 12 второго операнда.

14нформащю1ШЬ е входы пересчетных триггерных декад 5, 6 второго операнда и 1,2 результата соединены с выходами соответствующих элементов 21, 22 И четвертой группь и 19, 20 третьей группы. Первые входы элементов 19, 20 И третьей группы соединены между собой и с первым входом элемента 14 ИЛИ, а вторые входы элементов 19, 20 И третьей группы соед1шень1 с выходами соответствующих триггерщ 1Х декад 7, 8 регистра промежуточного результата и с первыми входатуШ элементов 21, 22 И четвертой группы. Вторые входы элементов 21, 22 И четвертой группы соединены между собой и с выходом формирователя 35 -сигнала записи второго операнда.

Первые входы всех формирователей 27-35 управляющих и счетных импульсов соединены между собой и являются вторым тактовым входом устройства. Выходы блоков 9, 10 анализа кодов первого и 11, 12 второго операндов на нуль соединены со входами соответствующих формирователей 27-35 счетных и управляющих импульсов.

Вторые входы формирователей счетных и управляющих сигналов 27 -35 являются управляющими входами, на которые подается признак операции, выполняемой устройством.

Выходы блоков 9, ,10 анализа кодов первого операнда на нуль соединены со входами элемента 13 И, выход которого является выходным сигналом конца операции устройства.

В осдсве работы двоично-десятичного арифметического устройсиаа заложен принцип синхронного счета в декадах операнда и в декаде результата.

3 целях ускорения процессов вычисления, после сложения первой декады сложение кодов следующих старших декад операндов Bg производится синхронной подачей отрицательных и положит€ПЬ}1ых импульсов соответственно на счетные входы соответствующих пересчетных триггерных декад первого операнда и результата. В этом случае младшие декады в работе устройства не участвуют.

При выполнении операции сложения А+В двух двоично-десятичных кодов первого опералда А и второго операнда В, код первого операнда .4 через элементы 15, 16 И первой группы за осится в цересчетные триггерные декады 3, 4 первого операнда.- Для этого на вторые Блоды элементов 5, 16 И с управляющего Ехода подается сигнал разрешения записи первого операнда. Код второго операнда В через элементы П, 18. И второй группы, через декадь 7, 8 регистра промежуточного резyлi т;)тr; и через элементы 19, 20 И третьей группы заносится в пересчетные тритгерные декады I, 2 результата. Разрешением записи второго операнда в регистр результата являетс упразля1ощ11Й сн.гнал, поступающий на соотВ ЛчлЕу Г Ш й вход схемы 14 ИЛИ. На цервый и второй тактовые входы, устройства подаются сдвинутьзс одна относительно другой последоват.ельгюсти тактовых импульсов, причем, частота актовых импульсов определяет быстродействие устройства.

Вьгполнсние сперашй сложения на1шнается с поступлеилсм на вход устройства и далее на третьи входы формирователей 27, 29, 31, 32 признака операции сложения, начало которого совпадает с йервым тактовым импульсом. При неравенстве кода в первой декаде 3 первого операнда нулю (А-)0) с выхода блока 9 анализа кода первого операнд,а на формирователь . 31 поступает разрешающий сигнал, а на формирователь 32 поступает запрешающий сигнал. Одновременно на формирователь 27 с этого же блока 9 поступает разрешающий сигнал, а на формирователь 29 поступает запрешаюший сигнал. Счет производится с кажд.ым вторым тактовым импульсом, при этом, формирователи 3 к 27 подают на счетные входы первых декад 3 первого операнда и 1 результата соотаетствянко импульсы отр15цательного и положительного счета. Счет в, первых декадах прекращается, как только блок 9 в очередном первом такте установит равенство нулю кода в первой декаде первого операнда (). Посл этого опералщя производится с очередной

по старшинству i-ой (i-2, 3,...) декадой 4 первого операнда, в которой код первого операнда не равен нулю (A,:f 0). Соответствующий блок 10 анализа первого операнда на нуль выдает разрешающий сигнал на формирователи 29 и 31 сигналов переноса, формирующие счетные импульсы для i-ых пересчетных триггерных декад 4 первого операнда и 2 результата. Операция сложения заканчивается, когда код в декадах 3,4 первого операнда будет равен нулю. При этом очередным первым тактовым импульсом блоки 9, 10 анализа устанавливают состояние нуля в соответствующих пересчетных декадах 3, 4 первого операнда, после чего с выхода схемы 13 И выдается сигнал окончания операции сложения. В пересчетных триггерных декадах 1, 2 результата находится код результата операции (), который может быть считан с информационного выхода устройства, а также может быть оставлен в пересчетных декадах для выполнения последующих операций.

При выполнении операции вычитания двух двоично-десятичных кодов (В-А) последовательность действий аналогична операции сложения. Отп№(ке заключается в том, что поступающий признак операции вычитания подает разрешение на работу формирователей 28, 30, которые выдают импульсы отрицательного счета,на первую и последующие 1-ые декады

1,2 результата. По окончагши операции в пере. счетных тр1-1ггерных декадах-1, 2 результата находится код разности ().

При выполнении операции умножения двух двоично-десятичных кодов (В х А) предварительно в пересчетные триггерные декады 3, 4 первого операнда 5, б и 7, 8 второго операнда регистра промежуточного результата заносятся соответственно коды первого операнда А и второго операнда В. Пересчетные триггерные декады 1 результата предварительно устанавливаются в нуль. Операция умножения начинается с поступлением на входы формирователей 27-35 признака операции. Операция умножения выполняется как циклически повторяющиеся операции сложения. При неравенстве первой декады первого операнда нулю (А-(0) формирователи 33 и 27 подают на первые пересчетные декады 5 второго операнда и 1 результата импульсы отрицательного и положительного счета соответственно. Производится сложение первой декады второго операнда с первой декадой результата. Далее известным способом с использованием формирователей 24 и 29 производится сложение последующих i-тых декад. Цикл сложения прерывается после того, как блоки 11, 12 анализаторов кода второго операнда зафиксируют нуль во всех декадах 5, 6 второго операнда. В случае, если коды декад первого опера(ща 3, 4 не равны нулю () +... + ), то формирователи 31, 32 в очередном втором такте подаду на соответствующую декаду 3,4 первого операнда импульс отрицательного счета. В этом же такте код второго операнда по сигналу с формирователя 35 повторно заносится из декад 7, 8 регистра через элементы 21, 22 И четвертой группы в пересчетные триггерные декады 5, 6 второго операнда. По мере равен ства нулю младших декад первого операнда в очередном цикле сложения подача импульсов сложения с формирователей 27, 29 начинается соответственно на вторую, третью и т.д. декаду 1, 2 результата. Операция умножения заканчивается при равенстве нулю код в пересчетных триггерных декадах 3,4 первог операнда. Результат умножения в триггерных декадах 1, 2 результата представляет сумму частных произведений ...+ второго операнда на декаду первого операнда При выполнении операции деления двух двоично-десятичных кодов (А:В) последовательность действий аналогична операции умно жения. Отличие заключается в том, что с помощью блоков анализа кода первого операнда 9, 10 определяется самая старщая декада первого операнда, не равная нулю (). После этого подача импульсов на пересчетные триггерные декады первого операнда 3, 4 осуществляется таким образом, чтобы значаща часть кода первого операнда оказывалась всег да на один десятичный порядок больше значащей части кода второго операвда. Подача импульсов положительного счета на декаду результата 1, 2 при делении производится в о ратном порядке, начиная со старшей декады. Операция заканчивается при равенстве нулю кодов во всех декадах 3, 4 первого операнда. Частное от деления при этом находится в пересчетны) декадах 1, 2 результата. Эффективность сокращения оборудования предлагаемого устройства обусловлена тем, что оно реализуется на соответствующим обра зом соединенных пересчетных триггерных декадах и формирователях импульсов и не требует для организации операции сложения и вы читания, умножения и деления дополнительной аппаратуры, комбинационных схем и микропрограммного управления. Формула изобретения Двоично-десятичное арифметическое устройство, содержащее пересчетные триггерные де.кады результата, группы элементов И операн610дов, промежуточного результата, группы элементов ИЛИ операндов и результата, элемент И, элемент ИЛИ, отличающееся тем, что, с целью сокращения оборудования, оно содержит пересчетные триггерные декады операндов и промежуточного результата, две группы блоков анализа операндов на нуль, формирователь управляющих сетналов; первые входы блоков анализа кодов операндов на }гуль соединены между собой н являются первым тактовым входом устройства, вторые входы блоков анализа кодов операндов на нуль соединены с первыми выходами пересчетных триггерных декад операндов, установочные входы пересчетных триггерных декад первого операнда соединены между собой и с установочными входами блоков анализа кода первого операнда и являются первым установочным входом устройства, установочные входы пересчетных триггерных декад второго операнда соединены между собой и с установочными входами блоков анализа кода второго операнда и являются вторым установочным входом устройства, счетные входы первых пересчетных триггерных декад операндов, первый и второй счетные входы первой перссчетной триггерной декады результата соединены с выходами соответствующих формирователей счетньгх импульсов, счетные входы i-ых (i - 2, 3,...) перёсчетных декад операндов через элементы ИЛИ соответственно первой и второй грутш соединены с выходами соответствующих формирователей сигналов переноса, счетные входы i-ых (i - 2, 3,...) пересчетных триггерных декад результата через соответствующие элементы ИЛИ третьей и четвертой групп соединены с соответствующими выходами переноса {1-1)-ых пересчетных триггерных декад .результата, вторые входы элементов ИЛИ третьей и четвертой групп соединены с выходами соответствующих формирователей сигналов переноса, установочные входы пересчетных триггерных декад результата соединены между собой и являются третьим установочным входом устройства, информационные входы пересчетных триггерных декад первого операнда и регистра соединены с выходами соответствующих элементов И первой и второй групп, первые входы которых являются соответственно входами первого и второго операндов, вторые входы элементов И первой группы соединены между собой и являются управляющим входом записи первого операнда, вторые входы элементов И второй группы соединены между собой и с выходом элемента ИЛИ, первый вход которого является управляющим входом «записи второго операнда в регистр, а второй вход, соединенный с первым входом формирователя сигнала записи второго операгша, является управляющим входом ланиси второго операнда, пересчетные триггерные декады второго операнда, информационные входы пересчетных триггерных декад второго операнда и результата соединены с выходами соответствующих элементов И четвертой и третьей групп, первые входы элементов И третьей группы соединены между собой и с первым входом элемента ИЛИ, вторые входы элементов И третьей группь соединены с выходами соответствующих пересчетных триггерных декад промежуточного результата и с первыми входами соответствующих элементов И четвер той группы, вторые входы элементов И четве той группы соедт ены между собой и с выходом формирователя сигнала записи второго операнда, входы всех формирователей управЛЯ10ЩНХ и счетных импульсов соединены между собой и являются вторым тактовым входом устройства, выходы блоков анализа кодов первого и второго операвдов на нуль соединены с входами соответствующих формирователей счетных и управляющих импульсов, выходы блоков анализа кода первого операвда на нуль соединены со входами элемента И, выход которюго является выходным сигналом конца операщш устройства, выходы пересчетных триггерных декад результата являются информациО1шыми выходами устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 457084, кл. G 06 F 7/385, 17.01.75. 2.Авторское свидетельство СССР N 421007, кя. G 06 F 7/385, 28.03.74 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения в двоичной и в двоично-десятичной системе счисления | 1985 |

|

SU1273919A1 |

| Устройство для умножения | 1978 |

|

SU771669A1 |

| Устройство для деления чисел | 1986 |

|

SU1709308A1 |

| Устройство для индикации | 1979 |

|

SU824291A1 |

| Устройство для цифровой индикации | 1975 |

|

SU549820A1 |

| Устройство для сложения в двоичной и двоично-десятичной системах счисления | 1990 |

|

SU1789980A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Измеритель временных интервалов | 1981 |

|

SU1013904A1 |

| Устройство для динамической индикацииВРЕМЕНи СуТОК и КАлЕНдАРя | 1978 |

|

SU805244A2 |

| Пересчетное устройство | 1982 |

|

SU1046935A1 |

Авторы

Даты

1980-04-30—Публикация

1976-05-24—Подача