Изобретение относится к области вычислительной техники и может быть использовано в устройствах обработки информации автоматических систем контроля и управления.

Цель изобретения - повышение быстродействия устройства и расширение области его применения за счет выполнения операции деления непрерывно поступающих операндов.

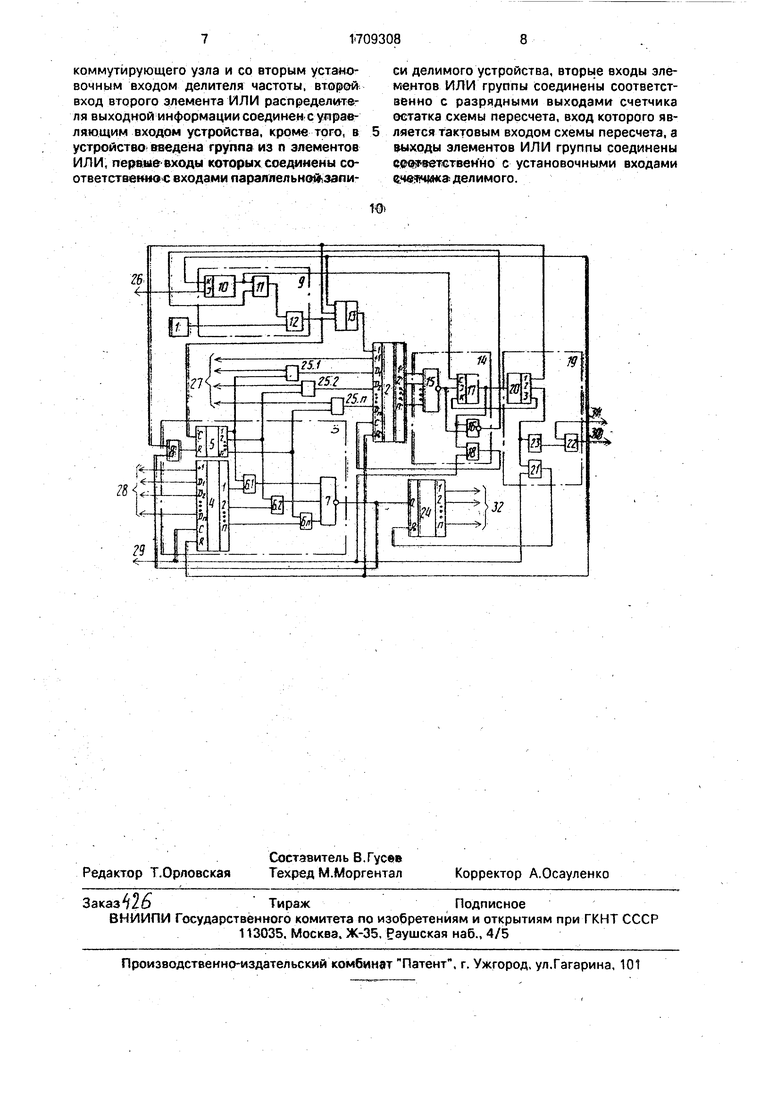

Функциональная схема устройства для деления чисел представлена на чертеже.

Устройство содержит генератор 1 тактовых импульсов, счетчик 2 делимого, схему 3 пересчета, содержащую счетчик 4 делителя, счетчик 5 остатка деления, группу из п элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 6.1-6.п; элемент ИЛИ-НЕ 7 и элемент ИЛИ 8е соответствующими.связями, коммутирующий узел 9, содержащий триггер 10 и первый и второй элементы И 11, 12 с соответствующими связями, делитель 13 частоты, схему 14 переписи, содержащую первый и второй элементы ИЛИ-НЕ 15, 16, триггер 17 и элемент ИЛИ 18 с соответствующими связями, распределитель 19 выходной информации, содержащий элемент 20 задержки, первый и второй элементы ИЛИ 21, 22 и элемент И 23 с соответствующими связями, счетчик 24 результата, группу элементов ИЛИ 25.1-25.п, пусковой вход 26, шину 27 делимого, шину 28 делителя, установочный вход 29, выход

30окончания операции, управляющий вход

31и выходную шину 32 с соответствующими связями.

Устройство работает следующим образом. В исходном состоянии счетчик 2 делимого и счетчики .4. 5 делителя и остатка, а также счетчик 24 результата обнулены, на первом и втором выходах коммутирующего узла 9 сформированы сигналы уровня логического нуля, делитель 13 частоты находится в состоянии, при котором коэффициент деления равен единице.

В счетчик 2 делимого и счетчик 4 делителя производится предварительная iaanncb исходных операндов в виде параллельных чисел путем подачи их на установочныевходы счетчиков или в виде импульсных последовательностей, поступающих на счетные входы соответствующих счетчиков. При нулевом делимом сигнал уровня, логического нуля, сформированный на вУходе элемента ИЛИ-НЕ .16 схемы 14 переписи, поступает на четвертый вход коммутирующего узла 9 и запрещает прохождение импульсов с выхода генератора 1. Деление не производится, результат равен нулю.

.При делимом, не равном нулю, единичный сигнал на четвертом входе коммутирующего узла 9 подготавливает его открытие. а по, сигналу, поступающему на пусковой .вход 26 устройства, триггер 10 коммутирующего узла 9 переключается в единичное состояние, разрешая прохождение с его первого входа на первый выход импульсов генератора и потенциалом логической единицы на Своем втором выходе подготавливая установку в единицу триггера 17 схемы 14 переписи. Импульсы тактовой частоты с первого выхода коммутирующего хузла 9 поступают на счетный вход счетчика 5 остатка схемы 3 пересчете и через делитель 13 частоты, имеющий коэффициент де. ления единицу, на вычитающий вход счетчика 2 делимого. С накоплением в счетчике 5 остатка числа, равного делителю, на

выходах злементов ИСКЛЮЧАЮЩЕЕ ИЛИ б группы формируются сигналы уровня логического нуля, которце поступая на входы элемента ИЛИ-НЕ 7, формируют на его выходе единичный импульс, который поступает на счетный вход счетчика 24 результата, записывая внего еди.ницу. и производит обнуление счетчика 5 остатка схемы 3 пересчета. После обнуления счетчика 2 делимого

0 на выходе элемента ИЛИ-НЕ 15 схемы 14 переписи формируется сигнал уровня логической единицы, который переключает, в единичное состояние триггер 17, сигнал с прямого выхода которого через элемент

5 ИЛИ 18 осуществляет запись остатка деления, поступающего с разрядных выходов счетчика 5 остатка схемы 3 пересчета через элементы ИЛИ 25 группы на установочные , входы счетчика 2 делимого. Целая часть частного снимается с выходных информационных шин 31 устройства, а сигнал с выхода триггера 17 схемы 14 переписи поступает на вход элемента 20 задержки распределителя 19 и с его первого выхода поступает на установочный вход делителя 13 частоты, устанавливая его в состояние, при котором его коэффициент деления становится равным десяти, на вход обнуления счетчика 5 остатка схемы 3 пересчета. Сигнал со второго

0 выхода элемента 20 задержки поступает на вход установки в ноль счетчика 24 результата, а сигнал с третьего выхода элемента 20 задержки поступает на вход установки в ноль триггера 17 схемы 14 переписи. Далее цикл счета повторяется, но поскольку тактовая частота на вычитающий вход счетчика 2 делимого поступает поделенная на десять, то фактически в устройстве производится деление остатка, умноженного на десять. В случае когда остаток очередного цикла становится равным нулю, сигнал с выхода элемента ИЛИ-НЕ 6 переписывает нулевую информацию в счетчик 2 делимого, подтверждая его состояние, а на выходе

5 элемента ИЛИ 22 распределителя 19 по сигналу со второго выхода элемента 20 задержки формируется сигнал Окончание операции, который обнуляет счетчик 2 делимого, счетчик 4 делителя, триггер 10 коммутирующего узла 9, а делитель 13 частоты переводит в состояние, при котором коэффициент его деления становится равным единице.

Процесс деления в устройстве можно

5 остановить на любом цикле с помощью внешнего сигнала, поступающего с управляющего входа 31 устройства на вто)ой вход элемента ИЛИ 22. на выходе которого формируется сигнал Окончание.операции. Быстродействие устройства увеличивается

за счет возможности увеличения частоты генератора тактовых импульсов, величина которой в прототипе ограничивается временем задержки установки пересчетной декады, а установка устройства сигналом окончания операции в состояние готовности позволяет производить операцию деления над непрерывно поступающими операндами с помощью подачи сигналов на его установочный и пусковой входы.

Формула изобретения Устройство для деления чисел, содержащее генератор тактовых импульсов, счетчик делимого, схему пересчета, коммутирующий узел, делитель частоты, схему переписи, распределитель выходной информации и счетчик результата, причем выход генератора тактовых импульсов соединен с первым входом коммутирующего узла, второй вход KOTOpord соединен с пусковым входом устройства, информационный вход схемы переписи соединен с выходо,м счетчика делимого, первый выход коммутирующего узла соединен с тактовым входом схемы пересчета и с информационным входом делителя частоты, выход которого соединен с вычитающим входом счетчика делимого, вход сложения которого соединен с входом последовательной записи делимого устройства, вход сложения схемы пересчета соединен с входом последовательной записи делителя устроит ства, отличающееся тем, что. с целью повышения быстродействия устройства, а также расширения области его применения за счет выполнения операции деления непрерывно поступающих операндов, коммутирующий узел устройства выполнен в виде триггера и первого и второго элементов И, причем выход триггера соединен со вторым выходом коммутирующего узла и с первым входом первого элемента И, выход которого соединен с первым входом второго элемента И, второй вход которого является первым входом коммутирующего узла, а выход первым выходом коммутирующего узла, вход установки в единицу триггера соединен со вторым входом коммутирующего узла, третий вход которого соединен с входом установки в ноль триггера, а четвертый вход соединен со вторым входом первого элемента И. схема пересчета устройства содержит п-разрядный счетчик делителя, празрядный счетчик остатка, группу из п-элементо8 ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент ИЛИ-НЕ и элемент ИЛИ, причем разрядне выходы счетчика остатка соединены соответственное первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы, йторые

входы которых соединены соответственно с разрядными выходами счетчика делителя, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы соединены с соответствующими вхо5 дамиэлемента ИЛИ-НЕ, выход которого соединен с первым входом элемента ИЛИ, выход которого соединен с входом установки в ноль счетчика остатка, установочные входы счетчи.ка делителя соединены с входами параллельной записи делителя устройства, а вход разрешения записи счетчика делителя Соединен с установочным входом устройства, схема переписи ус тройства содержит первый и второй

15 элементы ИЛИ-НЕ, триггер и.элементИЛИ,

причем входы первого элемента

являются информационным входом схемы

переписи, выход первого элемента ИЛИ- НЕ соединен с входом установки в единицу

0 триггера и с первым входом второго элемента ИЛИ-НЕ, второй вход которого соединен с выходом триггера и с первым входом элемента ИЛИ, второй вход которого соединен с установочным входом устройства, а выход

5 элемента ИЛИ соединен с входом разрешения записи в счетчик делимого, синхровход триггера схемы переписи соединен со вторым выходом коммутирующего узла, четвертый вход которого соединен с выходом

0 второго элемента ИЛИ-НЕ схемы переписи, распределитель информации устройства содержит элемент задержки, первый и второй элементы ИЛИ и элемент И, причем вход элемента задержки распределителя выходной информации соединен с выходом триггера схемы переписи, первый выход элемента задержки распределителя выходной информации

соединен с первым управляющим входом делителя частоты и вторым-входом элемента ИЛИ схемы пересчета, второй выход элемента задержки распределителя выходной информации соединен с первыми входами элемента И и первого элемента ,И Л И,

5 второйвход которого соединен с установочным входом устройства, а выход первого элемента ИЛИ распределителя выходной информации соединен с входом установки в ноль счетчика результата, второй вход элемента И распределителя выходной информации соединен с входом установки в единицу триггера схемы переписи, вход установки в ноль которого соединен с третьим выходом задержки распределителя выходной информации, выход элемента И которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с выходом окончания операции устройства и с входами установки в ноль

счетчиков делимого, делителя, триггера

коммутирующего узла и со вторым установочным входом делителя частоты. второ( вход второго элемента ИЛИ распределителя выходной информации соединена yinpaeляющим входом устройства, кроме трго, в устройство введена группа из п элементов ИЛИ, первые входы которых соединены соответственное входами лараялельнойнзаписи делимого устройства, вторые входы элементов ИЛИ группы соединены соответственно с разрядными выходами счетчика остатка схемы пересчета, вход которого является тактовым входом схемы пересчета, а выходы элементов ИЛИ группы соединены С №гввтственйо с установочными входами е 4в; чкнса делимого.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1980 |

|

SU955053A1 |

| Устройство для деления кодов "золотой" пропорции | 1986 |

|

SU1361544A1 |

| Арифметическое устройство | 1985 |

|

SU1550510A1 |

| Устройство для умножения и деленияпОСлЕдОВАТЕльНО-пАРАллЕльНОгОдЕйСТВия | 1979 |

|

SU817703A1 |

| Устройство для обработки телединамограмм глубинно-насосных скважин | 1988 |

|

SU1671843A1 |

| Устройство для деления | 1983 |

|

SU1166100A1 |

| Устройство для деления последовательных чисел | 1987 |

|

SU1462298A1 |

| УСТРОЙСТВО ДЛЯ НАХОЖДЕНИЯ ОТНОШЕНИЯ ДВУХчислоимпульсных кодов | 1972 |

|

SU436352A1 |

| Устройство для деления чисел | 1985 |

|

SU1552180A1 |

| Делительное устройство | 1982 |

|

SU1104508A1 |

Изобретение относится к области вычислительной техники и может быть использовано в устройствах обработки информации автоматических систем контроля и управления. Цель изобретения - повышение быстродействия устройства и расширение области по применениюза счет выполнения операции деления непрерывно поступающих операндов. Устройство содержит генератор 1 тактовых импульсов, счетчик 2 делимого, схему 3 пересчета, содержащую учетчик 4 делитеяя, счетчик 5 остатка деления, группу из п элементов Исключающее ИЛИ 6, элемент ИЛИ-НЕ 7 и элемент ИЛИ 8 с соответствующими связями, коммутирующий узел 9, содержащий• /триггер 10, элементы И 11, 12 с соответствующими связями, делитель 13 частоты, схему 14 переписи, содержащую элементы ИЛИ- НЕ 15, 16, триггэр 17 и элемент ИЛИ Г8 с соответствующими связями, ра'спредели- тель 19 выходной информации, содержащий элемент 20 задержки, элементы ИЛИ 21, 22 и элемент И 23 с соответствующими связями, счетчик 24 результата, группу элементов ИЛИ 25. Поставленная цель достигается тем, что процесс деления в устройстве можно остановить в любом цикле с помощью внешнего сигнала, поступающего с управляющего входа 31 на второй вход элемента ИЛИ 22, на выходе которого формирует<:я сигнал "Окончание операции". Быстродействие устройства увеличивается за счет возможности увеличения частоты генератора тактовых им^пульсов, величина которой ограничивается временем задержки установки пересчетной декады, а установка устройства сигналом "Окончание операции" в состояние готовности позволяет производить операцию деления над непрерывно по- стулающими операндам'и с помощью подачи сигналов на его установочный и пусковой входы. 1 ил.VJО ЮСА>&Ооо

| Авторское свидетельство СССР fvfe 1198515, кл | |||

| G 0:6 F 7/52, 1980.Авторское свидетельство СССР № 474005, кл.С 06 F 60, 1973. |

Авторы

Даты

1992-01-30—Публикация

1986-03-28—Подача