С«Л М14:1Jp f

Фиг.1

Изобретение относится к автоматике и вычислительной технике.

Известно устройство для сложения в двоичной и в двоично-десятичной системах счисления, содержащее два триггера знаков, узел сравнения знаков, три элемента И, элемент НЕ, два дешифратора.

t Недостатками известного устройства являются низкое быстродействие, и узкая облаете ЬрШенения.

Наиболее близким по технической сущности к заявляемому является устройство для сложения в двоичной и в двоично-десятичной системах счисления, содержащее два триггера знака, узел сравнения знаков, две .группы фрагментов, каждая из которых содержит фрагменты для своего операнда, три элемента И, три элемента НЕ, три элемента ИЛИ, каждый фрагмент содержит дешифратор нуля, реверсивный счетчик, элемент НЕ и элемент И.

Недостатком известного устройства является узкая область применения, так как известное устройство не позволяет производить сложение в произвольном двойчнр-десятичном коде, а также низкое быстродействие.

Целью изобретения является расширение области применения за счет возможно- сти использования более, широкого круга двоично-десятичных кодов и повышение быстродействия.

Поставленная цель достигается тем, что в устройство для сложения в двоичной и в двоично-десятичной системах счисления, содержащее первую и вторую группы блоков преобразования декад, блок формирования знака, первый и второй элементы НЕ,. первую группу элементов И и группу элементов ИЛИ, причем выходы элементов И первой группы соединены соответственно с первыми входами элементов ИЛИ группы, введены первый и второй регистры операндов, первый и второй накапливающие сумматоры, алгебраический сумматор, вторая группа элементов И, регистр кода, группа из К -1 блоков формирования весов декад (К - количество декад входных чисел) и группа из К блоков формирования декад, причем информационные входы первого и второго регистров операндов соединены соответственно с первым и вторым информационными входами устройства, с первым синхровходом которого соединены входы разрешения записи первого и второго регистров операндов, разрядные выходы первого регистра операнда соединены подекадно с первыми информационными входами соответствующих блоков преобразования декад первой группы, разрядные выходы

второго регистра операнда соединены подекадно с первыми информационными входами соответствующих блоков преобразования декад второй группы, а знаковые

разрядные выходы первого и второго регистров операндов соединены соответственно с первым и вторым знаковыми входами алгебраического сумматора, и с первым и вторым знаковыми входами блока формирования знака, информационный вход регистра кода соединен с установочным входом устройства, второй синхровход которого соединен с входом разрешения записи регистра кода, выход которого соединен с

5 первым входом первого блока формирования декад, с вторыми информационными входами первых блоков преобразования декад первой и второй групп и с первым входом первого блока формирования декад

0 группы, выход 1-го б л о к а фррми р о ва н и я весов декад группы (I 1, К - 2) соединен с входом 1 + 1-го блока формирования весов декад группы, со вторыми информационными входами i + 1-го блоков преобразования

5 декад первой и второй групп и с первым входом i + 1-го блока формирования декад группы, выход К - 1-го блока формирования весов декад группы соединен с вторыми информационными входами К-х блоков преоб0 разования декад первой и второй групп и с первым входом блока формирования декад группы, первый вход управления режимом работы устройства соединен с первыми управляющими входами блоков преобразова5 ния декад первой и второй групп и с входом первого элемента НЕ, выход которого соединен с вторыми управляющими входами блоков преобразования декад первой и второй групп, выходы блоков преобразования

0 декад первой группы соединены с входом первого накапливающего сумматора, выход которого соединен с первым информационным входом алгебраичного сумматора, и с первым информационным входом блока

5 формирования знака, выходы блоков преобразования декад второй группы соединены с входом второго накапливающего сумматора, выход которого соединен с вторым информационным входом алгебраического

0 сумматора и со вторым информационным входом блока формирования знака, выход которого соединен со знаковым выходом устройства, разрядные выходы алгебраического сумматора соединены соответственно

5 с первыми входами элементов И первой труппы и со вторым входом К-ro блока формирования декад группы, первый аыход -го блока формирования декад группы, 0 2. К), соединен с вторым входом j - 1-го блока формирования декад группы, вторые входы

блоков формирования декад группы соединены с первыми входами элементов И второй группы, второй управляющий вход устройства соединен с вторыми входами элементов И первой группы и с входом вто- рого элемента НЕ, выход которого соединен с вторыми входами элементов И второй группы, выходы которых соединены с вторыми входами элементов ИЛИ группы, выходы которых являются информационными выходами устройства.

Кроме того, блок преобразования декад содержит первую, вторую, третью, четвертую, пятую to шестую группы элементов И, группу элементов ИЛИ и сумматор, причем первые входы элементов И первой, второй, третьей, четвертой и пятой групп соединены соответственно с первым информационным входом блока преобразования декад, второй информационный вход которого соеди- нен с вторыми входами, элементов И первой, второй, третьей и четвертой групп, выходы которых соединены с входами первой, второй, третьей и четвертой групп сумматора, разрядные выходы которого соединены соответственно с первыми входами элементов И шестой группы, первый управляющий вход блока преобразования декад соединен с вторыми входами элементов И пятой группы, выходы которых соеди- нены с первыми входами элементов ИЛИ группы, второй управляющий вход блока преобразования декад соединен с вторыми входами элементов И шестой группы, выходы которых соединены с вторыми входами элементов ИЛИ группы, выходы которых являются выходом блока преобразования декады.

Кроме того, блок формирования декады содержит четыре узла формирования разрядов декады, каждый из которых содержит схему сравнения, вычитатель и мультиплексор, причем входы первой группы схемы сравнения и вычитателя соединены с входа- ми первой группы узла формирования разряда декады, входы второй группы схемы сравнения и вычитателя соединены с ин- формационными входами первой группы мультиплексора, и с входами второй группы узла формирования разряда декады, выход схемы сравнения соединен с управляющим входом мультиплексора, информационные входы второй группы которого соединены соответственное разрядными выходами вы- читателя, а выход мультиплексора является первым выходом узла формирования разряда декады, вторым выходом которого является выход схемы сравнения, входы первой группы первого, второго, третьего и четвертого узлов формирования разрядов декады соединены с первым входом блока формирования декады, второй вход которого соединен с входами второй группы четвертого узла формирования разряда декады, первый выход первого узла формирования разряда декады является первым выходом блока формирования декады, вторые выходы первого, второго, третьего и четвертого узлов формирования разряда декады являются вторым выходом блока формирования декады, первый выход 1-го узла формирования разряда декады (i 2- 4) соединен с вторым входом I - 1-го узла формирования разряда декады.

Кроме того, блок формирования знака содержит схему сравнения, первый и второй элементы И, первый и второй элементы ИЛИ, первый и второй элементы НЕ и первый и второй элементы ИЛИ-НЕ, причем первый и второй информационные входы блока формирования знака соединены соответственно с входами первой и второй групп схемы сравнения, выходы Больше и Меньше которой соединены соответственно с первыми входами первого и второго элементов ИЛИ, вторые входы которых соединены с выходом Равно схемы сравнения, а выходы первого и второго элементов ИЛИ соединены соответственно с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно со вторым и первым знаковыми входами блока формирования знака и с входами второго и первого элементов НЕ, выходы которого соединены соответственно с третьими входами второго и первого элементов И, выходы которого соединены соответственно с первым и вторым входами второго элемента ИЛИ-НЕ, третий вход которого соединен с выходом первого элемента ИЛИ-НЕ, первый и второй входы которого соединены соответственно с первым и вторым знаковыми входами блока формирования знака, выход которого соединен с выходом элемента второго ИЛИ-НЕ.

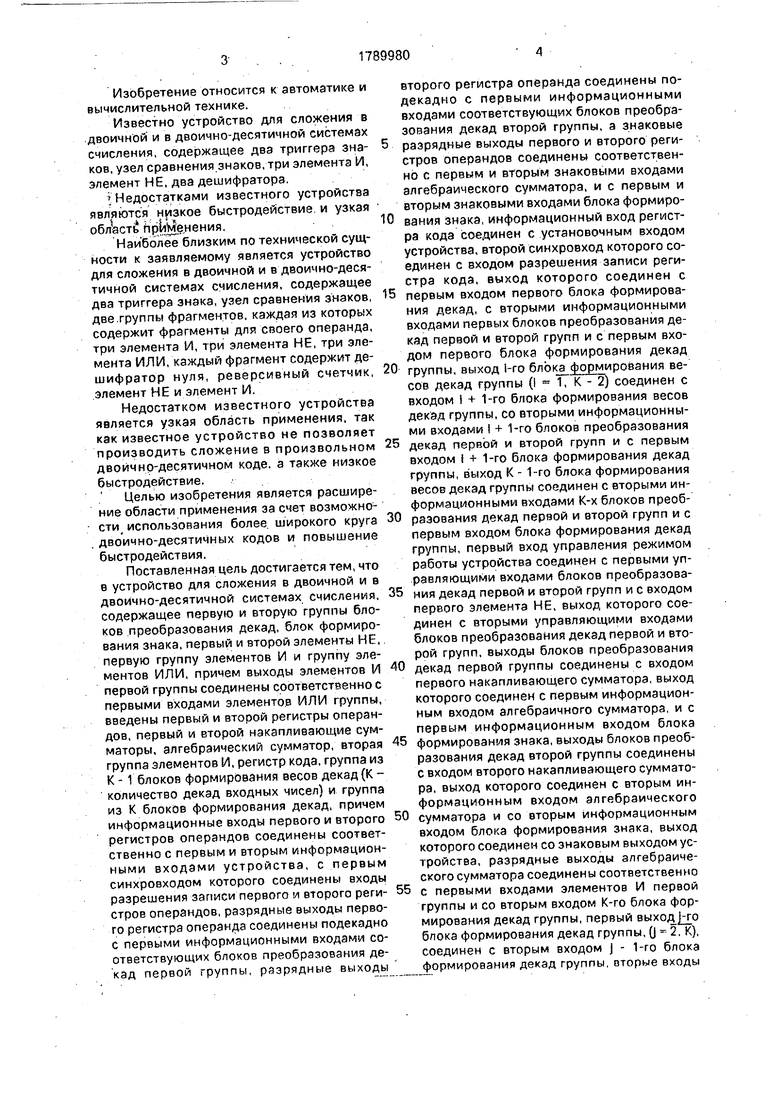

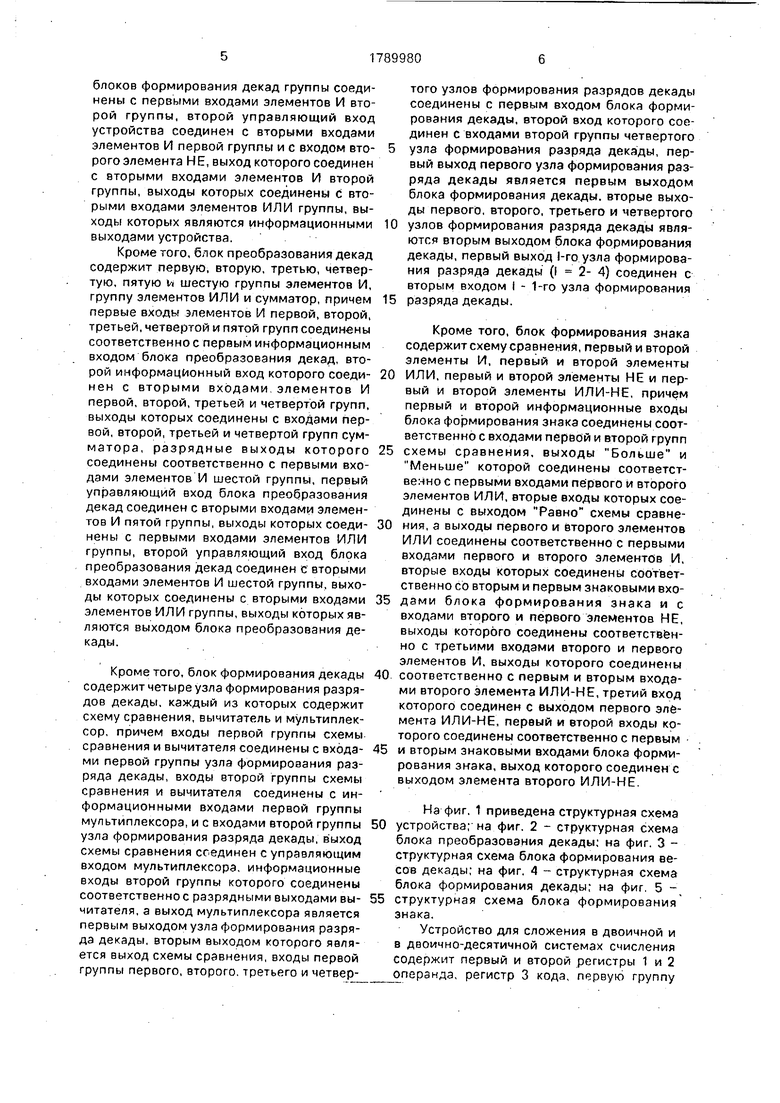

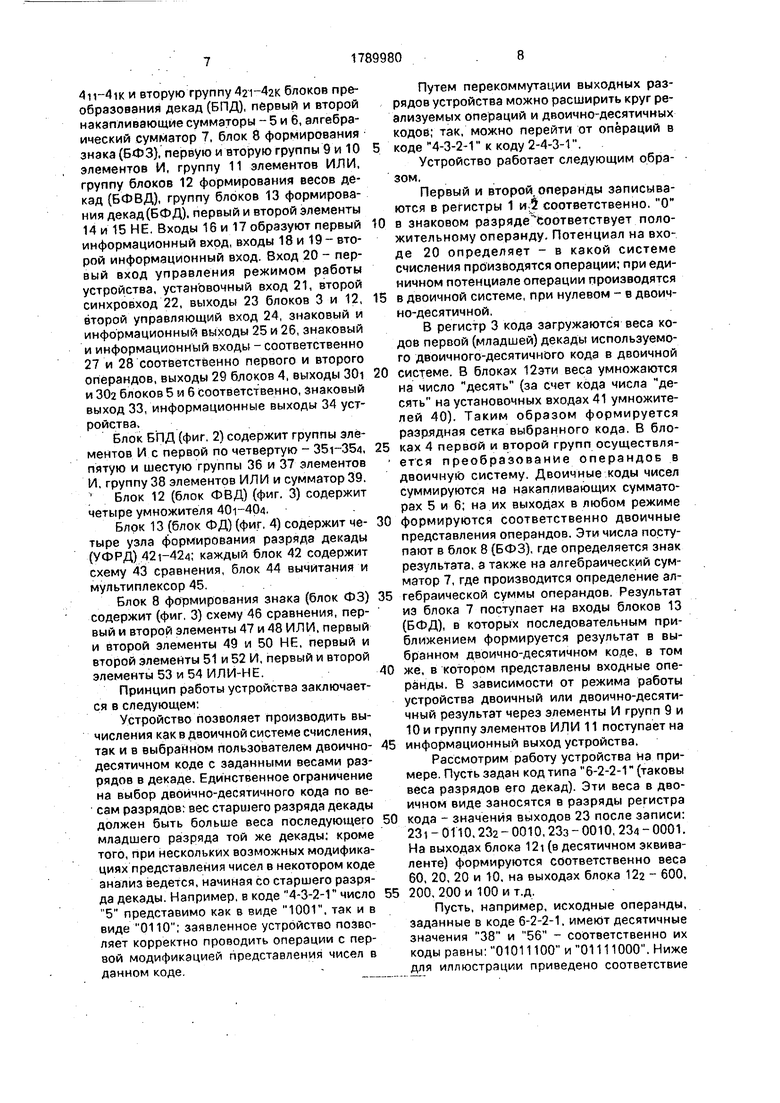

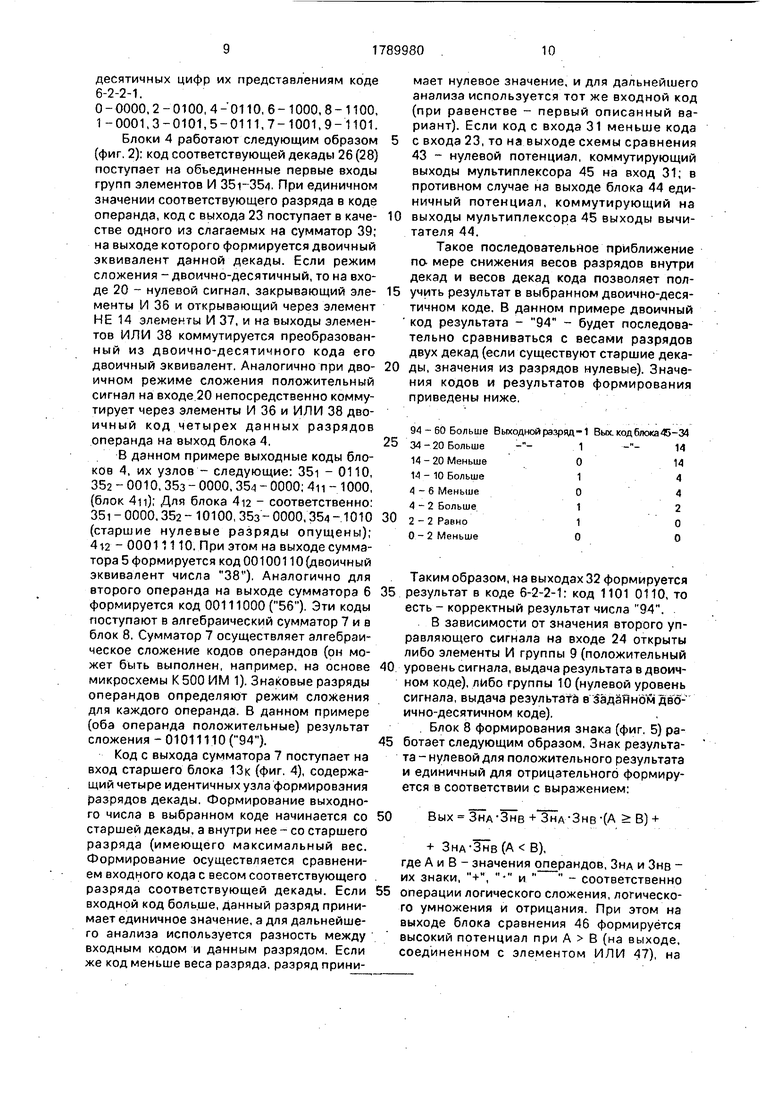

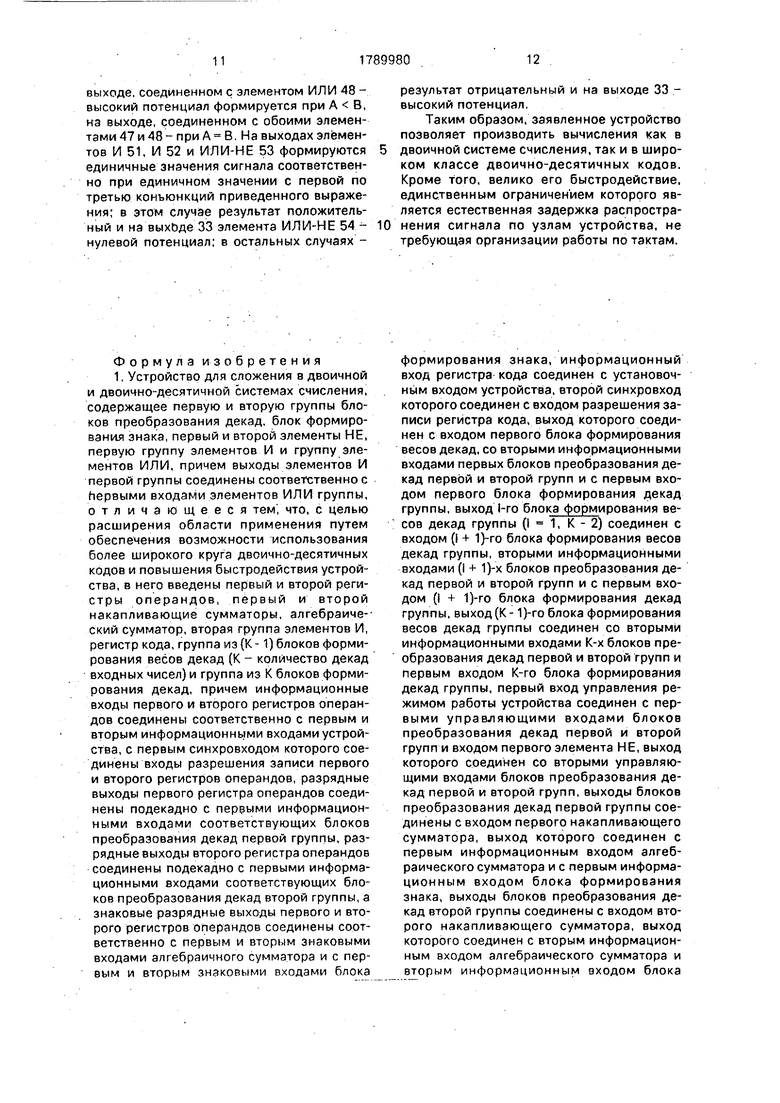

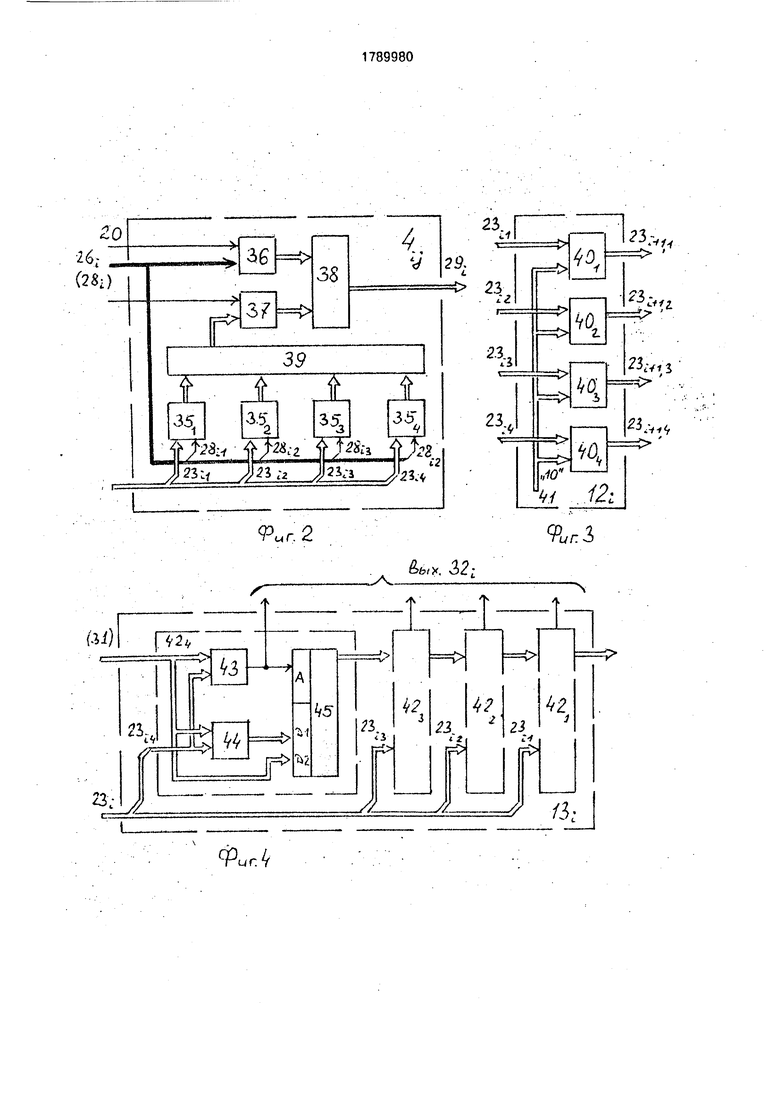

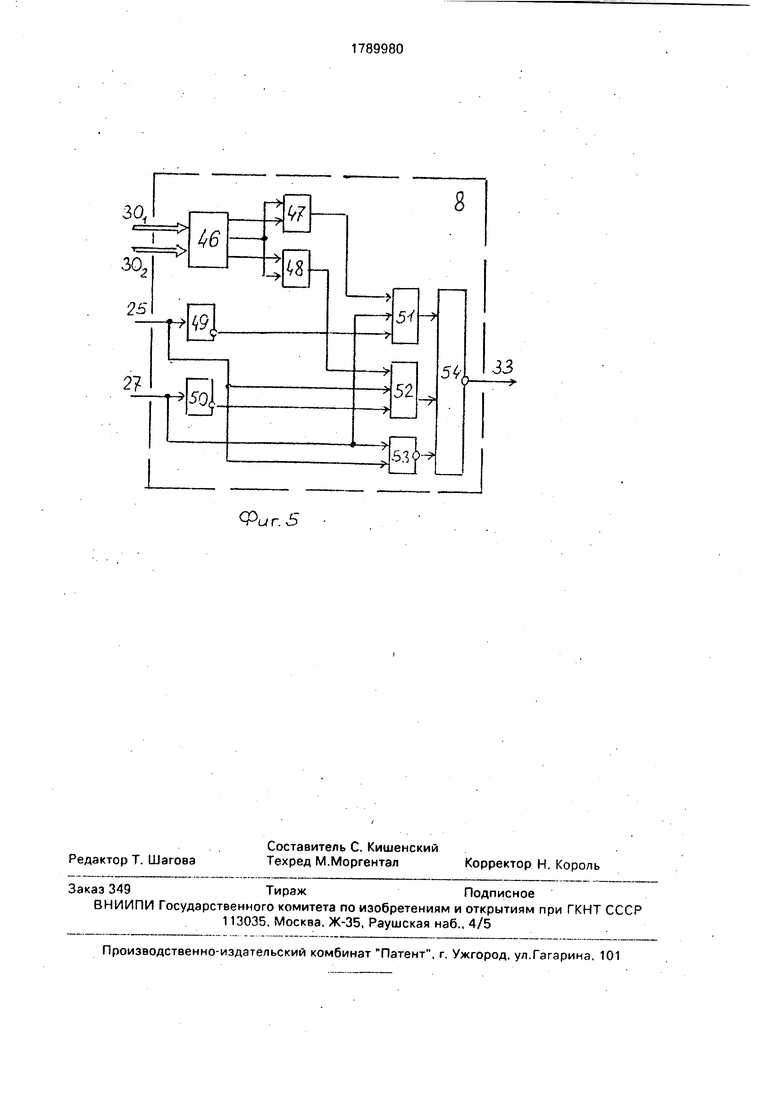

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - структурная схема блока преобразования декады: на фиг. 3 - структурная схема блока формирования весов декады; на фиг. 4 - структурная схема блока формирования декады; на фиг. 5 - структурная схема блока формирования знака.

Устройство для сложения в двоичной и в двоично-десятичной системах счисления содержит первый и второй регистры 1 и 2 операнда, регистр 3 кода, первую группу

4ц-4IK и вторую группу 421-42K блоков преобразования декад (БПД), первый и второй накапливающие сумматоры - 5 и 6, алгебраический сумматор 7, блок 8 формирования знака (БФЗ), первую и вторую группы 9 и 10 элементов И, группу 11 элементов ИЛИ, группу блоков 12 формирования весов декад (БФВД), группу блоков 13 формирования декад (БФД), первый и второй элементы 14 и 15 НЕ. Входы 16 и 17 образуют первый информационный вход, входы 18 и 19 - второй информационный вход. Вход 20 - первый вход управления режимом работы устройства, установочный вход 21, второй синхровход 22, выходы 23 блоков 3 и 12, второй управляющий вход 24, знаковый и информационный выходы 25 и 26, знаковый и информационный входы - соответственно 27 и 28 соответственно первого и второго операндов, выходы 29 блоков 4, выходы 30i и ЗОа блоков 5 и 6 соответственно, знаковый выход 33, информационные выходы 34 устройства.

Блок БПД (фиг, 2) содержит группы элементов И с первой по четвертую - , пятую и шестую группы 36 и 37 элементов И, группу 38 элементов ИЛИ и сумматор 39. Блок 12 (блок ОВД) (фиг. 3) содержит четыре умножителя 40i-4Q4.

Блок 13 (блок ФД) (фиг, 4) содержит четыре узла формирования разряда декады (УФРД) 421-424; каждый блок 42 содержит схему 43 сравнения, блок 44 вычитания и мультиплексор 45..

Блок 8 формирования знака (блок ФЗ) содержит (фиг. 3) схему 46 сравнения, первый и второй элементы 47 и 48 ИЛИ, первый и второй элементы 49 и 50 НЕ, первый и второй элементы 51 и 52 И, первый и второй элементы 53 и 54 ИЛИ-НЕ.

Принцип работы устройства заключается в следующем:

Устройство позволяет производить вычисления как в двоичной системе счисления, так и в выбранном пользователем двоично- десятичном коде с заданными весами разрядов в декаде. Единственное ограничение на выбор двоично-десятичного кода по весам разрядов: вес старшего разряда декады должен быть больше веса последующего младшего разряда той же декады; кроме того, при нескольких возможных модификациях представления чисел в некотором коде анализ ведется, начиная со старшего разряда декады. Например, в коде 4-3-2-1 число 5 представимо как в виде 1001. так и в виде заявленное устройство позволяет корректно проводить операции с первой модификацией представления чисел в данном коде.

Путем перекоммутации выходных разрядов устройства можно расширить круг реализуемых операций и двоично-десятичных кодов; так, можно перейти от операций в

коде 4-3-2-1 к коду 2-4-3-1.

Устройство работает следующим образом.

Первый и второй операнды записываются в регистры 1 иЗ соответственно. 0й

0 в знаковом разряде боответствует положительному операнду. Потенциал на входе 20 определяет - в какой системе счисления производятся операции; при единичном потенциале операции производятся

5 в двоичной системе, при нулевом - в двоично-десятичной,

В регистр 3 кода загружаются веса кодов первой (младшей) декады используемого двоичного-десятичного кода в двоичной

0 системе. В блоках 12эти веса умножаются на число десять (за Счет кода числа десять на установочных входах 41 умножителей 40). Таким образом формируется разрядная сетка выбранного кода, В бло5 ках 4 первой и второй групп осуществля- ется преобразование операндов в двоичнуй систему. Двоичные коды чисел суммируются на накапливающих сумматорах 5 и 6; на их выходах в любом режиме

0 формируются соответственно двоичные представления операндов. Эти числа поступают в блок 8 (БФЗ), где определяется знак результата, а также на алгебраический сумматор 7, где производится определение ал5 гебраической суммы операндов. Результат из блока 7 поступает на входы блоков 13 (БФД), в которых последовательным приближением формируется результат в выбранном двоично-десятичном коде, в том

0 же, в котором представлены входные операнды. В зависимости от режима работы устройства двоичный или двоично-десятичный результат через элементы И групп 9 и 10 и группу элементов ИЛИ 11 поступает на

5 информационный выход устройства.

Рассмотрим работу устройства на примере. Пусть задан код типа 6-2-2-1 (таковы веса разрядов его декад). Эти веса в двоичном виде заносятся в разряды регистра

0 кода - значения выходов 23 после записи: 231-0110,232-0010,23з-0010,234-0001. На выходах блока 12i (в десятичном эквиваленте) формируются соответственно веса 60, 20, 20 и 10, на выходах блока 122 - 600,

5 200, 200 и 100 и т.д.

Пусть, например, исходные операнды, заданные в коде 6-2-2-1, имеют десятичные значения 38 и 56 - соответственно их коды равны: 01011100 и 01111000. Ниже для иллюстрации приведено соответствие

десятичных цифр их представлениям коде

6-2-2-1.

0-0000,2-0100, 4-0110, 6-1000,8-1100,

1-0001,3-0101,5-0111,7-1001,9-1101.

Блоки 4 работают следующим образом (фиг. 2): код соответствующей декады 26 (28) поступает на объединенные первые входы групп элементов И 351-354. При единичном значении соответствующего разряда в коде операнда, код с выхода 23 поступает в качестве одного из слагаемых на сумматор 39; на выходе которого формируется двоичный эквивалент данной декады. Если режим сложения -двоично-десятичный, то на входе 20 - нулевой сигнал, закрывающий элементы И 36 и открывающий через элемент НЕ 14 элементы И 37, и на выходы элементов ИЛИ 38 коммутируется преобразованный из двоично-десятичного кода его двоичный эквивалент. Аналогично при двоичном режиме сложения положительный сигнал на входе 20 непосредственно коммутирует через элементы И 36 и ИЛИ 38 двоичный код четырех данных разрядов операнда на выход блока 4,

В данном примере выходные коды блоков 4, их узлов - следующие: 35i - 0110, 352 - 0010, 35з - 0000, 354 - 0000; 4ц - 1000, (блок 4ц); Для блока 4i2 - соответственно; 35i - 0000.352 - 10100, 35з- 0000,354 -1010 (старшие нулевые разряды опущены); 412 - 00011110. При этом на выходе сумматора 5 формируется код 00100110(двоичный эквивалент числа 38). Аналогично для второго операнда на выходе сумматора 6 формируется код 00111000 (56). Эти коды поступают в алгебраический сумматор 7 и в блок 8. Сумматор 7 осуществляет алгебраическое сложение кодов операндов (он может быть выполнен, например, на основе микросхемы К 500 ИМ 1). Знаковые разряды операндов определяют режим сложения для каждого операнда. В данном примере (оба операнда положительные) результат сложения -01011110 (94).

Код с выхода сумматора 7 поступает на вход старшего блока 13к (фиг. 4), содержащий четыре идентичных узла формирования разрядов декады. Формирование выходного числа в выбранном коде начинается со старшей декады, а внутри нее - со старшего разряда (имеющего максимальный вес. Формирование осуществляется сравнением входного кода с весом соответствующего разряда соответствующей декады. Если входной код больше, Данный разряд принимает единичное значение, а для дальнейшего анализа используется разность между входным кодом и данным разрядом. Если же код меньше веса разряда, разряд принимает нулевое значение, и для дальнейшего анализа используется тот же входной код (при равенстве - первый описанный вариант). Если код с входа 31 меньше кода

5 с входа 23, то на выходе схемы сравнения 43 - нулевой потенциал, коммутирующий выходы мультиплексора 45 на вход 31; в противном случае на выходе блока 44 единичный потенциал, коммутирующий на

0 выходы мультиплексора 45 выходы вычи- тателя 44.

Такое последовательное приближение па мере снижения весов разрядов внутри декад и весов декад кода позволяет пол5 учить результат в выбранном двоично-десятичном коде. В данном примере двоичный код результата - 94 - будет последовательно сравниваться с весами разрядов двух декад (если существуют старшие дека0 ды, значения из разрядов нулевые). Значения кодов и результатов формирования приведены ниже.

94 - 60 Больше Выходнойрэзрад-1 Вых. код блока 45-34

5 34-20 Больше- - 14

14 - 20 Меньше014

14 - 10 Больше14

4-6 Меньше04

4-2 Больше12

0 2-2 Равно1О

О - 2 МеньшеОО

Таким образом, на выходах 32 формируется результат в коде 6-2-2-1: код 1101 0110, то есть - корректный результат числа 94.

. В зависимости от значения второго управляющего сигнала на входе 24 открыты либо элементы И группы 9 (положительный уровень сигнала, выдача результата в двоичном коде), либо группы 10 (нулевой уровень сигнала, выдача результата в задайном двоично-десятичном коде).

. Блок 8 формирования знака (фиг. 5) ра- ботэет следующим образом, Знак результата-нулевой для положительного результата и единичный для отрицательного формируется в соответствии с выражением:

Вых Знд -Знв -Знв -(А В) +

+ ЗнА-Знв(А В),

где А и В - значения операндов, Знд и Знв - их знаки, +, и - соответственно операции логического сложения, логического умножения и отрицания. При этом на выходе блока сравнения 46 формируется высокий потенциал при А В (на выходе, соединенном с элементом ИЛИ 47), на

выходе, соединенном с элементом ИЛИ 48 - высокий потенциал формируется при А В, на выходе, соединенном с обоими элементами 47 и 48 - при А В. На выходах элементов И 51, И 52 и ИЛИ-НЕ 53 формируются единичные значения сигнала соответственно при единичном значении с первой по третью конъюнкций приведенного выражения; в этом случае результат положительный и на выходе 33 элемента ИЛИ-НЕ 54- нулевой потенциал; в остальных случаях результат отрицательный и на выходе 33 - высокий потенциал.

Таким образом, заявленное устройство позволяет производить вычисления как в

двоичной системе счисления, так и в широком классе двоично-десятичных кодов. Кроме того, велико его быстродействие, единственным ограничением которого является естественная задержка распространения сигнала по узлам устройства, не требующая организации работы по тактам.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1989 |

|

SU1667259A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU864278A1 |

| Устройство для преобразования двоично-десятичного кода в двоичный | 1985 |

|

SU1300641A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых величин | 1987 |

|

SU1476616A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1285604A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый | 1979 |

|

SU847318A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1984 |

|

SU1266008A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1221757A1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU898423A1 |

Изобретение относится к автоматике и вычислительной технике. Целью изобретения является расширение области применения за счет возможности использования более широкого круга двоично-десятичных кодов и повышение быстродействия. Устройство для сложения в двоичной и двоично-десятичной системах счисления содержит два регистра 1, 2 операндов, регистр 3 кода, две группы блоков 4 преобразования декад, накапливающие сумматоры 5, б, алгебраический сумматор 7, блок 8 формирования знака, две группы элементов И 9, 10, группу элементов ИЛИ 11, группу блоков 12 формирования весов декад, группу блоков 13 формирования декад и два элемента НЕ. соединенные между собой функционально. 3 з.п. ф-лы, 5 ил.

Формула изобретения 1. Устройство для сложения в двоичной и двоично-десятичной системах счисления, содержащее первую и вторую группы блоков преобразования декад, блок формирования знака, первый и второй элементы НЕ, первую группу элементов И и группу элементов ИЛИ, причем выходы элементов И первой группы соединены соответственно с первыми входами элементов ИЛИ группы, отличающееся тем, что, с целью расширения области применения путем обеспечения возможности использования более широкого круга двоично-десятичных кодов и повышения быстродействия устройства, в него введены первый и второй регистры операндов, первый и второй накапливающие сумматоры, алгебраический сумматор, вторая группа элементов И, регистр кода, группа из (К -1) блоков формирования весов декад (К - количество декад входных чисел) и группа из К блоков формирования декад, причем информационные входы первого и второго регистров операндов соединены соответственно с первым и вторым информационными входами устройства, с первым синхровходом которого соединены входы разрешения записи первого и второго регистров операндов, разрядные выходы первого регистра операндов соединены подекадно с первыми информационными входами соответствующих блоков преобразования декад первой группы, разрядные выходы второго регистра операндов соединены подекадно с первыми информационными входами соответствующих блоков преобразования декад второй группы, а знаковые разрядные выходы первого и второго регистров операндов соединены соответственно с первым и вторым знаковыми входами алгебраичного сумматора и с первым и вторым знаковыми входами блока

формирования знака, информационный вход регистра кода соединен с установочным входом устройства, второй синхровход которого соединен с входом разрешения записи регистра кода, выход которого соединен с входом первого блока формирования весов декад, со вторыми информационными входами первых блоков преобразования декад первой и второй групп и с первым входом первого блока формирования декад группы, выход 1-го блока формирования ве- сов декад группы (I 1, К - 2) соединен с входом (i + 1}-го блока формирования весов декад группы, вторыми информационными входами (I + 1)-х блоков преобразования декад первой и второй групп и с первым входом (i + 1)-ro блока формирования декад группы, выход (К- 1)-го блока формирования весов декад группы соединен со вторыми информационными входами К-х блоков преобразования декад первой и второй групп и первым входом К-ro блока формирования декад группы, первый вход управления режимом работы устройства соединен с первыми управляющими входами блоков преобразования декад первой и второй групп и входом первого элемента НЕ, выход которого соединен со вторыми управляющими входами блоков преобразования декад первой и второй групп, выходы блоков преобразования декад первой группы соединены с входом первого накапливающего сумматора, выход которого соединен с первым информационным входом алгебраического сумматора и с первым информационным входом блока формирования знака, выходы блоков преобразования декад второй группы соединены с входом второго накапливающего сумматора, выход которого соединен с вторым информационным входом алгебраического сумматора и вторым информационным входом блока

формирования знака, выход которого соединен со знаковым выходом устройства, разрядные выходы алгебраического сумматора соединены соответственно с первыми входами элементов И первой группы и вторым входом К-ro блока формирования декад группы, первый выход J-ro блока формирования декад группы (j 2. К) соединен с вторым входом Q - 1)-го блока формирования декад группы, вторые выходы блоков формирования декад группы соединены с первыми входами элементов И второй группы, второй управляющий вход устройства соединен с вторыми входами элементов И первой группы и входом второго элемента НЕ, выход которого соединен с вторыми входами элементов И второй группы, выходы которых соединены с вторыми входами элементов ИЛИ группы, выходы которых являются информационными выходами устройства.

мультиплексора и входами второй группы узла формирования разряда декады, выход схемы сравнения соединен с управляющим входом мультиплексора, информационные входы второй группы которого соединены соответственно с разрядными выходами вычитателя, а выход мультиплексора является первым выходом узла формирования разряда декады, вторым выходом которого является выход схемы сравнения, входы первой группы первого, второго, третьего и четвертого узлов формирования разряда декады соединены с первым входом блока формирования декады, второй вход которого соединен с входами второй группы четвертого узла формирования разряда декады, первый выход первого узла формирования разряда декады является первым выходом блока формирования декады, вторые выходы первого, второго, третьего и четвертого узлов формирования разряда декады являются вторым выходом блока формирования декад, первый выход 1-го узла формирования разряда декады (I 2, 4) соединен с вторым входом (I - 1)-го узла формирования разряда декады.

Фиг 4

Jur.

:5

| Устройство для сложения | 1980 |

|

SU920709A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Устройство для сложения в двоичной и в двоично-десятичной системе счисления | 1985 |

|

SU1273919A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-01-23—Публикация

1990-12-19—Подача