(54 УСТЮЙСТВО ДЛЯ УМНОЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения и деленияпОСлЕдОВАТЕльНО-пАРАллЕльНОгОдЕйСТВия | 1979 |

|

SU817703A1 |

| Устройство для умножения | 1985 |

|

SU1278838A1 |

| Устройство для умножения целых чисел в р-кодах Фибоначчи | 1986 |

|

SU1345190A1 |

| Устройство для умножения | 1982 |

|

SU1136151A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения | 1980 |

|

SU960805A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Арифметическое устройство | 1988 |

|

SU1578708A1 |

Изобретение относится к вычислительной технике и может быть использовано в устрой ствах обработки дискретной информации для выполнения операций умножения над числами, представленными в двоично-десятичном коде. Известно устройство умножения 1 , содержаще формирователь синхронизирующих импульсов, выход которого соединен с первым входом элемента И, регистр множимого, регист множителя и схему деления количества последовательных импульсов. Известное устройство сложно и имеет низкое быстродействие, так как для получения ре зультата умножения двух чисел необходимо произвести большое количество операций сложения, равное произведению сомножителей. Наиболее близким по технической сущности к предложенному является устройство умножения 2, содержащее триггер пуска, триггер ре верса, регистры множимого и множителя, формирователь синхроимпульсов, схему знака и схему управления, счетчик результата, вычитающий счетчик и элементы И и ИЛИ, причем выход формирователя синхроимпульсов соеди иен с первым входом первого элемента И, второй вход которого соединен с прямым выходом триггера пуска, а выход, через второй злемент И, соединен со входом счетчика результата, выходы регистров множимого и множителя через многовходовые элементы И и элемент ИЛИ соединены со счетными входами вычитающего счетчика и триггера реверса. Описанное устройство обладает низким быстродействием, так как для получения результата умножения двух чисел требуется большое число операций, равное произведению сомножителей. Цель изобретения - повыщение быстродействия. Указанная цель достигается тем, что устройство для умножения, содержащее триггер операции, регистры множимого и множителя, декады счетчика результата,, элемент И, при этом первый вход элемента И соединен с первым выходом формирователя синхроимпульсов, второй вход - с прямым выходом триггера операции, S-вход которого является управляющим входом устройства, согласно изобретению, содержит также два анализатора цифр операнда, коммутатор, группу элементов И и группу элементов ИЛИ. При этом первый, второй и третий выходы формирователя синхроимпульсов соединены с соответствующими входами синхронизации первого и второго анализаторов цифр операнда, информационные входы которых соединены с выходами соответственно регистра множимого и регистра множителя, а первые управляющие входы соединены с управляющим входом устройства. Выход элемента И соединен со вторым управляющим входом первого анализатора цифр операнда, а третий вход элемента И соединен с первым управляющим выходом второго анализатора цифр операнда, второй управляющий вход которого соединен со вторым управляющим выходом первого анализатора цифр операнда, а третий управляющий выход -- с R-входом триггера операции. Группы выходов первого и второго анализаторов цифр операнда соединеньг с соответствующими руппами входов коммутатора, выходы которого соединены с информационными входами соответствующих элементов И группы, входы синхронизации элементов И группы соединены с выходом элемента И, выходы i-тыХ элементов И группы (i 2-п, где п - количество ра,зрядов произведения ммнус единица) соединены с первыми входами j-тых элементов ИЛИ (J 1-п-Т) группы, выходы которых соединены со счетными входами (j+l)-x декад счетчика результата, вторые входы j-тых элементов ИЛИ группы соединены со счетными выходами j-ftix декад счетчика результата, счетный вход первой декады которого соединен с выходом первого элемента И группы.

Кроме этого, анализатор цифр операнда содержит вычитающий счетчик, суммирующий счечик, дешифратор, коммутатор цифр, два триггера, четыре элемента И и два элемента ИЛИ, при этом счетный вход вычитающего счетчика является вторым управляющим входом анализатора цифр операнда, группа информационных входов вычитающего счетчика соединена с группой выходов коммутатора цифр, а выход - с первым входом первого элемента И и S-BXOдом первого триггеру, единичный выход которого соединен с первыми входами второго и третьего элементов И. Второй вход второго элемента И и первый вход четвертого элемента И являются первым входом синхронизации анализатора цифр операнда, вторым входом синхронизации которого являются R-входы первого и второго триггера, а третьим входом синхронизации - второй вход третьего элемента И. Третий вход второго элемента И соеди.нен с нулевым выходом второго триггера, а выход - с первым входом первого элемента ИЛИ и счетным входом суммирующего счетчика, вход установки нуля которого соединен со вторым входом первого элемента ИЛИ и выходом четвертого элемента И, являющегося третьим управляющим выходом анализатора цифр операнда. Информационные выходы суммирующего счетчика соединены с входами дешифратора, информационные выходы которого соединены с соответствующими входами коммутатора цифр и являются группой выходов анализатора цифр операнда. Управляющий выход дешифратора соединен со вторым входом первого элемента И, информационные входы которого являются информационными входами анализатора цифр операнда, выход которого соединен с S-входом второго триггера и является вторым управляющим выходом анализатора цифр операнда. Вь:ход третьего элемента И соединен с первым входом второго элемента ИЛИ второй вход которого является первым управляющим входом анализатора цифр операнда, а выход соединен с входом синхронизации коммутатора цифр, информационные входы которого являются информационными входами анализатора цифр операнда. Выход первого элемента ИЛИ соединен с входом установки нуля вычитающего счетчика, единичный выход второго триггера соединен со вторым входом четвертого элемента И, а нулевой выход первого триггера является первым управляющим выходом анализатора цифр операнда.

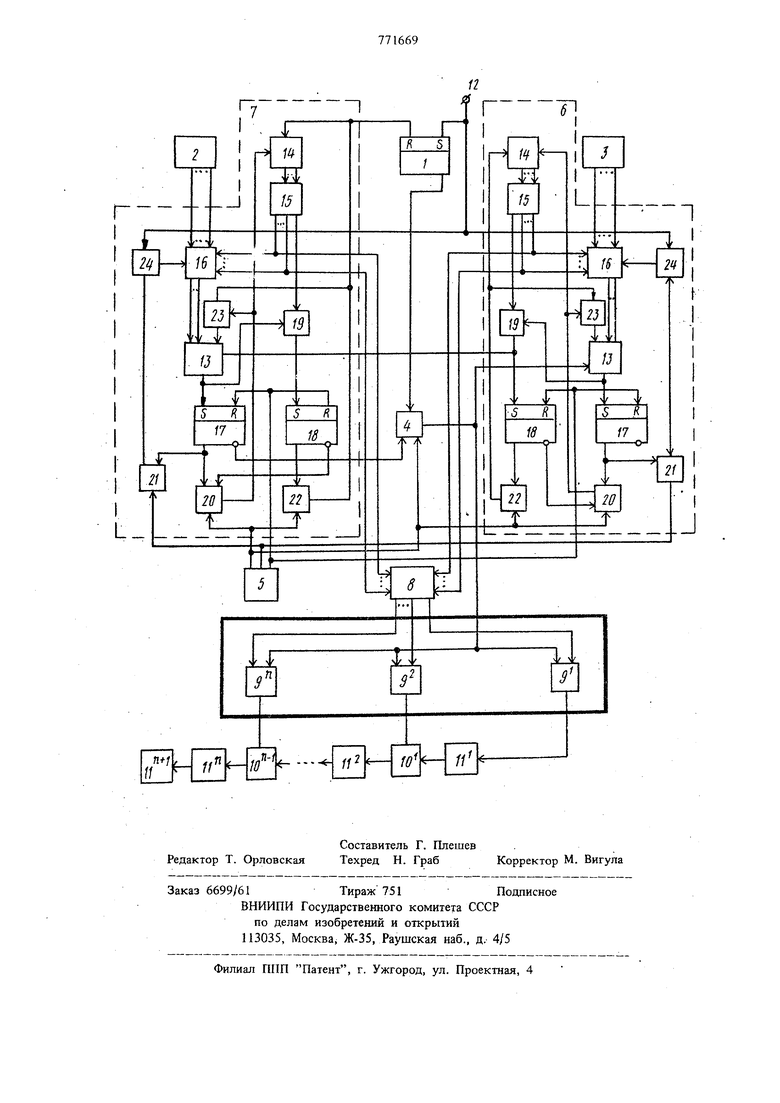

На чертеже представлена схема устройства умножения, содержащего триггер I операции, регистр 2 множителя, регистр 3 множимого, элемент И 4, формирователь 5 синхроимпульсов, первый и второй анализаторы 6 и 7 цифр операнда, коммутатор 8, группу элементов И 9 - И 9 .группу элементов ИЛИ 10-Ю, декады счетчика результата и управляющий вход 12. из анализаторов 6 и состоит из вычитающего счетчика 13, суммирующего счетчика 14, дешифратора 15, коммутатора 16 цифр, первого и второго триггеров 17 и 18, четырех элементов И 19-22 и двух элементов ИЛИ 23 и 24.

Устройство работает следующим образом.

Перед началом работы триггер 1 операции, суммирующие счетчики 14, регистр 2 множителя, вычитающие .счетчики 13, триггеры 17, 18, регистр 3 множимого, декады П-И счетчика результата устанавливаются внулевое (исходное) состояние (цепи установки элементов памяти не показаны).

В. регистр 2 множителя записывается значение множителя в двоично-десятичном коде, а в регистр 3 множимого - значение множимого также в двоично-десятичном коде.

Устройство начинает работать с момента поступления сигнала на управляющий вход 12 устройства. По этому сигналу триггер 1 операции устанавливается в еггиничное состояние. Одновременно этот сигнал через элементы ИЛИ 24 анализаторов 6 и 7 постутЕает на входы коммутаторов 16 цифр, Коммутатор 16 цифр анализатора 6 осуществляет перепись двоично-десятичного кода каждого разряда множимого из регистра 3 множимого и вычитающий счетчик 13. Так как суммирующий счетчик 14 находится в исходном состоянии, то по сигналу управления в вычитающий счетчик 13 записывается двоично-десятичный код первого разряда множимого. Одновременно по сигнал , поступившему с выхода элемента ИЛИ 24 анализатора 7, срабатывает коммутатор 16, кс:-, 1рый осуществляет перепись двоично-десятичнс о- кода соответствующего разряда множителя из регистра 2 множителя в вычитающий счетчик 13. В рассматриваемом случае, когда суммирующий счетчик 14 находится в исходном состоянии, в вычитающий счетчик 13 записывается двоично-десятичный код первого разряда множителя. Сигнал с единичного выхода триггера 1 операции открывает по первому входу элемента И 4, на третий вход которого предварительно подан сигнал разрещения с нулевого выхода триггера 17 анализатора 7, а на второй вход - импульсы с первого вь1хода формирователя 5 синхроимпульсов. С выхода элемента И 4 последо вательность импульсов подается на счетный вход вычитающего счетчика 13 анализатора 6 и одновременно на один из входов группы элементов И 9 - И 9 . На другие входы группы элементов И 9 - И 9 поступает сигнал с соответствующего выхода коммутатора 8. Коммутатор 8 в зависимости от сигналов на информационных выходах суммирующих счетчиков 14 анализаторов 6 и 7, которые через соответствующие дешифраторы 15 поступают на его входы, формирует соответствующий выходной сигнал, открывающий один из элементов группы элементов И 9 - И 9 . В результате последовательность импульсов с выхода элемента И 4 подается на вход соответствующей декады 11 - 11 счетчика результата. В начальный момент суммирующий счетчик 14 анализатора 7 установлен в исходном состоянии, что соответствует первому циклу операции умножения. Суммирующий счетчик 14 анализатора 6 также находится в нулевом состоянии, что соответствует первому микротакту операции умножения. На основании этих сигналов комму татор 8 формирует выходной сигнал, который открывает только один элемент И 9 группы и последовательность импульсов с выхода элемейта И 4 начинает поступать на вход первой декады П счетчика результата. После того как на счетный вход вьгчитающе го счетчика 13 анализатора 6 и одновременно на вход первой декады П счетчика результата поступит 1ШСЛО импульсов, равное значению первой декады множимого, на выходе вычитающего счетчика 13 формируется сигнал, совпадающий с импульсом на первом выходе формирователя 5 синхроимпульсов. Данный сигнал формируется в момент перехода вычитающего счетчика 13 в нулевое состояние. Триггер 17 устанавливается в единичное состояние. Сигнал с единичного выхода триггера 17 открывает элемент И 20, предварительно подготовленный к срабатыванию сигналом управления с нулевого выхода триггера 18. Импульс с первого выхода формирователя 5 синхроимпульсов через открытый элемент И 20 поступает на счетный вход суммирующего счетЧи-ка 14 и через элемент ИЛИ 23 - на вход установки нуля вычитающего счетчика 13. При этом суммирующий счетчик 14 переходит в первое состояние, а вычитающий счетчик 13 устанавливается в исходное (нулевое) состояние. Сигналы с информационных выходов суммирующего счетчика 14 поступают на вход дешифратора 15. На одном из его информационных выходов формируется очередной сигнал, который, с одной стороны, подготавливает коммутатор 16 цифр для записи двоично-десятичного кода второго разряда множимого в вычитающий счетчик 13 и, с другой стороны, дает возможность коммутатору 8 сформировать сигнал на втором выходе. При этом сигнал с выхода коммутатора 8 подготавливает к срабатыванию элемент И 9 Кроме того, сигнал с единичного выхода триггера 17 открывает элемент И 21. Импульс с третьего выхода формирователя 5 синхроимпульсов через открытый элемент И 21 и через элемент ИЛИ 24 подается на вход коммутатора 16 цифр, в результате чего в вычитающий счетчик 13 записывается двоично-десятичный код очередного, второго разряда множимого. С выхода элемента И 4 последовательность импульсов продолжает поступать на счетный вход вычитающего счетчика 13 и через открытый элемент И 9 и элемент ИЛИ 10 - на вход второй декады 11 счетчика результата. Аналогично описанному устройство для умножения работает до тех пор, пока не будет закончен предпоследний микротакт операции умножения. При этом по сигналу с выхода элемента И 20 суммирующий счет1шк 14 переходит в очередное состояние, а вычитающий счетчик 13 устанавливается в исходное состояние. Сигнал управления с первого информадионного выхода дешифратора 15 открывает элемент И 19. Сигнал с соответствующего второго информационного выхода децд1фратора 15, вопервых, подготавливает коммутатор 16 цифр для записи в вычитающий счетчик 13 двоичнодесятичного кода последнего разряда множимо го и, во-вторых, oбecпe швaeт коммутатору 8 возможность формирования управления входом соответствующей декады П-П счетчика результата для приема последовательности импульсов в последнем микротакте. Импульс с третьего выхода формирователя синхроимпульсов через открытый элемент И 21 через элемент ИЛИ 24 подается на управляющи вход коммутатора 6 цифр, в результате чего в вычитающий счетчик 13 записывается двоичн десятичный код последнего разряда множимого Импульс со второго выхода формирователя 5 синхроимпульсов устанавливает триггер 17 в н левое состояние. С выхода элемента И 4 последовательность импульсов продолжает поступать на счетный вход вычитающего счетчика 13 анализатора 6 и на вход соответствующей декады счетчика результата. После того как на счетный вход вычитающе го счетчика 13 и одновременно на вход соответствующей декады счетчика результата посту пит число импульсов, равное значению последнего разряда множимого, на его выходе формируется сигнал, который постзшает, во-первы на S-вход триггера 17 и через открытый элемент И 19 на S-вход триггера 18, устанавливая их в единичное состояние, и, во-вторых, на счетный вход вычитающего счетчика 13 ана лизатора 7. При этом число, записанное в нем и равное первому разряду множителя, уменьшается на единицу. Импульс с первого выхода формирователя 5 синхроимпульсов через открытый элемент И 22 поступает на вход установки нуля суммирующего счетчика 14 анализатора б и через элемент ИЛИ 23 - на вход установки нуля вычитающего счетчика 13. Импульс с третьего выхода формирователя синхроимпульсов через открытый сигналом с единичного выхода триггера 17 элемент И 21 и через элемент ИЛИ 24 поступает на вход коммутатора 16 Щ1фр. В результате в вычитающий счетчик 13 записывается двоично-десятич ный код первого разряда множимого. Так как суммирующие счетчики 14 анализаторов 6 и 7 опять находятся ,в исходном сост янии, то, аналогично описанному, коммутатор 8 формирует на первом выходе сигнал, который снова открывает элемент И 9. Сигналом со второго выхода формирователя 5 синхроимпульсов в нулевое состояние ус танавливаются триггеры 17 и 18 анализатора 6 Таким образом осуществляется окончание первого такта операции умножения и переход к выполнению второго такта. 98 После выполнения первого такта операции умножения в счетчике результата находится число, равное значению множимого. В последующих тактах устройство работает аналогично. При этом общее число тактов равно значению первого разряда множителя. В процессе выполнения последующих тактов операции умножения осуществляется сложение промежуточного результата со значением соответствующего разряда множимого. Как было отмечено ранее в конце каждого такта операции умножения на выходе элемента И 19 анализатора 6 формируется сигнал, поступающий на счетный вход вычитающего счетчика 13 анализатора 7. После того как на его вход будет подано число импульсов, равное значению первого разряда множителя, что соответствует окончанию выполнения процедуры умножения на разряд множителя, т.е. окончанию первого цикла операции умножения, на выходе вычитающего счетчика 13 анализатора 7 формируется сигнал. По этому сигналу триггер 17 анализатора 7 устанавливается в единичное состояние. Сигналом с единичного выхода триггера 17 открывается элемент И 20, предварительно подготовленный по второму входу сигналом управления с нулевого выхода триггера 18, Импульс с первого выхода формирователя 5 синхроимпульсов через открытый элемент И 20 поступает на счетный вход суммирующего счетчика 14, а через элемент ИЛИ 23 - на вход установки нуля вь1читающего счетчика 13. При этом суммирующий счетчик 14 переходит в первое состояние, а вычитаюший счетчик 13 - в исходное состояние. Сигналы с информационных выходов суммирующего счетчика 14 поступают на входы дещифратора 15. На одном из его информационных выходов формируется сигнал управления, который,-во-первых, подготавливает коммутатор 16 цифр для записи двоично-десятичного кода второго разряда множителя и, во-вторых, дает возможность коммутатору 8 сформировать сигнал управления элементом И 9 группы. Это обеспечивает сдвиг на одну декаду при записи множимого в счетчик результата, так как очередной цикл работы устройства умножения соответствует операции умножения на следующий разряд множителя. Кроме того, сигнал с единичного Выхода триггера 17 вдкла открывает элемент И 21. Импульс с третьего выходаформирователя 5 синхроимпульсов через открытый элемент И 21 и через элемент ИЛИ 24 подается на вход коммутатора 16 цифр, в результате чего в вычитающий счетчик 13 записывается двоично-десятичный код второго разряда множителя. Одновременно аналогично описанному по сигналу с третьего выхода формирователя 5 синхроимпульСОВ осуществляется запись в вычитающий счет чик 13 анализатора 6 двоично-десятичного кода первого разряда множимого. Затем сигнало со второго выхода формирователя 5 синхроим пульсов триггер 17 анализатора 7 и триггеры и 18 анализатора 6 устанавливаются в нулевое состояние. С выхода элемента И 4 последовательность импульсов продолжает поступать на счетный вход вычитающего счетчика 13 анализатора 6 и через открытый элемент И 9 группы и эле мент ИЛИ Ю группы - на вход второй декады 11 счетчика результата. Устройство умножения работает аналогично описанному, при этом коммутатор 8 обеспечи вает необходимый сдвиг на одну декаду. После того как на вход вычитающего счетчика 13 анализатора 7 поступит число импульсов, равное значению второго разряда множителя, что соответствует окончанию умножения ; на второй разряд множителя, на выходе вычи тающего счетчика 13 анализатора 7 формирует ся очередной сигнал. Аналогично описанному, осуществляется перевод в очередное состояние суммирующего счетчика 14, запись двоично-десятичного кода очередного разряда множителя в вычитающий счетчик 13 анализатора 7 и запись двоичнодесятичного кода первого разряда множителя ,в вычитающий счетчик 13 анализатора 6. После окончания выполнения предпоследнего цикла суммирующий счетчик 14 анализатора 7 переводится в состояние, соответствующее под готовке устройства к умножению на последний разряд множителя. Устройство для умножения осуществляет аналогично описанному умножение на последний разряд множителя. После того как на вход вычитающего счетчика 13 анализатора 7 поступит число импуль.сов, равное значению последнего разряда множителя, на его выходе формируется сигнал, который поступает на S-вход триггера 17 и через элемент И 19, подготовленный сигналом с информационного выхода децшфратора 15 на S-вход триггера 18, устанавливая их в единичное состояние. Сигнал с единичного выхода триггера 18 открывает элемент И 22. Импульс с первого выхода формирователя 5 синхроимпульсов через открытый элемент И 22 поступает на вход установки нуля суммирующего счетчика 14, через элемент ИЛИ 23 на вход установки нуля вычитающего счетчика 13 и на R-вход триггера 1 операщ1и, устаналивая их в исходное (нулевое) состояние. Одновременно устанавливается в исходное со стояние суммирующий счетчик 14 и вычитающий счетчик 13 анализатора 6. 10 После установки триггера 1 операции в нулевое состояние с1шмается сигнал управления с входа элемента И 4, в результате чего прекращается поступление последовательности импульсов на вход декад П-П счетчика результата. Импульс со второго выхода формирователя 5 синхроимпульсов устанавливает в нулевое состояние триггеры 17 и 18 анализаторов 6 и 7. После этого устройство, возвращается в исходное состояние. На этом операция умножения заканчивается и устройство готово к выполнению очередной оператцш умножения. Предлагаемое устройство для умножения по сравнению с известными устройствами обладает более высоким быстродействием, так как количество тактовых импульсов, необходимое , для вычисления произведения двух чисел, равно произведению сумм цифр этих чисел. Формула изобретения 1. Устройство для умножения, содержащее триггер опера1ши, регистры множимого и множителя, декады счетчика результата, элемент И, при этом первый вход элемента И соединен с первым выходом формирователя синхроимпульсов, второй вход - с прямым выходом триггера операции, S-вход которого является управляющим в.ходом устройства, отличающееся гем, что, с целью повышения быстродействия, в него дополнительно введены два анализатора цифр опера1ща, коммзтатор, группа элементов И и группа элементов ИЛИ, при этом первый, второй и третий выходы формирователя синхроимпульсов соединены с соответствующими входами синхронизации первого и второго анализатора цифр операнда, информацио) входы которых соединены с выходами соответстве)но регистра множимого и регистра множителя, а первые управляющие входы соединены с управляющим входом устройства, выход элемента И соединен со вторым управляющим входом первого анализатора цифр операнда, а третий вход элемента И соединен с первым управляющим выходом второго анализатора цифр операнда, второй управляющий вход которого соединен со вторым управляющи.м выходом первого анализатора цифр операнда, а третий т1равляющий выход - с R-входрм триггера операции, группы выходов первого и второго анализаторов Щ1фр операнда соединены с соответствующими группами входов коммутатора выходы которого соединены с информационным входами соответствующих элементов И группы, входы синхронизации элементов И группы соедицены с выходом элемента И, выходы i-тьтх элементов И группы (i 2-п, где п - количество раз11

рядов произведения минус еданица) соединены с первыми входами j-тых элементов ИЛИ (J 1-П-1) группы, выходы которых соединены со счетными входами (j-Hl)-x декад счетчика результата, вторые входы j-тых элементов ИЛИ группы соединены со счетными выходами j-тых декад счетчика результата, счетный вход первой декады которого соединен с выходом первого элемента И группы.

6912

и выходом четвертого элемента И, являющегося третьим управляющим выходом анализатора цифр операнда, информационные выходы суммирующего счетчика соединены с входами дещифратора, информационные выходы которого соединены с соответствующими входами коммутатора цифр и являются группой выходов анализатора цифр операнда, а управляющий выход дешифратора соединен со вторым входом первого элемента И, информационные входы которого являются информационными входами анализатора цифр операнда, выход которого соединен с S-входом второго триггера и является вторым управляющим выходом анализатора

цифр операнда, выход третьего элемента И соединен с первым входом второго элемента ИЛИ, второй вход которого является первым управляющим входом анализатора цифр операнда, а выход соединен с входом синхронизации коммутатора цифр, информационные входы цоторого являются информационными входами анализатора цифр операнда, выход первого элемента ИЛИ соединен с входом установки нуля вычитающего счетчика, единичный выход второго триггера

соединен со вторым входом четвертого элемента И, а нулевой выход первого триггера является первым управляющим выходом анализатора цифр операнда.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1980-10-15—Публикация

1978-10-18—Подача