(54) ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Резервированное запоминающее устройство с самоконтролем | 1982 |

|

SU1070609A1 |

| Полупроводниковое запоминающее устройство | 1984 |

|

SU1238157A1 |

| Запоминающее устройство | 1977 |

|

SU720509A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1978 |

|

SU769628A1 |

| Оперативное запоминающее устройство | 1978 |

|

SU868831A1 |

| НАКОПИТЕЛЬ ЭЛЕКТРИЧЕСКИ ПРОГРАММИРУЕМОГО ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1991 |

|

RU2028676C1 |

| Полупроводниковое запоминающее устройство | 1978 |

|

SU748508A1 |

| Запоминающее устройство | 1982 |

|

SU1023393A1 |

I

Изобретение относится к вычислительной технике и может найти применение в интегральных микросхемах постоянных запоминающих устройств (ПЗУ), микропроцессоров, микрокалькуляторов.

-Известно ПЗУ, содержащее матричный накопитель, запоминающие элементы которого связаны с щинами строк и столбцов. Дешифраторы шин строк и столбцов, выходы которых соединены с соответствующими шинаТйи, адресные и выходные шины 1.

Недостатком указанного ПЗУ является сравнительно низкое быстродействие, обусловленное малой выходной мощностью дешифраторов.

Наиболее близким к предлагаемому по технической сущности является устройство, обеспечивающее высокое быстродействие и содержащее матричный накопитель, блоки выборки строк и столбцов накопителя, подг ключенные соответственно к каждой строке и столбцу, дешифраторы, подключенные к каждому из блоков выборки 2.

Однако в известном устройстве большое

количество МДП-элементов на кристалле и

большая площадь кристалла, а следовательно, высокая стоимость и невысокая надежность.

Цель изобретения - упрощение устройства, ведущее к снижению стоимости микросхемы и повышению надежности за счет уменьшения количества элементов на кристалле.

Поставленная цель достигается тем, что в полупроводниковое ПЗУ, содержащее матричный накопитель, шины строк и столбцов которого подключены к выходам блоков выборки, а первые входы блоков выборки шин столбцов и нечетных шин строк соединены с выходами соответствующих дешифраторов, адресные шины и шины тактовых сигналов, введены ключевые элементы, выполненные на МДП-транзисторах, и селектор тактовых сигналов, причем сток каждого МДП-транзиcтopJ соединен с нечетной шиной строки, а исток соединен с первым входом блока выборки четной шины строки, первая шина тактовых сигналов соединена с первым входом селектора и входами дешифраторов, вторая шина тактовых сигналов соединена с затворами МДП-транзисторов ключевых элементов, со вторым входом селектора и со вторыми входами блоков выборки нечетных

шин строк, третья шина тактовых сигналов соединена с третьим входом селектора и со вторыми входами блоков выборки четных шин строк, четвертый вход селектора соединен с адресной шиной, а выход селектора соединен со вторыми входами блоков выборки шин столбцов.

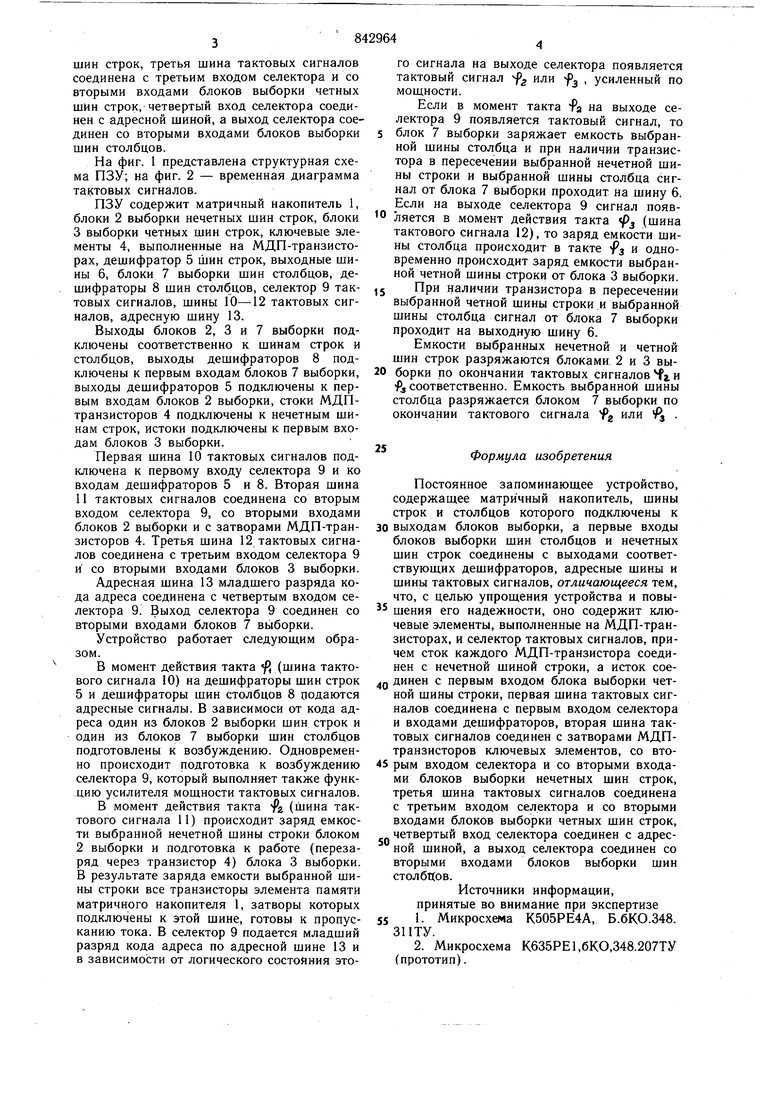

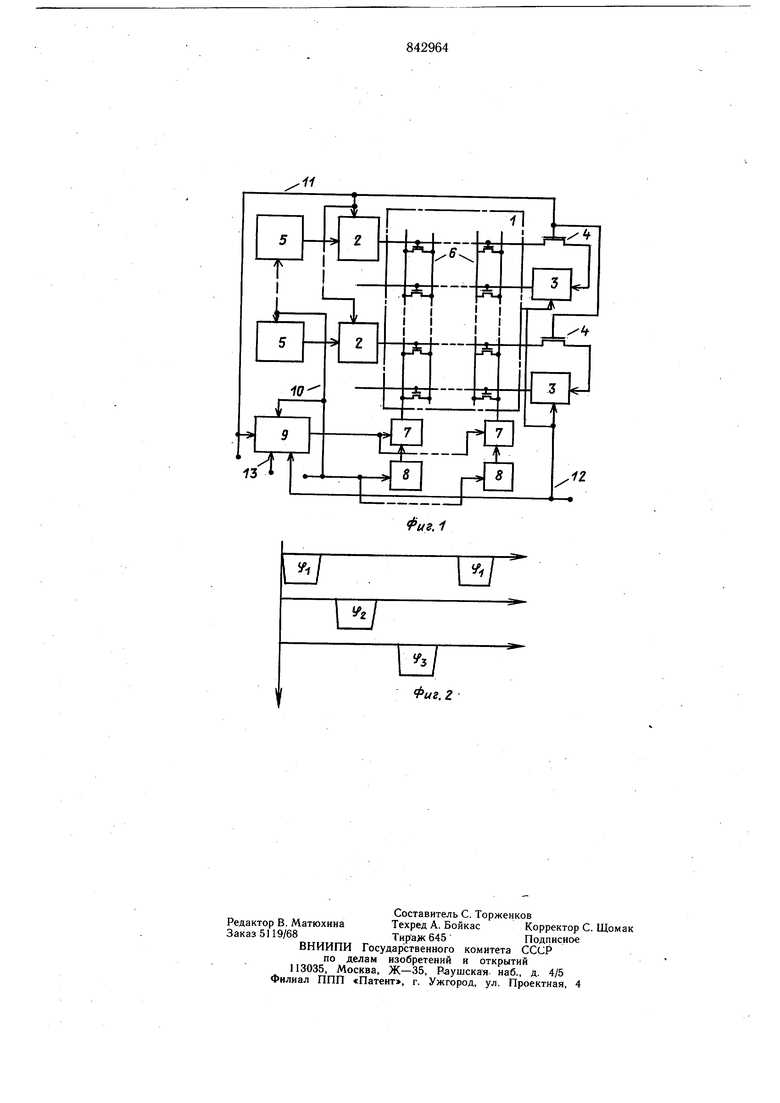

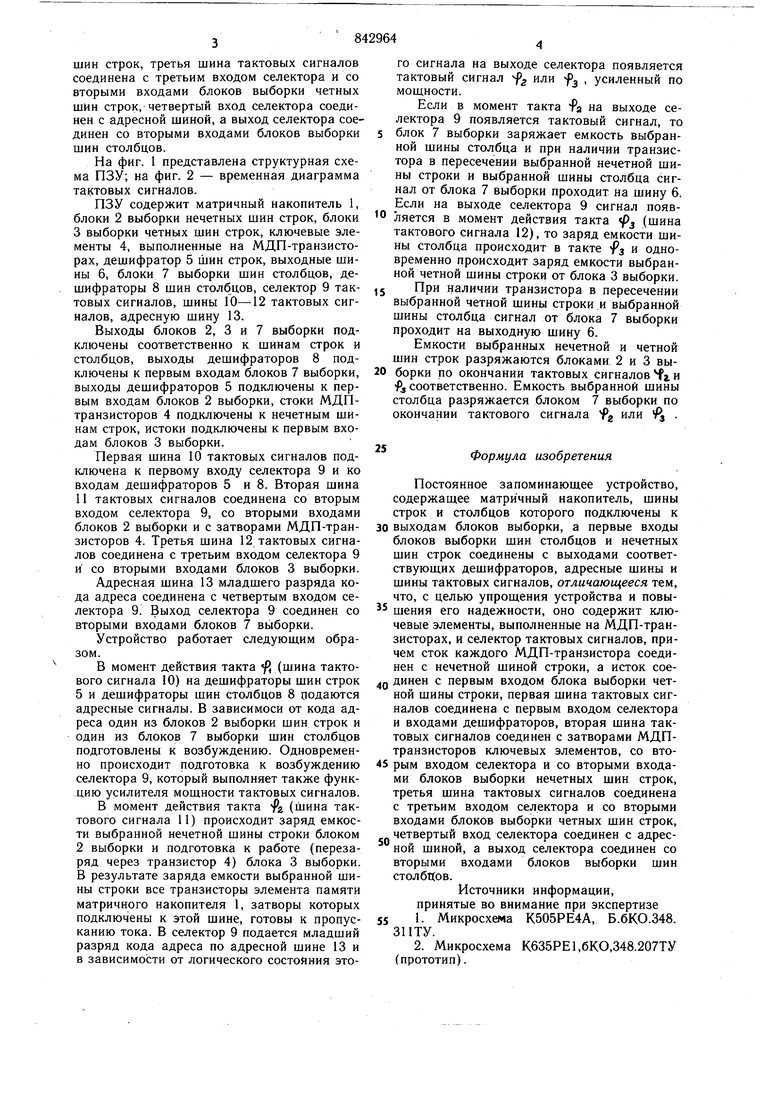

На фиг. 1 представлена структурная схема ПЗУ; на фиг. 2 - временная диаграмма тактовых сигналов.

ПЗУ содержит матричный накопитель 1, блоки 2 выборки нечетных шин строк, блоки 3 выборки четных шин строк, ключевые элементы 4, выполненные на МДП-транзисторах, дешифратор 5 шин строк, выходные шины 6, блоки 7 выборки шин столбцов, дешифраторы 8 шин столбцов, селектор 9 тактовых сигналов, шины 10-12 тактовых сигналов, адресную шину 13.

Выходы блоков 2, 3 и 7 выборки подключены соответственно к шинам строк и столбцов, выходы дешифраторов 8 подключены к первым входам блоков 7 выборки, выходы дешифраторов 5 подключены к первым входам блоков 2 выборки, стоки МДПтранзисторов 4 подключены к нечетным шинам строк, истоки подключены к первым входам блоков 3 выборки.

Первая шина 10 тактовых сигналов подключена к первому входу селектора 9 и ко входам дешифраторов 5 и 8. Вторая шина 11 тактовых сигналов соединена со вторым входом селектора 9, со вторыми входами блоков 2 выборки и с затворами МДП-транзисторов 4. Третья шина 12 тактовых сигналов соединена с третьим входом селектора 9 и со вторыми входами блоков 3 выборки.

Адресная шина 13 младшего разряда кода адреса соединена с четвертым входом селектора 9 Выход селектора 9 соединен со вторыми входами блоков 7 выборки.

Устройство работает следующим образом.

В момент действия такта /} (шина тактового сигнала 10) на дешифраторы шин строк 5 и дешифраторы шин столбцов 8 цодаются адресные сигналы. В зависимоси от кода адреса один из блоков 2 выборки шин строк и один из блоков 7 выборки шин столбцов подготовлены к возбуждению. Одновременно происходит подготовка к возбуждению селектора 9, который выполняет также функцию усилителя мощности тактовых сигналов.

В момент действия такта « (iliHHa тактового сигнала 11) происходит заряд емкости выбранной нечетной шины строки блоком 2 выборки и подготовка к работе (перезаряд через транзистор 4) блока 3 выборки. В результате заряда емкости выбранной шины строки все транзисторы элемента памяти матричного накопителя 1, затворы которых подключены к этой шине, готовы к пропусканию тока. В селектор 9 подается младший разряд кода адреса по адресной шине 13 и в зависимости от логического состояния этого сигнала на выходе селектора появляется тактовый сигнал fj или fj , усиленный по мощности.

Если в момент такта fa на выходе селектора 9 появляется тактовый сигнал, то

блок 7 выборки заряжает емкость выбранной шины столбца и при наличии транзистора в пересечении выбранной нечетной шины строки и выбранной шины столбца сигнал от блока 7 выборки проходит на шину 6. Если на выходе селектора 9 сигнал появляется в момент действия такта (шина тактового сигнала 12), то заряд емкости шины столбца происходит в такте fj и одновременно происходит заряд емкости выбранной четной шины строки от блока 3 выборки.

Г1ри наличии транзистора в пересечении выбранной четной шины строки .и выбранной шины столбца сигнал от блока 7 выборки проходит на выходную шину 6.

Емкости выбранных нечетной и четной шин строк разряжаются блоками 2 и 3 выборки по окончании тактовых сигналов fг и Рд соответственно. Емкость выбранной шины столбца разряжается блоком 7 выборки по окончании тактового сигнала Р или .

Формула изобретения

Постоянное запоминающее устройство, содержащее матричный накопитель, шины строк и столбцов которого подключены к

выходам блоков выборки, а первые входы блоков выборки шин столбцов и нечетных шин строк соединены с выходами соответствующих дещифраторов, адресные шины и шины тактовых сигналов, отличающееся тем, что, с целью упрощения устройства и повыщения его надежности, оно содержит ключевые элементы, выполненные на МДП-транзисторах, и селектор тактовых сигналов, причем сток каждого МДП-транзистора соединен с нечетной шиной строки, а исток соединен с первым входом блока выборки четной шины строки, первая шина тактовых сигналов соединена с первым входом селектора и входами дешифраторов, вторая шина тактовых сигналов соединен с затворами МДПтранзисторов ключевых элементов, со вторым входом селектора и со вторыми входами блоков выборки нечетных шин строк, третья шина тактовых сигналов соединена с третьим входом селектора и со вторыми входами блоков выборки четных шин строк, четвертый вход селектора соединен с адресной шиной, а выход селектора соединен со вторыми входами блоков выборки шин столбцов.

Источники информации, принятые во внимание при экспертизе

5 1. Микросхема К505РЕ4А, Б.бКО.348. ЗПТУ.

Авторы

Даты

1981-06-30—Публикация

1979-10-08—Подача