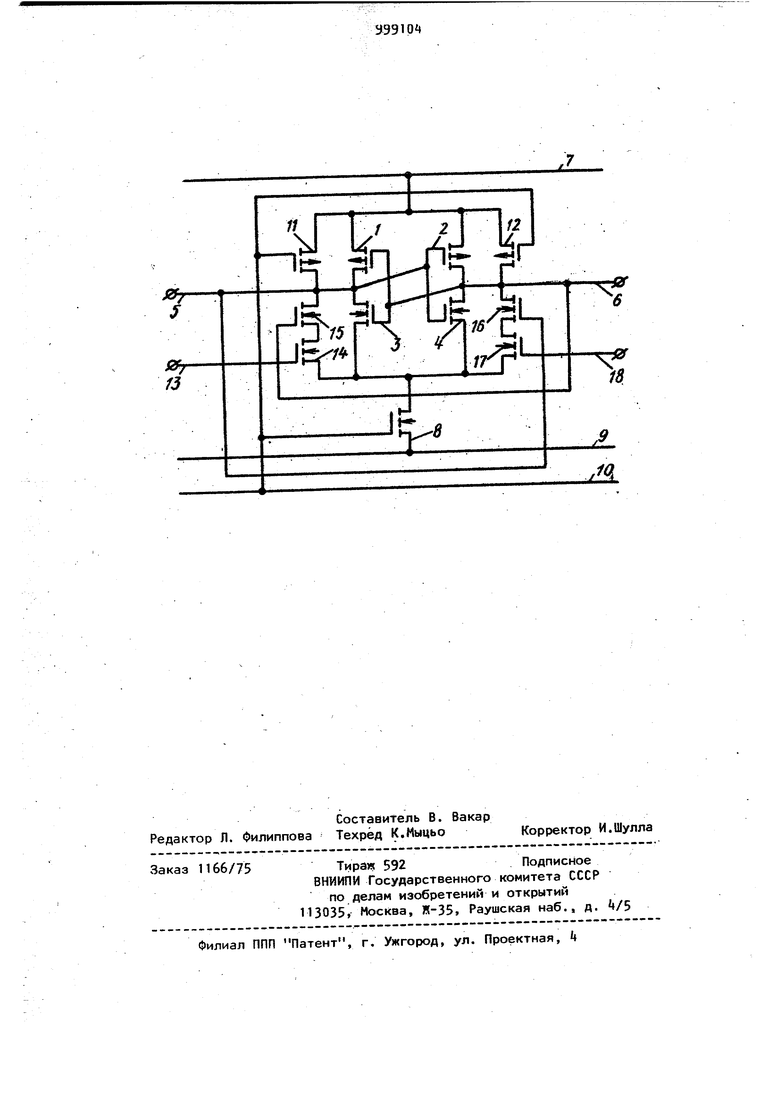

вы)оду усилителя-формирователя и к затворам первых транзисторов р и У -типа, истоки транзисторов р-типа триггера подключены к шине питания, ключевой транзистор и-типа, сток которого подключен к истокам транзисторов Vi-типа триггера, исток соединен с ши-ной нулевого потенциала, а затвор - с управляющей шиной, два транзистора подзаряда р-типа, истоки которых подключены к шине питания, сток первого транзистора подзаряда соедине.н; с инверсным выходом усилите ля-формирователя, а сток второго транзистора подзаряда соединен с пря мым выходом усилителя-формирователя затворы, транзисторов подзаряда объединены и связаны с управляющей шиной Информационный вход усилителя-формирователя подключен к затвору информа ционного транзистора Vi-типа, исток которого подключен к стоку ключевого транзистора, а сток соединен с истоком транзистора и-типа обратной св зи, сток которого подключен к инверсному выходу, а затвор - к прямому выходу усилителя-формирователя. Этот усилитель-формирователь отличается простотой схемы и используется в случаях, когда не требуются повышенные стабильность и чувствительность переключательной характеристики схемы 21. Недостатком известного усилителяформирователя является низкая его стабильность и чувствительность. Целью изобретения является повышение надежности усилителя-формирователя. Поставленная цель достигается тем что усилитель-.формирователь для оперативного запоминающего устройства на КМДП-транзисторах, содержащий пер вый и второй транзисторы р-проводимости, третий и четвертый транзисторы Ц -проводимости, при этом стоки первого и третьего транзисторов подключены к первому выходу усилителяформирователя и к затворам второго и четвертого транзисторов, стоки ко Topbix подключены к второму выходу усилителя-формирователя и к затворам первого и третьего транзисторов, истоки первого и второго транзисторов подключены к шине питания, истоки третьего и четвертого транзисторов подключены к стоку ключевого тран. зистора У)-проводимости, исток которого соединен с шиной нулевого потенциала, а затвор - с шиной управления, первый и второй транзисторы подзаряда р-проводимости, истоки которых подключены к шине питания, сток первого транзистора подзаряда соединен с первым выходом усилителя-формирователя, а сток второго транзистора подзаряда соединен со вторым выходом усилителя-формирователя, затворы первого и второго транзисторов.подзаряда подключены к шине управления, информационный транзистора-проводимости, исток которого соединен со стоком ключевого транзистора, затвор - с информационным входом усилителя-формирователя, а сток - с истоком первого транзистора обратной связи п.-проводимости, сток и затвор которого соответственно подключены к первому и второму выходам усилителя-формирователя, также содержит опорный транзистор VI -проводимости и второй транзистор обратной связи я-проводимости, исток которого соединен со стоком опорного транзистора, сток и затвор соответственно со вторым и первым выходами усилителя-формирователя, затвор опорного транзистора подключен к опорному входу усилителя-формироват аля, а исток - к стоку ключевого транзистора. На чертеже представлен усилительформирователь. Устройство содержит первый и второй транзисторы 1 и 2 р.-проводимости, третий и четвертый 3 и транзисторы И-проводимости, первый выход 5, второй выход 6, шину 7 питания, ключевой транзистор 8 И-ПРОВОДИМОСТИ, шину 9 нулевого потенциала, шину 10 управления, первый и второй транзисторы подзаряда р-проводимости соответственно 11 и 12, информационный вход 13, информационный транзистор 1 П-проводимости, первый и второй транзисторы обратной связи и-проводимости соответственно 15 и 16, транзистор 17 и-проводимости, опорный вход 18. Усилитель-формирователь работает следующим образом. В исходном состоянии (режим хранения в ЗУ) потенциал на шине 10 управления соответствует логическому О. На опорный вход 18 подано опорное напряжение, соответствующее требуемой зоне переключения усилителя по входному напряжению. Ключевой транзисторов закрыт, а открытые первый и BTopoi транзисторы, 11 и 12 под заряда устанавливают hfa первом и втором выходах 5 и 6 хровни логической 1. При этом первый и второй транз1 сторы 1 и 2 закрываются, а тре тий и четвертый транзисторы 3 и открываются. Первый и второй транзисторы 15 и 16 обратной связи открыты. Опорным напряжением на опорном входе 18 опорный транзистор 17 приоткрыт и находится в определенной точке вольт-амперных характеристик, В зависимости от логического уровня на информационном входе 13 информационный транзистор Т может быть-:ЛИбо открыт, либо закрыт. В любом случае состояние информационного транl j не влияет на состояние зистора усилителя-формирователя, поскольку ключевой транзистор 8 закрыт. В режиме хранения на информационном, входе 13 .должна быть установлена ин-л формация, подлежащая обработке усилителем. 3 режиме призма и запоминания входной информации (режим обращения в ЗУ) на шине 10 управления I„ . устанавливается уровень логической 1. Транзисторы 11 и 12 подзаряда закрываются, а ключевой транзистор 8 открывается. Предположим, что на информационный вход 13 подана логическая 1. Паразитные емкости в узлах схемы, свя занных с первым 5 и вторым 6 ми, начинают разряжаться через открытые транзисторы 3 и i, ключевой транзистор 8, информационный транзистор 1, первый и второй транзисторы 15 и 16 обратной сВЯЗИ;.опорный транзистор 17. Так как величина опорного напряжения лежит в зоне между уров1| ями логического О и логической 1 информационный транзистор будет открыт больше опорного транзистора Т7, следовательно ток, протекающий через информационный транзистор 14 . и первый транзистор 15 обратной связи будет больше тока, протекающего через второй транзистор Тб обратной связи и опорный транзистор 17 В Р9 зультате разряд паразитной e |1кocти связанной с первым выходом 5) произойдет быстрее и соответственно первыи, второй,,тритии и четвертый транзисторы, 1, 2, 3, установятся в со-, стояние, когда на выходе 5 будет ло0гический О на втором выходе 6 логическая 1 (транзисторы 1 закрыты, а транзисторы 2, 3 открыты). По цепи обратной связи второй транг зистор 16 обратной связи закроется, а первый транзистор 15 обратной свя-. зи останется открытым, Схема сохранит (запомнит) установившееся состояние при любых изменениях информации на входе, так как состояние информационного транзистора И не может повлиять на уровень логического О на первом выходе 5 соединенном с открытым третьим транзистором 3. При подаче на информационный вход 13 логического О информационный транзистор Н закроется (или подзакроется в случае подачи на вход 13 уровня логического О, величина которого близка к порогу переключения усилителя), Вэтом случае ток, протекающий через второй транзистор 16 обратной связи и опорный транзистор . 17 (п|эавое плечо усилителя), будет больше и первый второй у третий и Четвертый 1, 2, 3 и 4 транзистора установятся в состояние когда на втором выходе 6 будет логический 0% а на первом вы) 5 логическая 1 (транзисторы 1J Ц открытыJ а транзисторы 2, 3 закрыты), Пёрвыйтр зиртор 15 обратной связи зацгроется, а / второй Транзистор 1.6 «б ратной связи останется .. При закрытом первом транзийтбре 5 обратной связи изменение логического состояния на информационном входе 13 не может изменить, установившийся уровень логической t на первом выходе 5 соег. дйненном-с открытым первым транзистором.; Таким образом, усилитель-формирователь запоминает поданную на вход информацию. При этом входная информация подаётся на схему до перехода к режиму обращения и удерживается в том режиме на время, достаточное ля срабатывания схемы, пбсле чего нформация на входе усилителя может зменяться. Высокие стабильность и чувствиельность усилителя-формирователя опеделяются наличием стабильного опорого напряжения и симметричностью леч усилителя во всем диапазоне детабилизирующих факторов, гарантирумой технологическим процессом изотовления интегральной микросхемы ЗУ. 79991 Стыковка усилителя-формирователя по входу с ТТЛ-схемами обеспечивается соответствующим выбором величины опорного напряжения и пороговых напряжений МДП-транзисторов. Предлагаемый усилитель-формирователь обладает более высоко- стабильностью и чувствительностью, чем известный и может быть применен в высококачественных интегральных ЗУ на КМДП-транзисторах в качестве элемента регист ра и в качестве схемы приема и запоминания сигналов входной .информации и запись-считывание. Использование усилителя-формирователя в интегральной микросхеме ЗУ повысит надежность блока ЗУ и вычислитеИьной системы в целом, поскольку снизится чувствительность мин росхемы ЗУ к сбоям временной диаграммы- в части.сигналов адреса, входной информации, запись-считывание, Помимо этого на 5-10 сократится число интегральных схем обращения в блоке ЗУ, так как исключаются макросхемы согласования уровней и регистр адреса. Соответственно снизится стоимость и увеличится надежность блока ЗУ. эмула изобретения Усилитель-форми11о ватель для oneративного запоминающёг& усхройства на КМДП-транзисторах, содерж ь му. первый и второй транзисторы р-про- - водимости, третий и четвертый транзисторы ,Vi -проводимости, при этом стоки первого и третьего транзисторов подключены к первому выходу усилите ля-формирователя и к затворам второго и четвертого транзисторов, стоки которых подключены к второму выходу усилителя-формирователя и к затворам первого и третьего транзисторов, истоки первого и второго транзисторов 5 10 подключены к шине питания, истоки третьего и четвертого транзисторов подключены к стоку ключевого транзистора И-проводимости , исток Которого соединен с шиной нулевого потенциала, а затвор - с шиной управления, первый и второй транзисторы подзаряда р-проводимости, истоки которых подключены к шине питания, сток первого транзистора подзаряда соединен с первым выходом усилителя-формирователя, а сток второго транзистора подзаряда соединен со вторым выходом усилителяформирователя, затворы первого и второго транзисторов подзаряда подключены к шине управ-ления, информационный транзистор и-проводимости, исток которого соединен со стоком ключевого транзистора, затвор - с информационным входом усилителя-формирователя, а сток - с истоком первого транзистора обратной связи И-проводимости. сток и затвор которого соответственно подключены к первому и второму выходам усилителя-формирователя, о т личающиися тем, что, с целью повышения надех ности усилителяформирователя, он содержит опорный транзистор И-проводимости и второй транзистор обратной связи И-проводимоои, исток которого соединен со стоком опорного транзистора, сток и затвор - соответственно со вторым и первым выходами усилителя-формирователя, затвор опорного транзистора подключен к опорному входу усилитетя-формирователя, а исток - к стоку кл1&чевасо транзистора. Источники информации, принятые во внимание при экспертизе 1. G, Ramachandran .Single-Supply erasable PROM saves power with CMOS process. - Electronics, If Й, 1978. pp. 106-111. 2. Авторское свидетельство СССР по заявке № 2950389/18-24, кл. G 11 С 7/00, 1980 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Входной усилитель-формирователь с запоминанием информации | 1980 |

|

SU903970A1 |

| Усилитель считывания на КМДП-транзисторах | 1986 |

|

SU1377910A1 |

| Усилитель на кмдп-транзисторах | 1979 |

|

SU862236A1 |

| Усилитель считывания на КМДП транзисторах | 1986 |

|

SU1376117A1 |

| Усилитель считывания на кмдп-транзисторах | 1978 |

|

SU771716A1 |

| Усилитель для запоминающего устройства | 1981 |

|

SU999103A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1980 |

|

SU888206A1 |

| Усилитель считывания | 1983 |

|

SU1134965A1 |

| Усилитель считывания | 1981 |

|

SU1015435A1 |

| Функциональный коммутатор на КМДП-транзисторах | 1988 |

|

SU1506540A1 |

Авторы

Даты

1983-02-23—Публикация

1981-07-06—Подача