I

Изобретение относится к запоминающим устройствам и может быть использовано при построении микромощных интегральных запоминающих устройств на дополняющих МДП-транзисторах.

Известен усилитель считывания, построенный на основе симметричного триггера, в котором затворы нагрузочных транзисторов соединены с разрядными шинами, а емкости симметричных узлов перед считыванием заряжаются до одинакового потенциала с помощью стробируемых транзисторов П.

Недостатками этого усилителя являются низкие чувствительность и быстродействие.

Наиболее близким техническим решением к данному изобретению является усилитель считывания для-запоминающего устройства на дополняющих МДП-транзисторах, содержащий первый и второй р-канальные транзисторы, соединенные триггерной связью, истоки которых подключены к шине питания

и истокам р-канальных транзисторов первого и второго интерторов, причем сток первого р-канального транзистора соединен с входом первого инвертора и стоком первого нагрузочного п-канального транзистора, сток второго р-канального транзистора соединен с входом второго инвертора и стоком второго нагрузочного п-канапьного транзистора, входы первого и

10 второго инверторов соединены соответственно с первым и вторым выходами уси/мтеля затворы первого и второго нагрузочных п-канальных транзисторов соединены соответственно с

15 первой и второй разрядными шинами, истоки-- со стоком ключевого п-канального транзистора, затвор которого соединен с первой шиной управления, исток - с общей шиной, истоки

М п-канальных транзисторов первого и второго инвертора соединены со стоком к/ж чевого п-каналь 1ого т нзистора, к первой шине управления подключен затвор симметрирующего транзистора, исток которого связан с входом первого инвертора, а сток - с входом второго инвертора С23. Недостатками известного усилителя являются низкая чувствительность и низкое быстродействие, обусловленное отсутствием управления напряжениями отпираний транзисторов с помощью напряжения на разрядных шинах, Цель изобретения - повышение чувствительности и быстродействия усилителя. Поставленная цель достигается тем, что в усилитель считывания, содержащий первый и второй переключающие р-канальные транзисторы, соединенные по триггерной схеме, нагрузоч ные и ключевой п-канальные транзисто ры, первый и второй инвертирующие р-канальные транзисторы и третий и четвертый инвертирующие п-канальные транзисторы, причем сток первого переключающего транзистора подключен к стоку первого нагрузочного и затвора первого и третьего инвертирующих транзисторов, сток, второго переключа щего транзистора соединен с затворами второго и четвертого инвертирую щих транзисторов и стоком второго на грузочного транзистора, истоки нагрузочных транзисторов подключены к стоку ключевого транзистора, исток которого соединен с шиной нулевого потенциала, а затвор является первым управляющим входом усилителя, истоки первого и второго инвертирующих тран зисторов подключены к шине питания, затворы первого и второго нагрузочны Транзисторов являются соответственно первым и вторым входами усилителя, стоки первого и третьего инвертирующих транзисторов объединены и являются первым выходом усилителя, а стоки второго и четвертого инвертиру

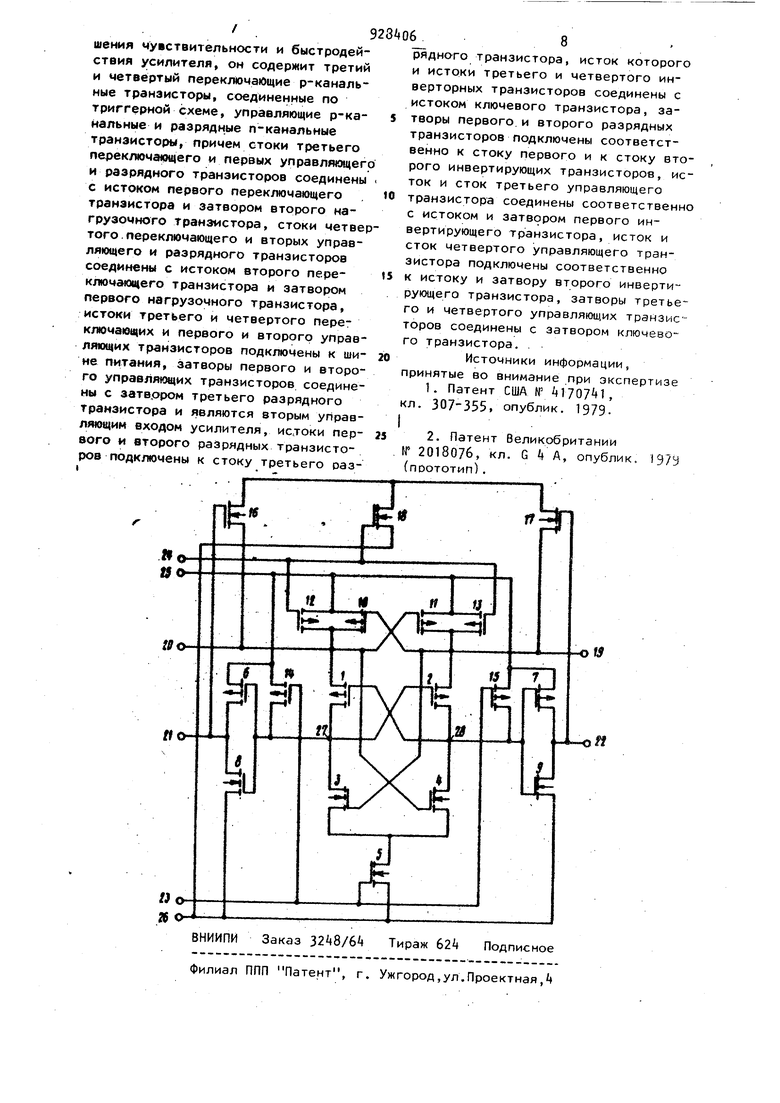

ющих транзисторов объединены и являются вторым выходом усилителя, введены третий и четвертый переключающие р-канальные транзисторы, соединенные по триггерной схеме, управляющие р-канальные и разрядные п-канальные транзисторы, причем стоки третьего переключающего и первых управляющего и разрядного транзисторов соединены с истоком первого переключающего транзистора и затвором второго нагрузочного транзистора, стоки четвертого переключающего итый 15 Р канальные управляющие транзисторы, первый 16, второй 17 и третий 18 п-канальные разрядные транзисторы. На чертеже обозначены первый 19 и второй 20 входы, первый 21 и второй 22 выходы, первый 23 и второй 2 управляющие входы усилителя, содержащего также шину 25 питания и шину 26 нулевого потенциала. На че{зтеже обозначены также сток 27 первого и сток 28 второго переключающих транзисторов. Входы 19 и 20 усилителя подключаются через вторых управляющего и разрядного транзисторов соединены с истоком второго переключающего транзистора изатвором первого нагрузочного транзистора, истоки третьего и четвертого переключающих и первого и бторого управляющих .транзисторов подключены к шине питания, затворы первого и второго управляющих транзисторов соединены с затвором третье го разрядного транзистора и являются вторым управляющим входом усилителя, истоки первого и второго разрядных транзисторов подключены к стоку третьего разрядного транзистора, исток которого и истоки третьего и четвертого инверторных транзисторов соединены с истоком ключевого транзистора, затворы первого и второго разрядных транзисторов подключены соответственно к стоку первого и к стоку второго инвертирующих транзисторов, исток и сток третьего управляющего транзистора соединены соответственно с истоком и затвором первого инвертирующего транзистора, исток и сток четвеотого управляющего подключены соответственно к истоку и затвору второго инвертирующ го транзистора, затворы третьего и че.твертого управляющих транзисторов соединены с затвором ключевого транзистора. На чертеже приведена принципиальная схема усилителя считывания. Усилитель содержит пер&ый 1 и второй 2 переключающие р-канальные транзисторы, первый 3 и второй Ц нагрузочные п-канальные транзисторы, ключевой 5 п-канальный транзистор, первый 6 и второй 7 р-канальные, третий 8 и Четвертый 9 п-канальные инвертирующие транзисторы, третий 10 и четвертый 11 р-канальные переключающие транзисторы, первый 12, второй 13 третий Н и четверсоответствующие разрядные шины и дополнительные транзисторы в запоминающем устройстве (на чертеже не показаны) к запоминающим элементам блока памяти (на чертеже не показан ным).. Усилитель считывания работает следующим образом. В режиме хранения напряжение на шинах управления 23 и соответствует уровню логического нуля, на входах 19 и 20 - уровню логической единицы. Транзисторы 8, 9, 12 - 15 открыты, и на стоке 2/ транзистора 1 и стоке 28 транзистора 2 устанавливаются уровни логической едмницы, а на выходах 21 и 22 - уровни логического нуля. В режиме считывания первоначально подается сигнал логической едини цы на вход 2k, При этом закрываются транзисторы 12 и 13, и входы 19 и 20 усилителя оказываются изолирован ными от шины питания 25iЧерез один из входов, например 20, начинает протекать ток считывания от выбранноге элемента блока памяти (на черт же не показанного). Изменения напряжения на входах 19 и 20 приводит к изменению проводимости нагрузочных транзисторов 3 и Ц, а также к изменению напряжений на стоках 27 и 28 соответственно транзисторов 1 и т.е. к изменению напряжений отпирания транзисторов 1 и 2. Если не учитывать влияние напряжения между подложкой и истоком транзисторов 1 и 2 на их пороговые напряжения, то изменение напряжения отпирания транзисторов 1 и 2 равно изменению напряжения на входах 19 и 20. Изменение напряжения между подложкой и истоком транзисторов 1 и 2 приводит к измене нию пороговых напряжени°й транзисторов 1 и 2. Это приводит к дополнительному изменению напряжений отпира ния транзисторов 1 и 2. После того как напряжение на входах 19 и 20 превысит некоторую величину (разбаланс усилителя), на первый управляющий вход 23 подается сигнал логической единицы. Транзистор 5 открывается, и в усилителе происходит регенеративный процесс. На стоке 27 транзистора 1 начинает устанавливаться уровень логического нуля, а на стоке 28 транзистора 2 - уровень логической единицы. Транзисторы 6 и 8 переключаются, что приводит к откры6«ванию транзистора 16. Через транзмсторы 16 и 18 происходит разряд емкости шины блока памяти, подк/ж чен ной к входу 20, в результате чего открывается транзистор 11 и закрывается транзистор 4. При этом на стоке 28 транзистора 2 устанавливается уровень логической единицы, и исключается сквозное протекание тока через усилитель после его переключе ния. После окончания переходного процесса на выходе 21 устанавлиаается уровень логической единицы, а на выходе 22 - уровень логического нуля. Технико-экономическое преим ество предложенного усилителя заключается в более высоких, по сравнению с известным,быстродействии и чувствительности. Формула . изобретения Усилитель считывания, содержащий первый и второй переключающие р-канальные транзисторы, соединенные по триггерной схеме, нагрузочные и ключевой п-канальные транзисторы, первый и второй инаертируинцие р-канальные транзисторы и третий и четёертый инвертирующие i-канальные транзисторы, причем сток первого переключающего транзистора подк/вочен к стоку первого нагрузочного и затворам первого и третьего инвертирующих транзисторов, сток второго переключающего транзистора соединен с затворами второго и четвертого инвертирующих:транзисторов и стоком нагрузочного транзистора, ИСТОКИ нагрузочных транзисторов под. ключены к стоку ключевого транзис о тора, исток которого соединен с шиной нулевого потенциала, а :затвор является первым управляющим входом усилителя, истоки первого и второго инвертирующих транзисторов подключены к шине питания, затворы первого и второго нагрузочных транзисторов яв-; ляются соответственно первым и вторым входами усилителя, стоки первого и третьего инвертирующих транзисторов объединены и являются первым выходом усилителя, а стоки второго и четвертого инвертирующих транзисторов объединены и являются вторым выходом усилителя, отличающийся тем, что. с целью повы

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания на дополняющих МДП-транзисторах | 1982 |

|

SU1062785A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1981 |

|

SU963087A1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

| Усилитель считывания на КМДП-транзисторах | 1986 |

|

SU1377910A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1981 |

|

SU1005185A1 |

| Усилитель считывания на КМОП-транзисторах | 1983 |

|

SU1149310A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1980 |

|

SU888206A1 |

| Усилитель считывания | 1982 |

|

SU1120405A1 |

| Преобразователь уровней напряжения | 1984 |

|

SU1167725A1 |

| Динамический усилитель считывания на МДП-транзисторах | 1986 |

|

SU1336101A1 |

Авторы

Даты

1982-05-15—Публикация

1980-09-29—Подача