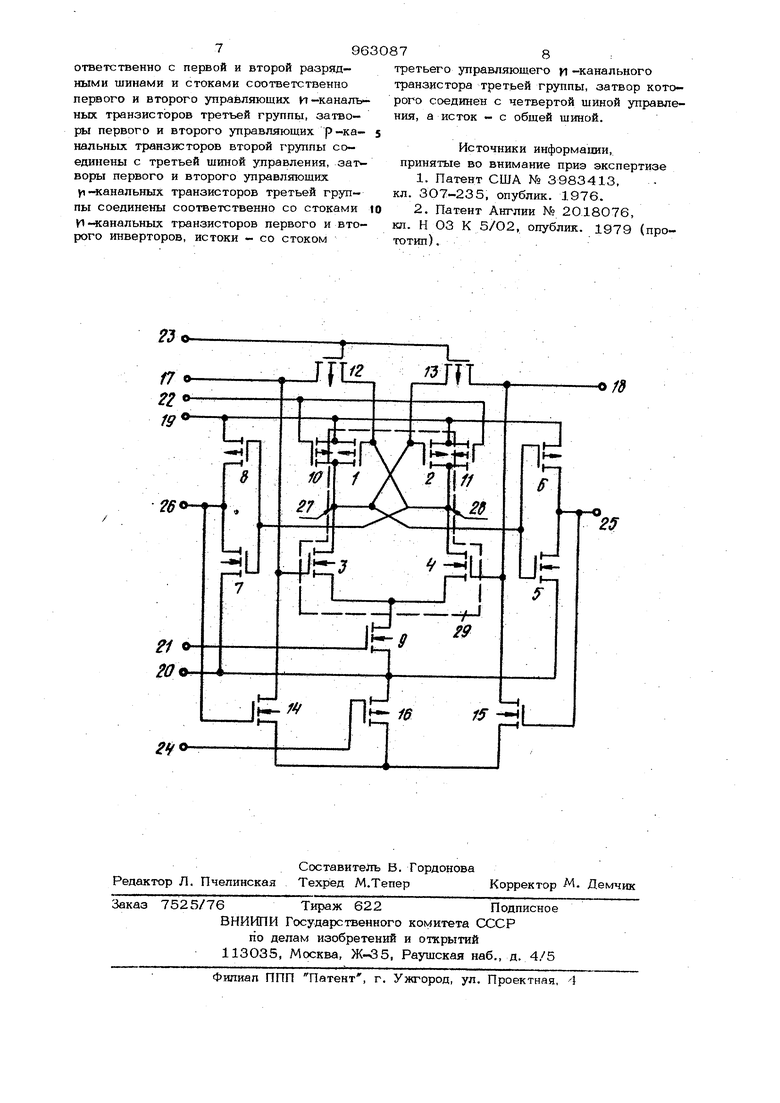

(54) УСИЛИТЕЛЬ СЧИТЫВАНИЯ НА ДОПОЛНЯЮЩИХ Изобретение относится к вычислительной технике и может бы.ть использовано при построении микромошных запоминающих устройств на дополняющих МДП-тран зисторах. Известны усилители считывания, содержащие триггер на МДП-транзисторах, в котором затворы нагрузочных транзисторов соединены с разрядными шинами l Недостатки данных усилителей - низкая чувствительность и большая потребляем ая мощность. Наиболее близок к предлагаемому усилитель считывания на дополняющих МЦП-транзисторах, содержащий первый и второй УД-Канальные транзисторы, соединенные по схеме с перекрестной связью, истоки которых соединены с шиной питания и истоками р-канальных транзисторов первого и второго инверторов, стоки соответственно со стоками первого и вто рого нагрузочных yi-канальных транзисторов, а также со входами соответственМДП-ТРАНЗИСТОРАХНО первого и второго инверторов, выходы которых соединены соответственно с первым и вторым выходами усилителя считывания, причем затворы первого и второго нагрузочных И -канальных транзисторов соединены соответственно с первой и второй разрядными шинами, истоки - со стоком ключевого и-канального транзистора, затвор которого соединен с первой шиной управления, исток - с обшей шиной, истоки ц-канальных транзисторов первого и второго инверторов соединены со стоком ключевого и-канального транзистора, к первой шине управления подключен затвор симметрирующего транзистора, исток которого связан с входом первого инвертора, а сток -. с входом второго инвер- тора С 21 Недостатками известного усилителя считывания являются низкая чувствительность, обусловленная невозможностью изменения напряжением разрядных шин напряжения в точках, к которым подклю-. чены стоки первого и второго р -канальных транзисторов, соединенных по схеме с перекрестной связью, до момента вре мени, когда открывается стробируюший транзистор, а .также большая потребляемая мощность, обусловленная медленным запиранием одного из нагрузочных И канальных транзисторов. Цель изобретения - повышение чувствительности и уменьшение потребляемой мощности усиителя считывания. Поставленная цель достигается тем, что усилитель считьшания на дополняющих МДП-транзисторах, содержащий первый и второй ключевые р-канальные тра зисторы, Соединенные тризтерной связью, истоки ключевых Р -канальных транзисторов соединены с шиной питания и истоками р-канальных транзисторов первого и второго инверторов, стоки ключевых рканальных транзисторов соединены соответственно со стоками первого и второго нагрузочных И -канальных транзисторов и затворами Р -канальных транзисторов первого и второго инверторов, стоки рканальных транзисторов которых являются соответственно первым и вторым выхода- . МИ усилителя считьюания, причем затворы первого и второго нагрузочных V -«аналь ных транзисторов соединены соответст- венно с первой и второй разрядными шинами, истоки - со стоками третьего ключевого yq-канального транзистора, затвор третьего ключевого И -канального транзистора соединен с первой шиной управления, а исток - с обшей шиной, содержи три группы управляющих И -канальных транзисторов, при этом истоки И-каналь- ных транзисторов первого и второго инверторов соединены с общей шиной, зат воры первого и второго управляющих р -канальных транзисторов первой группы соединены со второй шиной управления, истоки - с шиной питания, стоки - соответственно со стоками первого и второго нагрузочных V нканальных транзисторов и истоками первого и второго управляющих р -канальных транзисторов второй группы, стоки которых соединены соответственно с первой и второй разрядными шинами и со стоками соответственно первого и второго управляющих И -канальных транзисторов третьей группы, затворы первого и второго управляющих р -канальных транзисторов второй группы соединены с третьей шиной управления, затворы первого и второго упрарляющих Л-канальных транзисторов третьей группы соединены соответственно со стоками- И-канальных транзисторов первого и второго инверторов, истоки - со стоком третьего управляющего м -канального транзистора третьей группы, затвор которого соединен с четвертой шиной управления, а исток - с общей шиной. На чертеже представлена схема усилителя считъшания. Схема содержит ключевые первый 1 и второй 2 м -канальные транзисторы, первый 3 и второй 4 нагрузочные -канальные транзисторы, первый инвертор на транзисторах 5 и 6, второй инвертор на транзисторах 7 и 8, ключевой -канальный транзистор 9, управляющие первый 1О и второй 11 р -канальные транзисторы первой группы, управляющие второй 12 и первый 13 р -каанльные транзисторы второй группы, управляющие второй 14, первый 15 и третий 16 vi-канальные транзисторы третьей группы, первую 17 и вторую 18 разрядные шины, шину 19 питания, общую шину 2О, 21, вторую 22, третью 23 и четвертую 24 шины управления, первый 25 и второй 26 выходы усилителя считьшания, узлы 27 и 28 триггера 29, образуемого транзисторами 1-4. В схеме усилителя считывания транзисторы 1 и 2 соединены по схеме с перекрестной связью-, причем стоки соответственно подключены к стокам транзисторов 3 и 4, а истоки - к шине 19, затвор транзистора 1 связан со стоком транзистора 4, а затвор транзистора 2 - со стоком транзистора 3, истоки транзисторов 3, 4 объединены :И подключены к стоку транзистора 9, Исток которого связан с шиной 2О, а затвор - с шиной 21, затво транзистора 3 подключен к шине 17, а затвор транзистора 4 - к шине 18, затворы транзисторов 1О и 11 соединены с шиной 22, истоки - с шиной 19, а стоки - соответственно со стсясами транзисторов 1 и 2 ; затворы транзисторов 12 и 13 подключены к шине 23, истоки - соответственно к шинам 17 и 18, а стокисоответственно к затворам транзисторов 1 и 2, затвор транзистора 1 подключен к затворам транзисторов 7 и 8, стоки которых соединены с выходом 26, исток транзистора 8 связан с шиной 19, а исток транзистора 7 - с шиной 20, затвор транзистора 2 подключен к затворам транзисторов 5 и 6, стоки которых соединены с выходом 25, ticTpK транзистора 6 связан с шиной 19 а исток транзистора 5 - с шиной 20, исток транзистора 16 связан с шиной 20, затвор - с шиной 2.4, а сток - с истоками транзисторов 14 и 15, стоки которых подключены соответственно к шинам 17 и 18, а затворы связаны соответственно с выходами 26 и 25. Усилитель считьтания работает следующим образом. В режиме хранения, напряжение на шинах 17-19 и 24 соответствует уровню логической единицы, а на шинах 20-23 уровню логического нуля. Транзисторы 1, 2, 6, 8, 9, 14 и 15 закрыты. Осталь ные транзисторы открыты. В узг.ах 27 и 28 поддерживается напряжение -логической единицы, а на выходах 25 и 26 уси- лителя считывания - напряжение логического нуля. В режиме с.читьюания сначала подаетс сигнал логической единицы на шину 22. Транзисторы 10 и 11 закрьгааются и узлы 27 к 23 оказываются изолированными от шины питания. При этом паразитная емкость одной из разрядных шин (предположим шины 17) начинает заряжаться током считьгоания от выбранного элемента памяти, который в схеме ОЗУ подключен к разрядным шинам 17 и 18. Через открытые транзисторы 12 и 13 изменение напряжения раз рядных шин передается в узлы 27и 28. После того, как напряжения в узлах 27 и 28 и на разрядных шинах 17 и 18 станет дсютаточным, чтобы скомпенсиро- вать разбаланс усилителя считываний, по дается напряжение логической единицы на шины 21 и 23. При этом транзисторь1 12 и 13 закрьшаются, изолируя узлы 27 и 28 от разрядных шин 17 и 18. Транзистор 9 открьюается и в схеме раз вивается регенеративный процесс, после окончания которого триггер 29 оказьтае ся в одном из устойчивых состояний, определяемом напряжением на разрядных шинах. В узле 28 формируется уровень логического нуля. Инвертор на транзисторах 7 и 8 переключается, открьтая транзистор 14. Через открытые транзис- торы 14 и 16 ускоряется разряд емкости разрядной шины 17. После окончания переходного процесса в узлах 27 и 28 устанавливаются уровни напряжения, соот ветствукщие логической единице и нулю, соответственно на разрядной шине 17 устанавливается уровень логического нуля, на выходах усилителя 25 и 26 уровни, соответствующие логическому нулю и единице соответственно. Транзисторы 2 и 3 закрыты, обеспечивая отсутс вие протекания сквозного тока через триггер 29, Режим записи отличается от режима хранения тем, что напряжение на шине 24 соответствует уровню логического нуля, а на шине 23 - логической единицы. Моделирование на ЭВМ схемы усилителя считьтания .показало, что при одинаковом разбросе па рам е.тров предлагаемый усилитель считьгоания обладает на 20- ЗО% более высокой чувствительностью и меньшей потребляемой мощностью по сравнению с базовым объектом. Формула изобретения Усилитель считывания на дополняющих МДП-транзисторах, содержащий первый и второй ключевые р -канальные транзисторы, соединенные триггерной связью, истоки ключевых р -канальных транзисторов соединены с шиной питания и истоками р-канальных транзисторов первого . и второго инверторов, стоки ключевых р -канальных транзисторов соединены соответственно со стоками первого и второго нагрузочных п -канальных транзисторов и затворами р-канальных транзисторов первого и второго инверторов, стоки р -канальных транзисторов которых являются соответственно первым и вторым выходами усилителя считывания, при- чем затворы первого и второго нагрузоч- ных У)-канальных транзисторов соединены соответственно с первой и второй разрядными шинами, истоки - со стоками третьего ключевого h -канального транзистора, затвор третьего ключевого ц -канального транзистора соединен с первой шиной управления, а исток - с общей шиной, отличающийся тем, что, с целью повышения чувствительности и уменьшения потребляемой мощности усилителя считывания, он содержит три группы управляющих р -канальных транзисторов, при этом истоки VI -«анальных транзисторов первого и второго инверторов соединены с общей шиной, . затворы пер- вого и второго управляющих р -канальных транзисторов первой группы соединены со второй шиной управления, истоки - с шиной питания, стоки - соответственно со стоками первого и второго нагрузочных h-канальных транзисторсзв и соответст венно с истоками первого и второго управляющих р-канальных транзисторов второй группы, стоки которых соединены соответственно с первой и второй разрядными шинами и стоками соответственно первого и второго управляющих и-канапь ных транзисторов третьей группы, затворы первого и второго управляющих р-канальных транзисторов второй группы соединены с третьей шиной управления, затворы первого и второго управляющих

yi-«анальных транзисторов третьей группы соединены соответственно со стоками

ц-«анальных транзисторов первого и второго инверторов, истоки - со стоком

третьего управляющего yt -канального транзистора третьей группы, затвор которого соединен с четвертой шиной управления, а исток - с обшей шиной.

Источники информации, принятые во внимание приз экспертизе

1.Патент США № 3983413, кл. ЗО7-235, опублик. 1976.

2.Патент Англии N° 2018076,

кп. Н ОЗ К 5/О2, опублик. 1979 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания на дополняющих МДП-транзисторах | 1982 |

|

SU1062785A1 |

| Усилитель считывания | 1980 |

|

SU928406A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1981 |

|

SU1005185A1 |

| Усилитель для запоминающего устройства | 1981 |

|

SU999103A1 |

| Динамический усилитель считывания на МДП-транзисторах | 1986 |

|

SU1336101A1 |

| Усилитель считывания | 1982 |

|

SU1120405A1 |

| Усилитель считывания на КМОП-транзисторах | 1983 |

|

SU1149310A1 |

| Выходной усилитель | 1981 |

|

SU1015436A1 |

| Преобразователь уровней напряжения | 1984 |

|

SU1167725A1 |

| Усилитель считывания на кмдп-транзисторах | 1978 |

|

SU771716A1 |

Авторы

Даты

1982-09-30—Публикация

1981-03-30—Подача