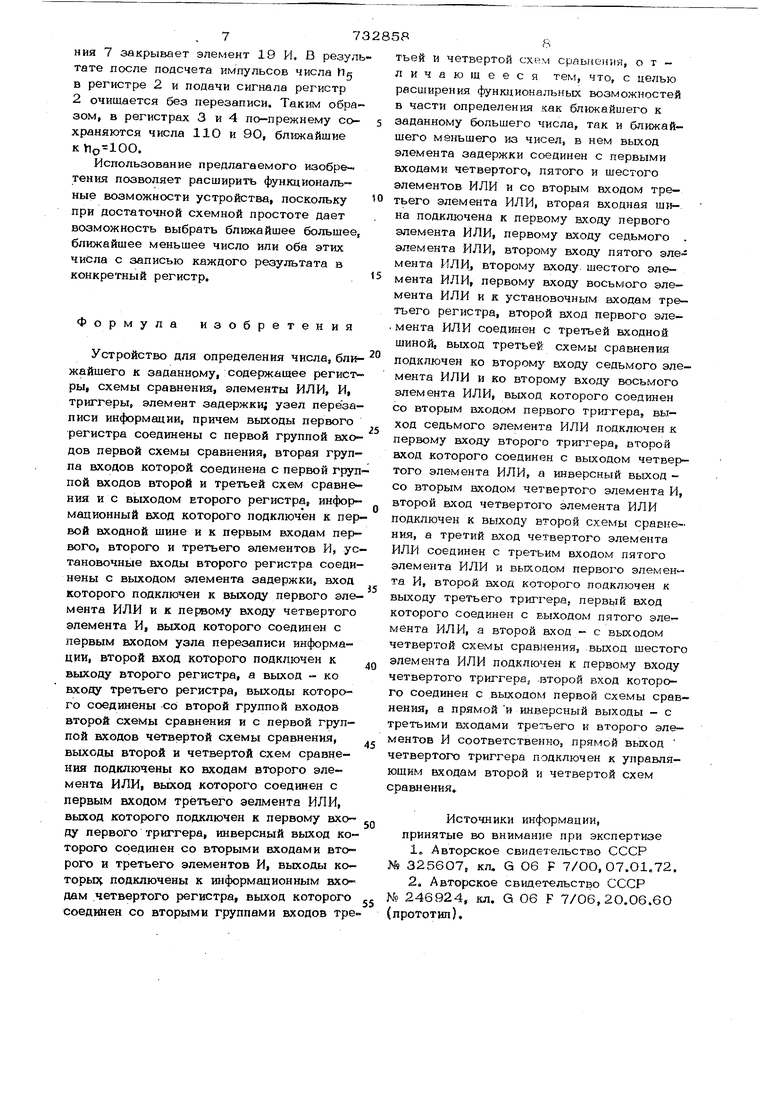

дам четвертого регистра, выход которого соединен со вторыми группами входов третьей н четвертой схем сравнения. Кроме того, оно содержит регистр заданного числа, два регистра приема чисел, схему определения положения заданного числа относительно двух других, записанных на данном этапе сравнения в регистры приема схемы совпадения и линии задержки 2.. Недостаток устройства - невысокие функциональные воэможности. При использовании устройства в том случае, если среди множества чисел имеются как ближайшее большее, так и ближайшее меньшее, выбирается только одно из них, другое же ближайшее число теряется. Кроме того, неизвестен регистр, в котором оказывается результат выбора. Цель изобретения - расширение функциональных возможностей устройства в части определения как ближайшего большего, так и ближайшего меньшего из чисел. Поставленная цель достигается тем, что в устройстве для определения числа, ближайшего к заданному, выход элемента задержки соединен с первыми входами чет вертого, пятого и шестого элементов ИЛИ и со вторым входом третьего элемента ИЛИ, вторая входная шина подключена к первому входу первого элемента ИЛИ, первому входу седьмого элемента ИЛИ, второму входу пятого элемента ИЛИ, второму входу шестого элемента ИЛИ, первому входу восьмого элемента ИЛИ и к установочным входам третьего регистра, второй вход первого элемента ИЛИ соединен с третьей входной шиной, выход третьей схемы сравнения подключен ко второму входу седьмого элемента ИЛИ и ко второ tviy входу восьмого элемента ИЛИ, выход которого соединен со вторым входом первого триггера, выход седьмого элемента ИЛИ подключен к первому входу второго триггера, второй вход которого соединен с выходом четвертого элемента ИЛИ, а инверсный выход - со вторь1М входом чет вертого элемента И, второй вход четвертого элемента ИЛИ подключен к выходу второй схемы сравнения, а третий вход четвертого элемента ИЛИ соединен с третьим входом пятого элемента ИЛИ и выходом первого элемента И, второй вход которого подключен к выходу третьего триггера, первый вход которого соединен с выходом пятого элемента ИЛИ, а второй вход - с выходом четвертой схемы сравнения, выход шестого элемента ИЛИ подключен к первому входу четвертого триггера, второй вход которого соединен с выходом первой схемы сравнения, а прямой и инверсный выходы - с третьими входами третьего и второго элементов И соответственно, прямой выход чет вертого триггера подключен к управляющим входам второй и четвертой схем сравнения. На чертеже представлена функциональная схема устройст за. Устройство содержит регистры 1, 2. 3, 4, узел 5 перезаписи информации, схемы 6, 7, 8, 9 сравнения, элементы 1О, 11 ИЛИ, элемент 12 задержки, элементы 13, 14, 15 ИЛИ, триггеры 16, 17, элементы 18, 19 И, триггер 20, элемент 22 ИЛИ, элементы 21, 23 И, элементы 24, 25 ИЛИ, триггер 26, входные шины 27, 28, 29.. Устройство работает следующим образом. В исходном состоянии все триггеры устанавливаются в О, в регистре 1 записывается заданное число, в остальных регистрах устанавливаются О. Для удобства описания работы устройства рассмотрим поступление на его информационный вход клемму 29 импульсов, например, следующих друг за другом чисел: h-f 70, И -90, tij 140, И ИО, he 120, охватывающих все возможные случаи соотношения как значений, так и последовательности их поступления на вход устройства. При этом пусть в регистре 1 записано заданное число HQ 1ОО. Импульсы первого числа fl подсчитываются в регистре 2, а также через элемент 23 И - в регистре 4. Сигнал окончания поступления импульсов числа поступает черев элемент 19 И на вход узла 5 перезаписи информации, разреишя, таким образом, перезапись содержимого регистра 2 в регистр 3. Через определенную временную задержку сигнал появляется на выходе элемента 12 задержки и устанавливает О в регистре 2. Одновременно этот сигнал через элемент 15 ИЛИ устанавливает триггер 17 в , отключая разрешение на узел 5 перезаписи информации, и через элемент 24 ИЛИ устанавливает триггер 26 в , отключая разрешение на подсчет импульсов в регистре 4. Таким образом, после поступления числа М в регистр 2 устанавливается О, в регистрах 3 и 4 - величина И,. На вход устройства поступают импутгьсы второго чиспа h2 ч поцс;читываются 573 в регистре 2. В тот момент, когда число в регистре 2 окажется равным числу п, записанному в регистр 4, сигнал с выхо да схемы сравнения 8 через элемент 14 ИЛИ установит триггер 17 в О. Одновременно сигнал с выхода схемы 9 сравнения через элемент 25 ИЛИ установит триггер 26 в О. Остальные импульсы второго числа теперь через элемент 23 И подсчитываются в регистре 4, а также продолжают подсчитываться в регистре 2. После окончания поступления импуль сов второго числа открывается элемент 19 И и разрешает перезапись. Далее происходят заключительные операции и переключения, аналогичные описанным, в результате чего врегистре 2 устанавливается О, а в регистрах 3 и 4 записывается ближайшее к заданному h... - 10О число (12 - 90 из двух чисел п 70 и . На вход устройства поступают импульсы третьего числа П и подсчитываются в регистре 2. В тот мЬмент, когда число в регистре 2 окажется равным числу h2, записанному в регистре 4, сигнал с выхода схемы 9 сравнения производит описанные выше переключения. В результате последующие импульсы числа И,, начиная с 91-го, подсчитываются также и в ре- гистре 4. В тот момент, когда число в регистре 2 равно заданному числу Пр,сигнал с выхода схемы сравнения 6 устанавливает триггер 20 в I, осуществив таким образом реверсирование регистра 4. Последующие импульсы числа И, продолжая подсчитываться в регистре 2, вычитаются из содержимого регистра 4. С установкой триггера 20 в единичное состо. яние появляется разрешающий сигнал на входах схем сравнения 7 и 8. В процессе дальнейшего поступления импульсов третьего числа и вычитания их из содержимого регистра 4 в момент, ко,гда число в регистре 4 равно числу в регистре 3i т.е. равно 90, сигнал с выхо да схемы 8 сравнения через элементы 10 и 24 ИЛИ устанавливает триггер 26 в единичное состояние и отключает разре- шение на вычитание импульсов из регистра 4. Одновременно сигнал с выхода схемы 8 сравнения устанавливает триггер 16 в единичное состояние и открывает элемент 18 И. Следующий (111-й) импульс числа проходит через элемент. 18 И и устанавливает через элемент 15 ИЛИ триггер 17 в единичное состояние, .отклю чая разрешение на перезапись. Этот же 8 (111-й) импульс П с выхода элемента 18 И возвращает триггер 16 в исходное состояние. После окончания поступления в схему числа Hj и подачи сигнала управления ре гистр 2 очищен, в регистрах 3 и 4 записано ближайшее к По;Число h,, 90. Далее на вход подаются импульсы четвертого числа. Они подсчитываются в ре-. гистре2,а после наступления момента равенства содержимого регистров 2 к 4 подсчитываются также и в регистре 4, Как и ранее, после момента равенства Ьодержимого регистров 2 и 1 начинается вычитание импульсов из регистра 4. С подсчетом в регистре 2 110-го импульса содержимое в регистре 4 снова становится равным содержимому регистра 3, т.е. равным 90. Так как с прямого выхода триггера 20 имеется разрешающий сигнал на схему 8 сравнения, на ее,выходе появляется сигнал равенства содержимого регистров 3 и 4. Этот сигнал производит описанные выше переключения, однако,поскольку следующий 111-й импульс не по.ступает (Пд :110j, элемент 19 И ocTae-Dся открытым для передачи сигнала на разрешение перезаписи. С приходом этого сигнала содержимое регистра 2 перезаписывается в регистр 3 и затем происходят все описанные ранее заключительные операции и переключения. В результате в регистре 3- записывается, число 110 (ближайшее большее к Vio ) а в регистре 4 - число 90. . Пусть на вход подаются импульсы пятого числа. С подсчетом в регистре 2 90-го ампульса сигнал равенства содержимого регистров 2 и 4 с выхода схемы сравнения 9 устанавливает триггер 17 в О и открывает элемент 19 И для подачи сигнала разрешения на узел 5 перезаписи информации, а также устанавливает триггер 26 в О и открывает элемент 23 И для подсчета импульсов в .регистре 4. Как и ранее, с подсчетом в регистре 2 (а также в 4) 1ОО-го импульса начинается их вычитание из содержимого регистра 4. При этом с установкой триггера 20 в сигнал разрешения сравнения поступает на схему сравнения 7. В момент подсчета в регистре 2 110-го импульса содержимое регистра 2 остановит ся равным содержимому регистра 3. Сигнал с выхода схемы сравнения 7 через элемент 1О ИЛИ и далее так же, как рассмотрено ранее, отключает регистр 4. Этот же сигнал с выхода схемы сравне- 77 ния 7 закрывает элемент 19 И, В резуль тате после подсчета импульсов числа Ид в регистре 2 и подачи сигнала регистр 2 очищается без перезаписи. Таким образом, в регистрах 3 и 4 по-прежнему сохраняются числа НО и 90, ближайшие . Использование предлагаемого изобретения позволяет расширить функциональ™ ные возможности устройства, поскольку при достаточной схемной простоте дает возможность выбрать ближайшее большее ближайшее меньшее число или оба этих числа с записью каждого результата в конкретный регистр. Формул изобретения Устройство для определения числа, бли жайшего к заданному, содержащее регистры, схемы сравнения, элементы ИЛИ, И, триггеры, элемент задержки узел перезаписи информации, причем выходы первого регистра соединены с первой группой входов первой схемы сравнения, вторая группа входов которой соединена с первой груп пой входов второй и третьей схем сравнения и с выходом второго регистра, информационный вход которого подключен к первой входной шине и к первым входам первого, второго и третьего элементов И, установочные входы второго регистра соединены с выходом элемента задержки, вход которого подключен к выходу первого элемента ИЛИ и к первому входу четвертого элемента И, выход которого соединен с первым входом узла перезаписи информации, второй вход которого подключен к выходу второго регистра, а выход - ко входу третьего регистра, выходы которого соединены -со второй группой входов второй схемы сравнения и с первой группой входов четвертой схемы сравнения, выходы второй и четвертой схем сравнения подключены ко входам второго элемента ИЛИ, выход которого соединен с первым входом третьего эелмента ИЛИ, выход которого подключен к первому входу первого триггера, инверсный выход которого соединен со вторыми входами второго и третьего элементов И, выходы которьс; подключены к информационным входам четвертого регистра, выход которого соедийен со вторыми группами входов тре 8 тьей и четвертой схем cpaBneiuiH, отличающееся тем, что, с целью расширения функциональных возможностей в части определения как ближайшего к заданному большего числа, так и ближайшего меньшего из чисел, в нем выход элемента задержки соединен с первыми входами четвертого, пятого и шестого элементов ИЛИ и со вторым входом третьего элемента ИЛИ, вторая входная Ш1ьна подключена к первому входу первого элемента ИЛИ, первому входу седьмого . элемента ИЛИ, второму входу пятого элемента ИЛИ, второму входу шестого элемента ИЛИ, первому входу восьмого элемента ИЛИ и к установочным входам третьего регистра, второй вход первого элемента ИЛИ соединен с третьей входной шиной, выход третьей схемы сравнения подключен ко второму входу седьмого элемента ИЛИ и ко второму входу восьмого элемента ИЛИ, выход которого соединен со вторым 1эходом первого триггера, выход седьмого элемента ИЛИ подключен к первому входу второго триггера, второй вход которого соединен с выходом четвертого элемента ИЛИ, а инверсный выход со вторым входом четвертого элемента И, второй вход четвертого элемента ИЛИ подключен к выходу второй схемы сравнения, а третий вход четвертого элемента ИЛИ соединен с третьим входом пятого элемента ИЛИ и выходом первого элемента И, второй вход которого подключен к выходу третьего триггера, первый вход которого соединен с выходом пятого элемента ИЛИ, а второй вход - с выходом четвертой схемы сравнения, выход шестого элемента ИЛИ подключен к первому входу четвертого триггера, -второй вход которого соединен с выходом первой схемы сравнения, а прямой и инверсный выходы - с третьими входами тре:гьего и второго элементов И соответственно, прямой выход четвертого триггера подключен к управляющим входам второй и четвертой схем сравнения Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 3256О7, кл. G Об F 7/ОО, 07.01.72. 2.Авторское свидетельство СССР № 246924, кл. Q 06 F 7/06,20.06.60 (прототип). г 8,8 f6- 29 0 t

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения числа, ближайшего к заданному | 1981 |

|

SU993248A1 |

| Устройство для определения чисел,ближайших к заданному | 1981 |

|

SU997029A1 |

| Устройство для моделирования деятельности человека-оператора | 1988 |

|

SU1580388A1 |

| Устройство для упорядочивания чисел | 1980 |

|

SU932487A1 |

| Устройство для моделирования деятельности операторов систем человек-машина | 1986 |

|

SU1388888A1 |

| Устройство для упорядочивания чисел | 1981 |

|

SU1012239A1 |

| Устройство для моделирования деятельности человека-оператора | 1986 |

|

SU1377870A1 |

| Устройство для моделирования деятельности человека-оператора | 1986 |

|

SU1399761A1 |

| Устройство для моделирования деятельности человека-оператора | 1987 |

|

SU1413640A1 |

| Устройство для сортировки двоичных чисел | 1984 |

|

SU1182509A1 |

Авторы

Даты

1980-05-05—Публикация

1978-01-05—Подача