00

о

Изобретение относится к вычислительной технике 5 в частности к устройствам для моделирования деятельности человека-оператора системы чел век - мапина.

Цель изобретения - расширение фун- К1даональньгх возможностей устройства за счет моделирования выполнения работ по аварийному алгоритму при BOS- никновении отказов.

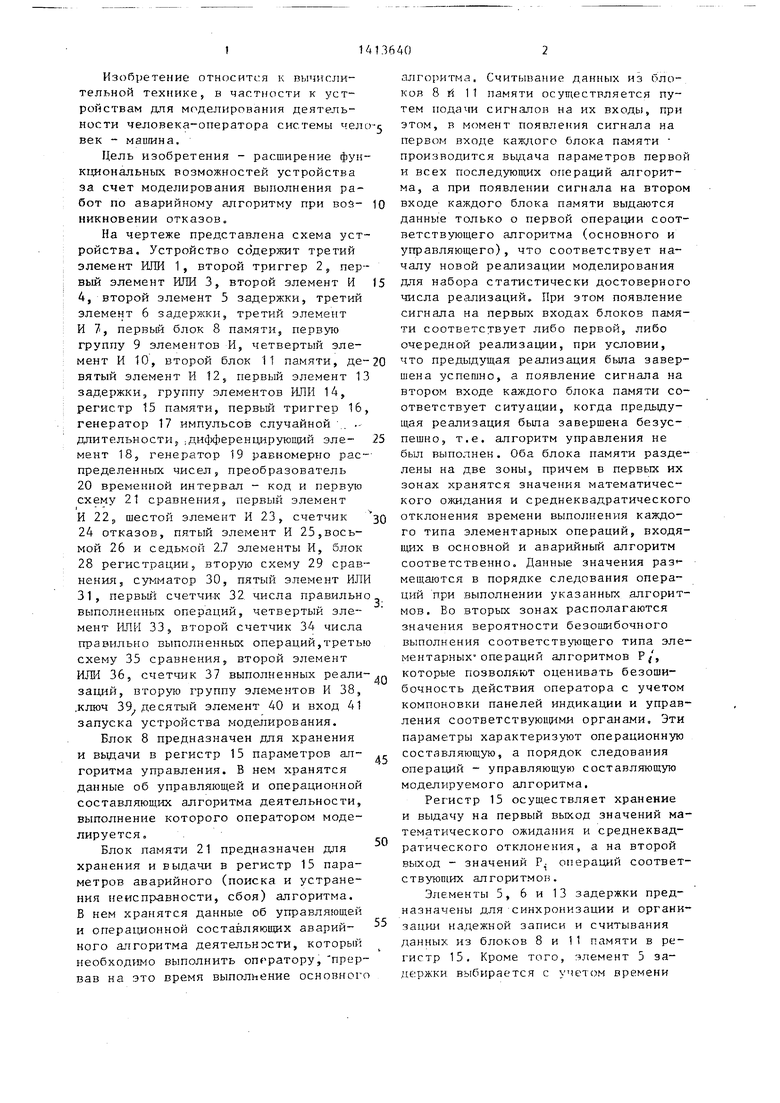

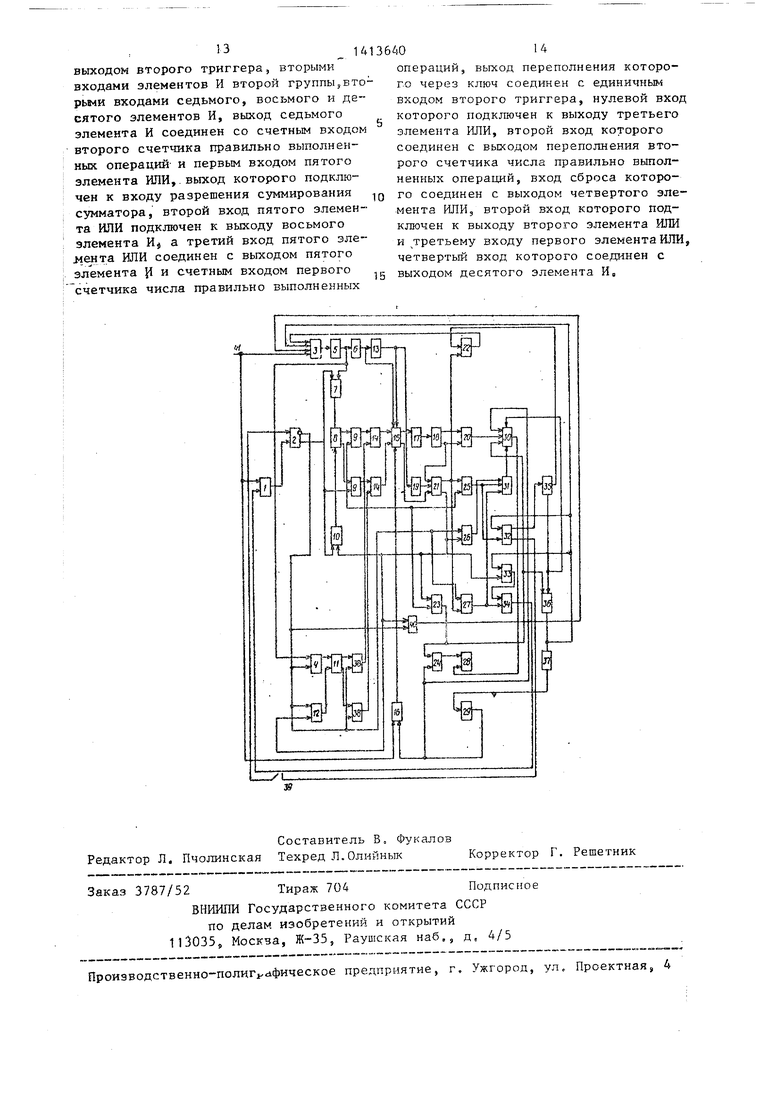

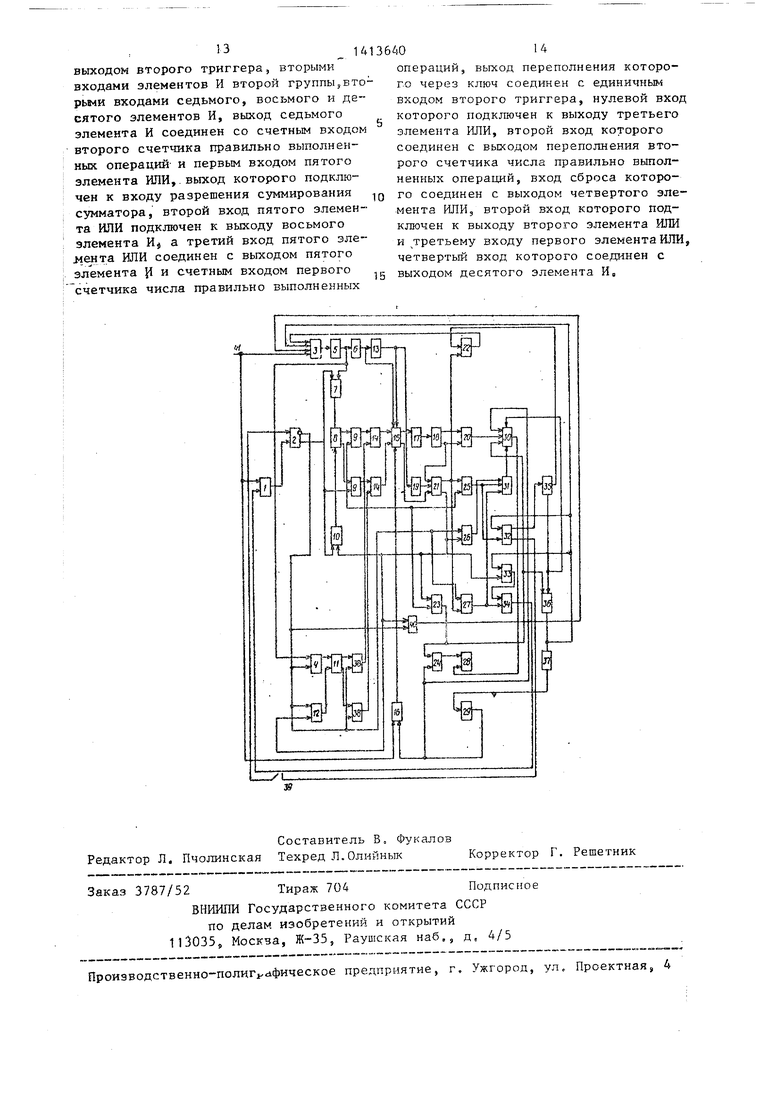

На чертеже представлена схема устройства. Устройство содержит третий элемент HJDi 1, второй триггер 2, первый элемент ИЛИ 3, второй элемент И 4, второй элемент 5 задержки, третий элемент 6 задержки, третий элемент И 7, первый блок 8 памяти, первую группу 9 элементов И, четвертый элемент И 10, второй блок 11 памяти, девятый элемент И 12s первый элемент 13 задержки, группу элементов ИЛИ 14, регистр 15 памяти, первый триггер 16 генератор 17 импульсов случайной .. .- длительностиJ ;Ди4х})еренц -арующий эле- мент 18, генератор 19 равномерно распределенных чисел, преобразователь 20 времен1 ой интервал - код и первую схему 21 сравнения, первый элемент И 22,, шестой элемент И 23, счетчик 24 отказов, пятый элемент И 25,восьмой 26 и седьмой 2.7 элементь И, блок 28 регистрации, вторую схему 29 сравнение , сумматор 30, пятый элемент ИЛИ 31, первый счетчи-к 32, числа правильно выполненных операций, четвертый элемент ИЛИ 33,, второй счетчик 34 числа правильно выполненных операций,третью схему 35 сравнения, второй элемент 36, счетчик 37 выполненных реализаций, вторую группу элементов И 38, .ключ 39 десятый элемент 40 и вход 41 запуска устройства модепирования.

Блок 8 предназначен для хранения и вьщачи в регистр 15 параметров алгоритма управления. В нем хранятся данные об управляющей и операционной составляющих алгоритма деятельности, выполнение которого оператором моделируется.

Блок памяти 21 предназначен для хранения и выдачи в регистр 15 параметров аварийного (поиска и устранения неисправности, сбоя) алгоритма. В нем хранятся данные об управляющей и операционной составляющих аварийного алгоритма деятельности, который необходимо выполнить оператору, прервав на это время выполнение основного

5 0 5 О „

5

0

алгоритма. Считывание данных из блоков 8 и 11 памяти осуществляется путем подачи сигналов на их входы, при этом, в момент появления сигнала на первом входе блока памяти производится вьщача параметров первой и всех последуюпшх операций алгоритма, а при появлении сигнала на втором входе каждого блока памяти выдаются данные только о первой операции соответствующего алгоритма (основного и управляющего), что соответствует началу новой реализации моделирования для набора статистически достоверного числа ре.ализаций. При этом появление сигнала на первых входах блоков памяти соответствует либо первой, либо очередной реализации, при условии, что предыдущая реализация была завершена успешно, а появление сигнала на втором входе каждого блока памяти соответствует ситуации, когда предыдущая реализация была завершена безуспешно, т.е. алгоритм управления не был выполнен. Оба блока памяти разделены на две зоны, причем в первых их зонах хранятся значения математического ожидания и среднеквадратического отклонения времени выполнения каждого типа элементарных операций, входящих в основной и аварийный алгоритм соответственно. Данные значения мещаются в порядке следования операций при выполнении указанных .алгоритмов. Во вторых зонах располагаются значения вероятности безошибочного вьшолнения соответствующего типа элементарных операцир алгоритмов Р/, которые позволяют оценивать безошибочность действия оператора с учетом компоновки панелей индикации и управления соответствующими органами. Эти параметры характеризуют операционную составляющую, а порядок следования операций - управляющую составляющую моделируемого алгоритма.

Регистр 15 осуществляет хранение и выдачу на первый выход значений математического ожидания и среднеквадратического отклонения, а на второй выход - значений Р операций соответ- ствуюп(их алгоритмов.

Элементы 5, 6 и 13 задержки предназначены для синхронизации и организации надежной записи и считывания данных из блоков 8 и 11 памяти в регистр 15. Кроме того, элемент 5 задержки выбирается с учетом времени

срабатывания триггера 2 и времени работы первого счетчика числа правильно выполненных операций при выполнении аварийного алгоритма.

Генератор 17 формирует последовательность импульсов случайной дли- тельности, распределенных по необходимому закону с параметрами, выдаваемыми из первой зоны по первым выходам блоков 8 и 11 памяти.

Генератор 19 равномерно распределенных в интервале (0-1) случайных чисел формирует случайные числа, соответствующие вероятности выполнения оператором элементарной операции алгоритма. Питание на генераторы 17 и 19 подается по сигналу, запускающему функционирование устройства, цепи подачи питания по схеме устройства не показаны.

Дифференцирующий элемент 18 выделяет импульс начала и импульс окончания импульсов случайной длительности, сформированных генератором 17 дл дальнейшего преобразования отрезка времени (длительности импульсов) в код в преобразователе 20 временной и интервал - код.

Сумматор 30 осуществляет суммирование всех значений временных интервалов выполнения операций как за одн так и за все операции алгоритма управления и за все предыдущие его реализации. Если при выполнении алгоритма управления оператором допущена ощибка, т.е. алгоритм управления не выполнен, значения всех предьодущих по данной операции временных затрат в данной реализации стираются и с бе ошибочными реализациями не суммируются,

В схеме 21 сравнения при поступлении импульса Конец от элемента 18 производится сравнение случайного

числа Хр, выработанного ранее по команде с выхода третьего элемента 13 задержки генератором 19,со значением вероятности безошибочного выполнения текущей операции алгоритма, переписанного в схему 27 сравнения выхода регистра 15. В результате сравнения этих чисел определяется безошибочноть выполнения текущей операции алгоритма. Если , то операция считается выполненной правильно. В противном случае фиксируется ошибка и на этом моделирование данной i реализации заканчивается. Подачей

10

15

20

25-

,

4136АО

сигнала на второй вход считывания любого из блоков памяти обеспечивается моделирование очередной реализации с первой операции одного из алгоритмов.

Счетчик 32 подсчитывает число пра-, ВИЛЬНО выполненных операций в основном алгоритме управления для дальнейшего сравнения в схеме 35 сравнения с числом операций, содержащихся в алгоритме управления, что позволяет определить момент окончания выполнения оператором задач и управления и переход к очередной реализации алгоритма. Кроме того, счетчик 32 после того5 как он отсчитает определенное число правютьно выполненных операций алгоритма (это число устанавливается заранее перед моделированием), выдает сигнал на втором этапе исследования на обработку аварийного алгоритма, при этом счетчик отключается и включается в работу только после успешного завершения аварийного алгоритма при переходе оператора к выполнению оставшихся операций основного алгоритма. Этот момент повторяется на втором этапе при каждой новой реализации и может быть розыгргш для лйбой операции основного алгоритма и соответствующего аварийного алгоритма с учетом возникшей ситуации,

Счетчик ЗА подсчитывает количество правильно выполненных операций в аварийном алгоритме. Как только оператор допускает ошибку, в аварийном алгоритме, счетчик ббнуляется и реализация аварийного алгоритма повто - ряется. Число операций аварийного алгоритма устанавливается на счетчик заранее. Как только счетчик отсчитывает необходимое число правильно выполненных операций, он вьщает команду на продолжение выполнения осйов- ного алгоритма управления.

Число операций основного алгорит-; ма управления устанавливается в схеме 35 сравнения перед началом моделирования.

30

35

40

45

Счетчик 37 подсчитывает число проведенных реализаций алгоритма, причем как успешньк,так и ошибочных для схемы 29 сравнения с требуемым числом реализаций. Это число записывается в схему 29 сравнения также перед нача- лом моделирования и определяется ис ,ходя из требуемой точности результа тов моделирования.

Счетчик 24 подсчитывает число ошибок, допущенных при выполнении алгоритма управления (без учета ошибок при выполнении аварийного алгоритма) что соответствует числу безуспешных реализаций, т.е. попыток выполнения алгоритма.

Блок 28 регистрирует по окончании моделирования число безуспешных попыток выполнения алгоритма, т.е. содержимое счетчика 245 а также значение общего времени моделирования всех успешных реализаций алгоритма управления, т.е. содержимое сумматора 30.

Триггер 16 управляет включением и выключением устройства моделирования. Триггер 2 управляет процессом делирования алгоритма управления до возникновения аварийной ситуации и с учетом ее.

Количество элементов в первой . группе элементов И 9, второй группе элементов И 38 и группе элементов ИЛИ 14 соответствует разрядности и коли- честву параметров, храняа ихся в, первом 8 и втором 11 блоках памяти.

Исследование проводится в два этапа: 1) без учета аварийной ситуации до набора необходимой статистики ре- зультатов и 2) исследование и количественная оценка качества деятельности оператора с учетом аварийного алгоритма .

Рассмотрим работу устройства на первом этапе моделирования (ключ 39 в этом случае разомкнут). После подачи на вход 41 устройства сигнала Пуск включаются генераторы 17 и 19, первый из которых подготавливается к формированию последовательности импульсов случайной длительности, а второй - к генерации случайных равномерно распределенных чисел. Кроме того, импульс запуска через первый эле- мент ИЛИ 3 поступает на элемент 5 задержки, время задержки которого ус танавливается в зависимости от времени выхода на заданный режим работы генераторов 17 и 19, Импульс запуска через элемент ИЛИ 1 поступает на единичный вход триггера 2, с прямого выхода которого сигнал поступает на группу элементов И 9, обеспечивая прохождение информации из блока 8 па- мяти в регистр 15 памяти. Сигнал с выхода триггера 2 поступает на элемент И 25 для разрешении передачи сигналов схемы 21 сравкени - на счетчик

32 числа операций, выполненных успешно в основном алгоритме деятельности и на сумматор 30 через четвертый элемент ИЛИ 31. Кроме того, сигнал с прямого выхода триггера 2 поступает на входы элементов И 7 и 10 обеспечивая прохолодение сигналов на блок 8 памяти. Инверсный выход триггера 2 исключает участие в работе устройства блока 1 Г памяти, счетчика 34 посредством закрытия элементов И 4 и 13, а также элементов И 27 и 40. После поступления сигнала с элемента 5 задержки на первый вход считывания блока 8 памяти через открытый элемент И 7 производится считьюание данных из зон в регистр 15 для моделирования выполнения первой операции алгоритма управления. Кроме того, сигнал с элемента 5 задержки поступает на элемент 6 задержки, время задержки которого выбирается исходя из продолжительности перезаписи информации из блока 8 памяти в регистр 15 памяти. Сигнал с элемента 6 задержки поступает на вход элемента 13 задержки и на вход разрешения записи регистра 15. По этому сигналу осуществляется перезапись значений параметров операционной составляющей моделируемой операции в генератор 17 и схему 21 сравнения соответственно. Генератор 17 начинает формирование последовательности импульсов случайной длительности, которые поступают на вход дифферен1шрующего элемента 18, Величина задержки времени элемента 13 задержки обеспечивает надежное считывание информации из регистра 15 памяти. Сигнал Начало с дифференцирующего элемента 18 поступает на вход запуска преобразователя 20 временной интервал - код, а сигнал Конец - на вход останова, формируя код продолжительности временного интервала. Одновременно сигнал Конец дает команду на сравнение в первой схеме 21 сравнения, в которой сравниваются случайное равномерно распределенное число со значением вероятности безошибочного выполнения операции данного такта.Если , операция считается выполненной безошибочно и импульс выхода схемы 21 сравнения поступает на первый вход элемента И 22, При наличии сигнала НсЧ втором его входе, т.е. если не все операции алгоритма управления В1 1полнены, происходит подача этог о сигнала на вход элемента ИЛИ 3 и весь цикл работы устройства (уже для моделирования второй операции алгоритма управления) повторяется. Кроме того, импульс с выхода схемы 21 сравнения поступает на вход сумматора 30. через элемент ИЛИ 31 и на вход счётчика 32 через элемент И 25. Сумматор 30 состоит из двух блоков, в первом подсчитывается время выполнения операции текущей реализации алгоритма, а во втором время предыдущих успешно завершенных реализатдай. Если реализация заверше- на успешно, то время ее моделирования суммируется с содержимым второ- го блока за счет появления сигнала на его втором установочном входе; в противном случае5 т.е. при безуспеш- ной реализации, сигнал на первом установочном входе сумматора 30 обнули- ет содержимое первого блока. С выхода счетчика 32 число успешных операци поступает в схему 35 сравнения, с вы- кода которой снимается постоянный еди ничный сигнал до тех пор, пока не будут выполнены все операции алгоритма управления. Когда все операции алго- ритма будут выполнены успешно, еди- ничный импульс с выхода схемы 35 сравнения поступает через элемент ИЛИ 36 на счетчик 37 для подсчета общего числа проведенных реализаций.-Одновременно сигнал с выхода второго элемента ИЛИ 36 поступает на вход счетчика 32 и обнуляет его содержимое, подготовив его к подсчету числа успешных операций в очередной реализации, а также на вход первого элемента ИЛИ 3 для начала моделирования очередной реализации алгоритма управления и на вход счетчика 34 через элемент ИЛИ 33, обнулив содержимое счетчика 34 и подготовив его к подсчету числа успешных операций в аварийном алгоритме (в случае моделирования деятельности оператора по выполнению алгоритма управления с учетом аварийной ситуации - на втором этапе исследования). С выхода схемы 29 сравнения сигнал на триггер 16 не поступает до тех пор, пока не подсчитано требуемое число реализаций Если при сравнении в схеме 21 сравнения . , операция считается невыполненной, как и весь алгоритм управления в целом. В этом случае сигнал с выхода схемы 21 сравнения поступает на счетчик 24 отказов через

5 0 ,.

5

5

0

oTi CpbiTbul элемент И 23 лля подсчета числа безуспешных рея.т изаций алгоритма управления, на вход элемента lUIH

36для подсчета общего числа реализаций алгоритма управления в счетчике

37числа выполненных реализаций и обнуления счетчиков 32 и 34 через элемент ИЛИ 36. Кроме того, сигнал с выхода элемента И 23 обнуляет содержимое первого блока сумматора времени, затраченного на текущую реал1 зацию алгоритма управления. Сигнал с первого выхода первой схемы 21 сравнения поступает на второй вход считьшания блока 8 памяти через элемент И 10 и обеспечивает выдачу в регистр 15 данных первой операции алгоритма для моделирования очередной его реализации. Когда число реализаций алгоритма управления достигает требуемого числа, сигнал с выхода схемы 29 сравнения поступает на вход счетчика 24 для считывания информацш в блок 28 регистрац, а также на вход считывания сумматора 30, по сигналу которого суммарное время моделирования всех успешных реализаций переписывается также в блок 28 регистрации.

Во втором режиме функционирования устройства моделирования, т.е. с учетом аварийной ситуации, ключ 39 замкнут. Запуск устройства и работа устройства по моделированию выполнения операций, предшествующих той,на ко- торой создается аварийная ситуация, аналогична порядку работы устройства, описанному ранее. Кроме того счетчик 32 отсчитает количество правильно выполненных операций алгоритма управления, он выдает сигнал на вход 2 триггера через замкнутый ключ 39, причем сигнал на второй триггер 2 поступает после окончания моделирования очередной операции. Число правильно выполненных операций, при котором счетчик 32 выдает сигнал на второй триггер 2, устанавливается перед началом второго режима моделирования. С приходом сигнала со счетчика 32 триггер 2 переходит в нулевое состояние, исключая участие в процессе мо- делировЬния первого блока памяти посредством элементов И 7 и 10, сче г- чиков 32 и 24 посредствоя элементов И 25 и 23 соответственно. Кроме того, триггер 2 в новом состоянии обеспечивает участие в процессе моделирования второго блока 11 памяти посредством

элементов И 4 и 12, а также участие счетчика 34 для подсчета количества правильно выполненных операций в аварийном алгоритме посредством элемента И 27. С этого-момента начинается моделирование аварийного алгоритма, вкла- дьшаемого в основной алгоритм управления. Порядок считывания информации происходит с блока 11 памяти аналогична описанному ранее, за исключением работы устройства после схемы 21 сравнения. Так, после правильного выполнения операции аварийного алгоритма сигнал со второго выхода первой схемы 21 сравнения поступает на счетчик 34 числа правильно выполненных операций через элемент К 27 и элемент ИЛИ 31. Все правильно выполненные

: операции аварийного алгоритма подсчи- тьтаются в счетчике 34,, причем время моделирования выполнения операций аварийного алгоритма подсчитывается в сумматоре 30 (как успешных, так и ошибочных реализаций аварийного алгоритма) и входит в общее время моделирования реализации алгоритма управления. Так как счетчик 32 остановился и элемент И 25 закрыт, то. на время моделирования аварийного алгоритма со схемы 35 сравнения сигнал пос.тоянно поступает на элемент И 22,что обеспечивает процесс моделирования всех операций аварийного а тгоритма. Как только счетчик 34 число правильно выполненных операций и количество их будет равно числу операций аварийного алгоритма (это число устанавливается перед моделированием второго этапа), то из счетчика вьщается сигнал на триггер 2 через элемент ИЛИ 1, который прекращает моделирование аварийного алгоритма и

обеспечивает продолжение прерванного процесса моделирования основного алгоритма управления. При этом подготавливается к работе счетчик 32, блок 8 памяти, а также отключается счетчик 38 и блок 11 памяти. Последующая работа продолжается аналогично моделированию алгоритма управления на первом этапе исследования, описанном ранее. Если же во время моделирования аварийного алгоритма операция будет посчитана: вьтолненной неверно, то сигнал с первого выхода схемы 21 сравнения поступает на счетчик 34 через элемент ИЛИ 33 и обнуляет его, подготавливая его к nof ету опера-

ций аварийного алгоритма в новой реализации. Кроме того, сигнал со схемы 21 сравнения поступает на сум- матор 30 через элемент И 26 и элемент HJffl 31, обеспечивая подсчет времени, и на вход считывания второго блока памяти 11 через элемент И 12, обеспечивая выдачу новой реализации

аварийного алгоритма, а также сигнал с первого входа схемы 21 сравнения через открытый элемент И 40 поступает на вход элемента ИЛИ 3 для начала моделирования новой реализации аварийного алгоритма и так до тех пор пока аварийный алгоритм не будет завершен успешно. После правильного выполнения аварийного алгоритма продолжается моделирование основного алгоритма управления

Полученные позволяют оценить известными -методами характеристики качества операторской деятельности с учетом возможных аварийных.

ситуаций. При этом можно моделиро- вать возникновение аварийной ситуации с любой операции основного алгоритма управления и определить для ; каких ситуацш необходим вызов ремонтного персонала, а в каких случаях оператор способен самостоятельно выполнить задачу управления в отведенный временной интервал (норматив).

35

Формула изобретения

Устройство для моделирования деятельности человека-оператора,содержащее первый и второй элементы ИЛИ5первый элемент И, первый, второй и третий элементы задержки, первый блок памяти, регистр памяти, первый триггер, генератор импульсов случайной длительности, дифференцирующий элемент, генератор равномерно распределенных случайных чисел, преобразователь временной интервал - код, первую, вторую и третью схемы сравнения, счетчик отказов, блок регистрации,

сумматор, первый счетчик числа правильно выполненных операций основного алгоритма управления и счетчик числа выполненных реализаций, разрядные выхода которого соединены с инфор- мацион 1ымн входами второй схемы сравнения, выход ксчторой подключен к еди- нич)ому входу первого триггера,входу сброса .счеч чика отказов, входу считывания c мaтc Г , иифсфмационные входы

которого соединены соответственно с выходами преобразователя временной интервал - код, вход запуска которого подключен к первому выходу дифференцирующего элемента, второй выход которого соединен с входом остановки преобразователя, временной интервал - код и входом разрешения сравнения схемы сравнения, информационные входь: первой группы которой соединены соответственно с выходами генератора равномерно распределенных случайных чисел, вход запуска которого связан с выходом первого элемента задержки и входом обнуления регистра памяти,первая группа разрядных выходов которо го подключена к информационным входам генератора импульсов случайной длительности, выход которого подключен к входу дифференцирующего элемента, а вторая группа разрядных выходов регистра памяти соединена соответственно с информационными входами второй группы первой схемы сравнения, выход Меньше или Равно которой подключен к первому входу первого элемента И, выход которого соединен с первым входом первого элемента ИЛИ второй вход первого элемента И подключен к выходу Меньше третьей схемы сравнения, выход Равно которой соединен с первым входом второго элемента ИЛИ и установочным входом сумматора, выход переполнения счетчиков отказов соединен с первым информационным входом блока регистрации, второй информационный вход которого подключен к выходу сумматора, счетньй вход счетчика числа выполненных реализаций соединен с выходом второго

элемента ИЛИ и входом обнуления счетчика числа правильно выполненных операций, первая группа разрядных выходов которого соединена соответственно с информационными входами третьей схемы сравнения, нулевой вход первого триггера является входом запуска устройства и соединен с вторым входом первого элемента ИЛИ, выход которого через второй элемент задержки подключен к входу третьего элемента задержки, выход которого соединен с входом первого элемента задержки и входом считывания регистра памяти, отличающееся тем, что, с целью расширения функциональных возможностей моделирования за счет выполнения работ по аварийному алгоритму при

5

0

5

0

5

0

5

0

5

вспникнопеиии отказов, оно дополнительно содержит первую и вторую груп- ггы элементов И, с пторого по десятый элементы И, третий, четвертый и пятый элементы ШШ, группу элементов ШШ, второй триггер, второй блок па мяти, второй счетчик числа правильно выполненных операц1-1й и ключ, причем первые вход третьего элемента ИЛИ соединен с входом запуска устройстваj пря1-1ой выход первого триггера соединен с входом обнуления регистра памяти, группа разрядных входов которого подключена соответственно к выходам элементов ИЛИ группы, первые входы которых соответственно соединены с выходами элементов И первой группы, вторые входы элементов ИЛИ группы подключены соответственно к выходам элементов И, первые входы которых подключены соответственно к выходам второго блока памяти, первый вход которого подключен к выходу второго элемента И, первый вход которого соединен с выходом второго элемента задержки и первым входом третьего элемента И, выход которого подключен к первому входу считывания первого блока памяти, выходы которого соединены соответственно с первыми входами элементов И первой группы, вторые входы которых объединены и соединены с вторьгм входом третьего элемента И, прямым выходом второго триггера, первым входом четвертого элемента И, первым входом пятого элемента И и первым входом шестого элемента И, второй вход пятого элемента И и первый вход седьмого элемента И подключены к выходу Меньше или Равно первой схемы сравнения, выход Больше которой соединен с первым входом восьмого элемента И, первым входом четвертого элемента ИЛИ, вторым входом четвертого элемента И,вторым входом шестого элемента И, первым входом девятого и десятого элементов И, выход шестого элемента И соединен со счетным входом счетчика отказов, входом обнуления сумматора и вторым входом второго элемента ИЛИ, а выход четвертого элемента И подключен к второму входу считывания первого блока памяти, второй вход считывания второго блока памяти соединен с выходом девятого элемента И, второй вход которого соединен с вторым входом второго элемента И, инверсным

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования деятельности человека-оператора | 1984 |

|

SU1164726A1 |

| Устройство для моделирования деятельности человека-оператора | 1986 |

|

SU1377870A1 |

| Устройство для моделирования деятельности операторов систем человек-машина | 1986 |

|

SU1388888A1 |

| Устройство для моделирования деятельности человека-оператора | 1988 |

|

SU1580388A1 |

| Устройство для моделирования деятельности человека-оператора | 1984 |

|

SU1241254A2 |

| Устройство для моделирования деятельности человека-оператора | 1986 |

|

SU1399761A1 |

| Устройство для моделирования деятельности человека-оператора | 1990 |

|

SU1778761A1 |

| Устройство для моделирования деятельности человека-оператора | 1987 |

|

SU1545226A1 |

| Устройство для моделирования деятельности человека-оператора | 1987 |

|

SU1432553A1 |

| Устройство для обучения операторов | 1991 |

|

SU1765841A1 |

Изобретение относится к вычислительной технике, в частности к устройствам для моделирования деятельности человека-оператора системы человек - мнщина. Цель изобретения расширение функциональных возможностей устройства за счет моделирования выполнения работ по аварийному алгоритму при возникновении отказов Цель изобретения достигается введением в устройство двух групп элементов И, элементов ИЛИ, И, группы элементов ИЛИ, триггера, блока памяти, счетчика числа правильно выполненных операций и ключа. Устройством можно моделировать возникновение аварийной ситуации с любой операцией основного алгоритма управления и определить, для каких ситуаций необходим йызов ремонтного персонала, а в каких случаях оператор способен самостоятельно выполнить задачу управления в отведенный временной интервал (норматив). 1 ил.

| Устройство для моделирования деятельности человека-оператора системы "человек-машина | 1981 |

|

SU966701A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для моделирования деятельности человека-оператора | 1984 |

|

SU1164726A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-07-30—Публикация

1987-01-14—Подача