Изобретение относится к вычислительной технике, в частности к устройствам для моделирования деятельности человека-оператора систем человек-машина (СЧМ).

Цель изобретения - расширение функциональных возможностей устройства за счет определения числа ошибок по каждой моделируемой операции.

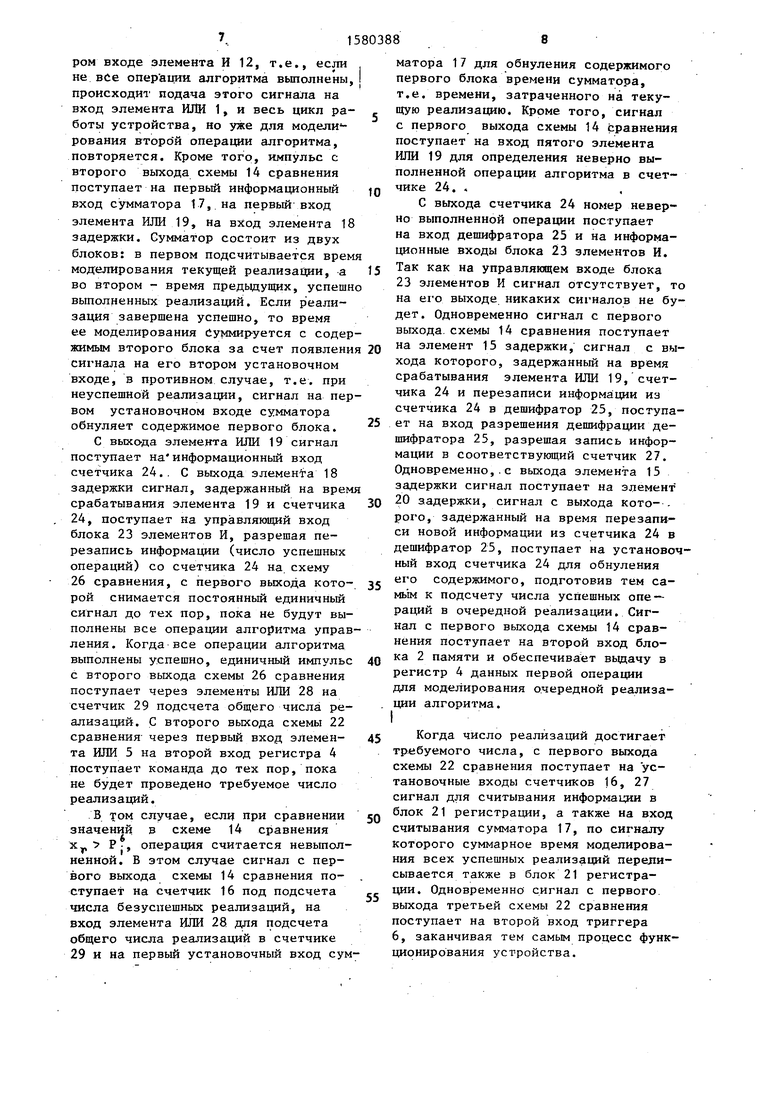

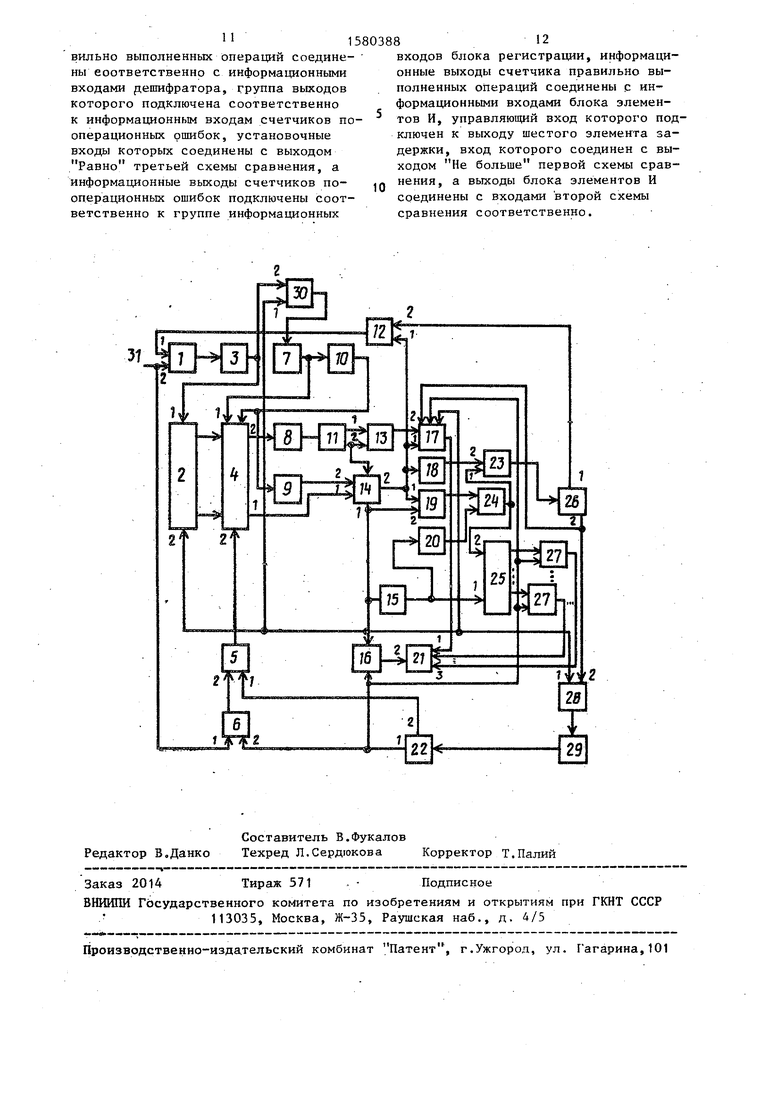

На чертеже представлена схема устройства.

Устройство содержит первый элемент ИЛИ 1, блок 2 памяти, первый элемент 3 задержки, регистр 4 памяти, четвертый элемент ИЛИ 5, триггер 6, второй элемент 7 задержки, ге:

нератор 8 импульсов со случайной длительностью, генератор 9 равномерно распределенных случайных чисел, третий элемент 10 задержки, дифференцирующий элемент 11, элемент И 12, преобразователь 13 временной интервал - код, первую схему 14 сравнения, четвертый элемент 15 задержки, счетчик 16 ошибок, сумматор 17, шестой элемент 18 задержки, пятый элемент ИЛИ 19, пятый элемент 20 задержки, блок 21 регистрации, третью схему 22 сравнения, блок 23 элементов И, счетчик 24 правильно выполненных операций, дешифратор 25, вторую схему 26 сравнения, группу 27 счетчикоз пооперасп

00

о оэ

ас оо

ционных ошибок, третий элемент ИЛИ 28, счетчик 29 выполненных реализаций, второй элемент ИЛИ 30 и вход 31 запуска.Блок 2 памяти предназначен для хранения и ввдачй в регистр 4 параметров алгоритма управления. В нем хранятся данные об управлявдей и операционной составляющих алгоритма деятельности, выполнение которого моделируется. Считывание этих данных осуществляется путем подачи сигналов на его входы, при этом при проявлении сигнала на его первом входе про- изводится выдача параметров первой и всех последующих операций алгоритма, а при появлении сигнала на втором его входе в регистр, выдаются данные только о первой операции алгорит ма, что соответствует началу новой реализации алгоритма при условии,что предыдущая реализация была завершена безуспешно, а значит, оператор не выполнил на этот раз задачи уп- равления.

Блок 2 памяти разделен на две зоны, причем в первой его зоне хранятся значения математического ожидания M(t) и среднеквадратического откло- нения &(t) времени выполнения каждого типа элементарных операций алгоритма. Данные значения размещены в порядке следования операций при выполнении алгоритма управления. Во второй зоне располагаются значения вероятности безошибочного выполнения соответствующего типа элементарных операций алгоритма Р ,-.

Эти параметры характеризуют опера ционную составляющую, а порядок их следования в соответствии с очередностью выполнения элементарных операций - управляющую составляющую моделируемого алгоритма деятельности.

Регистр 4 осуществляет хранение и выдачу на первый выход значения PI соответствующих типов элементарных операций, а на второй выход - значения математического ожидания и дисперсии времени выполнения каждого типа элементарных операций алгоритма .

Элементы 3, 7, 10 задержки предназначены для организации надежной записи и считывания данных из блока 2 памяти в регистр 4. Триггер 6 управляет включением и выключением устройства.

5 0 5

0

Q $

5

Генератор 8 служит для выдачи им- пульсов со случайной длительностью, распределенных по необходимому закону с параметрами, выдаваемыми блоком 2 памяти. Генератор 9 случайных равномерно распределенных в интервале (0-1) чисел вырабатывает значения - этих чисел.

Питание на генераторы 8, 9 подается по сигналу, определяющему начало функционирования устройства, цепи подачи питания на схеме устройства не показаны.

Элемент 11 выделяет импульс на - чала и импульс окончания импульсов, сформированных генератором 8 для дальнейшего преобразования отрезка времени в код, в преобразователе 13.

В схеме 14 сравнения, при поступлении от элемента 11 импульса конец, производится сравнение случайного числа х , выработанного ранее по команде с выхода элемента 10 задержки генератором 9, со значением вероятности безошибочного выполнения операции данного типа Р;, переписанного в схему 14 сравнения с регистра 4. В результате сравнения этих чисел определяется безошибочность выполнения текущей операции алгоритма. В случае, если х Ј Р (, то операция считается выполненной правильно, в противном случае засчитывается ошибка, на этом моделирование данной реализации прекращается . Подачей сигнала на вход блока 2 памяти обеспечивается моделирование очередной реализации первой операции алгоритма.

Элемент 15 задержки предназначен для организации надежной перезаписи информации из счетчика 24 в дешифра- 25 и надежного ее считывания на соответствующие счетчики 27 пооперационных ошибок.

Счетчик 16 подсчитывает число ошибок, допущенных при выполнении алгоритма, что соответствует числу без- успешных реализаций, т.е. попыток выполнения алгоритма.

Сумматор 17 осуществляет суммирование всех значений временных интервалов выполнения операций как за одну, так и за все операции алгоритма и за все успешные его реализации. При этом в случае, если при выполнении алгоритма оператором допущена ошибка, т.е. алгоритм не выполнен, значения всех предыдущих до данной операции временных затрат стираются и с безошибочными реализациями не суммируются.

Элемент 18 задержки предназначен для организации надежной перезаписи информа-ции из счетчика 24 на схему 26 сравнения. Элемент 20 задержки предназначен для организации надежной перезаписи новой информации из счетчика 24 в. дешифратор 25 и его обнуления.

Блок 21 по окончании моделирования регистрирует число безуспешных попыток выполнения алгоритма, т.е. содержимое счетчика 16, значение общего времени моделирования всех успешных реализаций алгоритма, т.е. содержимое сумматора, а также число ошибок по каждой операции, которые приводят к невыполнению алгоритма управления в целом, т.е. содержимое счетчиков 27 пооперационных ошибок.

Счетчик 24 подсчитывает число правильно выполненных операций для дальнейшего сравнения в схеме 26 сравнения с числом операций, содержащихся в алгоритме управления, что по- зволяет определить момент завершения выполнения задачи управления оператором и переход к новой ее реализации. Кроме того, при неверно выполненной операции счетчик 24 совместно с дешифратором 25 формирует адрес счетчика 27 фиксации неверно выполненной операции. Число операций моделируемого алгоритма устанавливается в схеме 26 сравнения перед началом моделирования.

Счетчики 27 подсчитывают число ошибок по каждой операции моделируемого алгоритма. Количество счетчиков определяется числом операций в алгоритме.

Счетчик 29 подсчитывает число проведенных реализаций, причем как успешных, так и ошибочных для сравнения в схеме 22 сравнения с требуемым числом реализаций. Это число записывается в схему 22 сравнения также перед началом моделирования и определяется исходя из требуемой точности результатов моделирования.

Устройство функционирует следующим образом.

Перед началом работы устройство находится в исходном состоянии: все счетчики, сумматор, триггер, регистры установлены в исходные состоя

5

0

5

ния, обнуляются сигналом, выработанным при подаче питания.

После подачи сигнала1 Пуск на вход 31 устройства включаются генераторы 8 и 9, первый из которых подготавливается к формированию последовательности случайного числа импульсов, а второй - к генерации случайных, равномерно распределенных чисел. Кроме того, импульс запуска через элемент ИЛИ 1 поступает на элемент 3 задержки, время задержки которого устанавливается в зависимости от выхода на заданный режим работы генераторов 8 и 9.

После поступления сигнала с выхода элемента 3 задержки на вход блока 2 памяти производится считывание данных из его обеих зон в регистр 4 для моделирования выполнения первой операции. Кроме того, сигнал с элемента 3 через элемент ИЛИ 30 поступает на элемент 7 задержки, время задержки которого выбирается исходя из продолжительности перезаписи информации из блока 2 в регистр 4. Сигнал с выхода элемента 7 задержки поступает на вход элемента 10 задержки и на вход разрешения считывания регистра 4. По этому .сигналу осуществляется перезапись значений параметров моделируемой операции в генератор 8 и схему 14 сравнения соответственно. Генератор 8 начинает формирование последовательности импульсов, которые поступают на вход элемента 11. Величина задержки времени элемента 10 обеспечивает надежное считывание информации из регистра 4. При поступлении сигнала с выхода элемента 10 на установочный вход регистра 4 памяти производится обнуление регистров.

Сигнал Начало с элемента 11 поступает на один вход преобразователя 13 временной интервал - код, а сигнал Конец - на другой его вход, формируя код продолжительности временного интервала. Одновременно сиг0 нал Конец дает команду на сравнение в схеме 14 сравнения. В ней сравнивается случайное равномерно распределенное число со значением вероятности безошибочного выполнения опера-

Ции данного типа. В том случае, если операция выполнена безошибочно, импульс с второго выхода схемы 14 сравнения поступает на вход элемента И 12. При наличии сигнала на вто0

5

0

5

ром входе элемента И 12, т.е., если не все операции алгоритма выполнены, происходит подача этого сигнала на вход элемента ИЛИ 1, и весь цикл ра- боты устройства, но уже для модели4- рования второ й операции алгоритма, повторяется. Кроме того, импульс с второго выхода схемы 14 сравнения поступает на первый информационный вход сумматора 17, на первый вход элемента ИЛИ 19, на вход элемента 18 задержки. Сумматор состоит из двух блоков: в первом подсчитывается врем моделирования текущей реализации, а во втором - время предыдущих, успешн выполненных реализаций. Если реализация завершена успешно, то время ее моделирования суммируется с содержимым второго блока за счет появлени сигнала на его втором установочном входе, в противном случае, т.е. при неуспешной реализации, сигнал на первом установочном входе сумматора обнуляет содержимое первого блока.

С выхода элемента ИЛИ 19 сигнал поступает на информационный вход счетчика 24. С выхода элемента 18 задержки сигнал, задержанный на врем срабатывания элемента 19 и счетчика 24, поступает на управляющий вход блока 23 элементов И, разрешая перезапись информации (число успешных операций) со счетчика 24 на схему 26 сравнения, с первого выхода кото- рой снимается постоянный единичный сигнал до тех пор, пока не будут выполнены все операции алгоритма управления . Когда все операции алгоритма выполнены успешно, единичный импульс с второго выхода схемы 26 сравнения поступает через элементы ИЛИ 28 на счетчик 29 подсчета общего числа реализаций. С второго выхода схемы 22 сравнения через первый вход элемен- та ИЛИ 5 на второй вход регистра 4 поступает команда до тех пор, пока не будет проведено требуемое число реализаций.

В том случае, если при сравнении значений в схеме 14 сравнения х Р-, операция считается невыполненной. В этом случае сигнал с первого выхода схемы 14 сравнения по- ступает на счетчик 16 под подсчета числа безуспешных реализаций, на вход элемента ИЛИ 28 для подсчета общего числа реализаций в счетчике 29 и на первый установочный вход сум5

5 0

0 5 0 5

0

матора 17 для обнуления содержимого первого блока времени сумматора, т.е. времени, затраченного на текущую реализацию. Кроме того, сигнал с первого выхода схемы 14 сравнения поступает на вход пятого элемента ИЛИ 19 для определения неверно выполненной операции алгоритма в счетчике 24. «

С выхода счетчика 24 номер неверно выполненной операции поступает на вход дешифратора 25 и на информационные входы блока 23 элементов И. Так как на управляющем входе блока 23 элементов И сигнал отсутствует, то на его выходе никаких сигналов не будет. Одновременно сигнал с первого выхода схемы 14 сравнения поступает на элемент 15 задержки, сигнал с выхода которого, задержанный на время срабатывания элемента ИЛИ 19, счетчика 24 и перезаписи информации из счетчика 24 в дешифратор 25, поступает на вход разрешения дешифрации дешифратора 25, разрешая запись информации в соответствующий счетчик 27. Одновременно, с выхода элемента 15 задержки сигнал поступает на элемент 20 задержки, сигнал с выхода кото- - рого, задержанный на время перезаписи новой информации из счетчика 24 в дешифратор 25, поступает на установочный вход счетчика 24 для обнуления его содержимого, подготовив тем самым к подсчету числа успешных one- раций в очередной реализации. Сигнал с первого выхода схемы 14 сравнения поступает на второй вход блока 2 памяти и обеспечивает выдачу в регистр 4 данных первой операции для моделирования очередной реализации алгоритма. I

Когда число реализаций достигает требуемого числа, с первого выхода схемы 22 сравнения поступает на установочные входы счетчиков 16, 27 сигнал для считывания информации в блок 21 регистрации, а также на вход считывания сумматора 17, по сигналу которого суммарное время моделирования всех успешных реализаций переписывается также в блок 21 регистрации. Одновременно сигнал с первого выхода третьей схемы 22 сравнения поступает на второй вход триггера 6, заканчивая тем самым процесс функционирования устройства.

Формула изобретения

Устройство для моделирования деятельности человека-оператора, содержащее блок памяти, выходы которого подключены соответственно к разрядным входам регистра памяти, последовательно соединенные первый элемент ИЛИ и первый элемент задержки, последовательно соединенные второй элемент задержки и третий элемент задержки, сумматор, счетчик ошибок, элемент И, счетчик правильно выполненных операций, триггер,единичный вход которого является входом запуска устройства, три схемы сравнения, счетчик выполненных реализаций,блок регистрации, генератор равномерно распределенных случайных чисел, второй, третий и четвертый элементы ИЛИ, генератор импульсов со случайной длительностью, дифференцирующий элемент и преобразователь временной интервал - код, первый и второй информационные входы первой схемы сравнения подключены соответственно к первому.информационному выходу регистра памяти и выходу генератора равномерно распределенных случайных чисел, вход запуска которого и установочный вход регистра памяти соединены с выходом третьего элемента задержки, выход второго элемента задержки подключен к первому входу разрешения считывания регистра памяти, первый и второй входы второго элемента ИЛИ соответственно соединены с выходом Больше первой схемы сравнения и выходом первого элемента задержки, выход которого соединен также с первым входом разрешения считывания блока памяти, второй вход разрешения считывания которого подключен к выходу Больше первой схемы сравнения, к информационному входу счетчика ошибок, к первому входу третьего элемента ИЛИ и к первому установочному входу сумматора, первый информационный вход которого соединен с.выходом Не больше первой схемы сравнения и первым входом элемента И, второй вход которого подключен к выходу Меньше второй схемы сравнения, а выход элемента И соединен с первым входом первого элемента ИЛИ, второй вход которого подключен к входу запуска устройства, нулевой вход триггера соединен с установоч0

5

0

5

0

5

ным входом счетчика ошибок, с входом считывания сумматора и с выходом Равно третьей схемы сравнения, выход Меньше которой подключен к | первому входу четвертого элемента ИЛИ, вторым входом соединенного с прямым выходом триггера, а выход четвертого элемента ИЛИ подключен к второму входу разрешения считывания регистра памяти, выход Равно второй схемы сравнения подключен к второму установочному входу сумматора и второму входу третьего элемента ИЛИ, выход которого соединен со счетным входом счетчика выполненных реал изаций7выход переполнения кото- ро го подключён к информационному входу третьей схемы сравнения, второй информационный выход регистра памяти соединен с входом генератора импульсов со случайной длительностью, выход которого подключен к входу дифференцирующего элемента, первый выход которого соединен с входом запуска преобразователя временной интервал - код, а второй выход - с входом разрешения сравнения первой схемы сравнения и с входом останова преобразователя временной интервал - код, выход которого подключен к второму информационному входу сумматора, выход которого соединен с первым информационным входом блока регистрации, второй информационный вход которого под- ключей к выходу счетчика ошибок, о т5

0

5

лью расширения функциональных возможностей устройства за счет определе- ния числа ошибок по каждой моделируемой операции, оно дополнительно содержит четвертый, пятый и шестой элементы задержки, пятый элемент ИЛИ, блок элементов И, дешифратор и группу счетчиков пооперационных ошибок, причем первый вход пятого элемента ИЛИ подключен к выходу Не больше первой схемы сравнения, выход Больше которой соединен с вторым вхо- я дом пятого элемента ИЛИ и с входом четвертого элемента задержки, выход которого подключен к входу разрешения работы дешифратора и к входу пятого элемента задержки, выход которого соединен с установочным входом счетчика правильно выполненных операций, информационный вход которого подключен к выходу пятого элемента ИЛИ, а информационные выходы счетчика пра11

1580388

вильно выполненных операций соединены соответственно с информационными входами дешифратора, группа выходов которого подключена соответственно к информационным входам счетчиков пооперационных ошибок, установочные входы которых соединены с выходом Равно третьей схемы сравнения, а информационные выходы счетчиков пооперационных ошибок подключены соответственно к группе информационных

12

входов блока регистрации, информационные выходы счетчика правильно выполненных операций соединены с информационными входами блока элементов И, управляющий вход которого подключен к выходу шестого элемента задержки, вход которого соединен с выходом Не больше первой схемы сравнения, а выходы блока элементов И соединены с входами второй схемы сравнения соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования деятельности человека-оператора | 1984 |

|

SU1164726A1 |

| Устройство для моделирования деятельности человека-оператора | 1986 |

|

SU1399761A1 |

| Устройство для моделирования деятельности человека-оператора | 1987 |

|

SU1545226A1 |

| Устройство для моделирования деятельности человека-оператора | 1990 |

|

SU1778761A1 |

| Устройство для моделирования деятельности операторов систем человек-машина | 1986 |

|

SU1388888A1 |

| Устройство для моделирования деятельности человека-оператора | 1986 |

|

SU1377870A1 |

| Устройство для моделирования деятельности человека-оператора | 1987 |

|

SU1432553A1 |

| Устройство для моделирования деятельности человека-оператора | 1987 |

|

SU1413640A1 |

| Устройство для моделирования деятельности человека-оператора | 1984 |

|

SU1241254A2 |

| Устройство для обучения операторов | 1989 |

|

SU1695363A1 |

Изобретение относится к специализированным средствам вычислительной техники. Цель изобретения - расширение функциональных возможностей устройства за счет определения числа ошибок по каждой моделируемой операции. Устройство содержит блок памяти, регистр памяти, четыре элемента ИЛИ, три элемента задержки, сумматор, счетчик ошибок, элемент И, счетчик правильно выполненных операций, триггер, три схемы сравнения, счетчик выполненных реализаций, блок регистрации, генератор равномерно распределенных случайных чисел, генератор импульсов со случайной длительностью, дифференцирующий элемент и преобразователь временной интервал - код. Введение четвертого, пятого и шестого элементов задержки, пятого элемента ИЛИ, блока элементов И, дешифратора и группы счетчиков пооперационных оибок позволяет расширить функциональные возможности устройства за счет получения новых результатов моделирования, в частности количества ошибок, допущенных при выполнении каждой операции алгоритма управления. 1 ил.

7uv2

| Устройство для моделирования деятельности человека-оператора систем "человек-машина | 1982 |

|

SU1053109A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Тренажер операторов автоматизированных систем управления | 1984 |

|

SU1203571A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-07-23—Публикация

1988-11-22—Подача