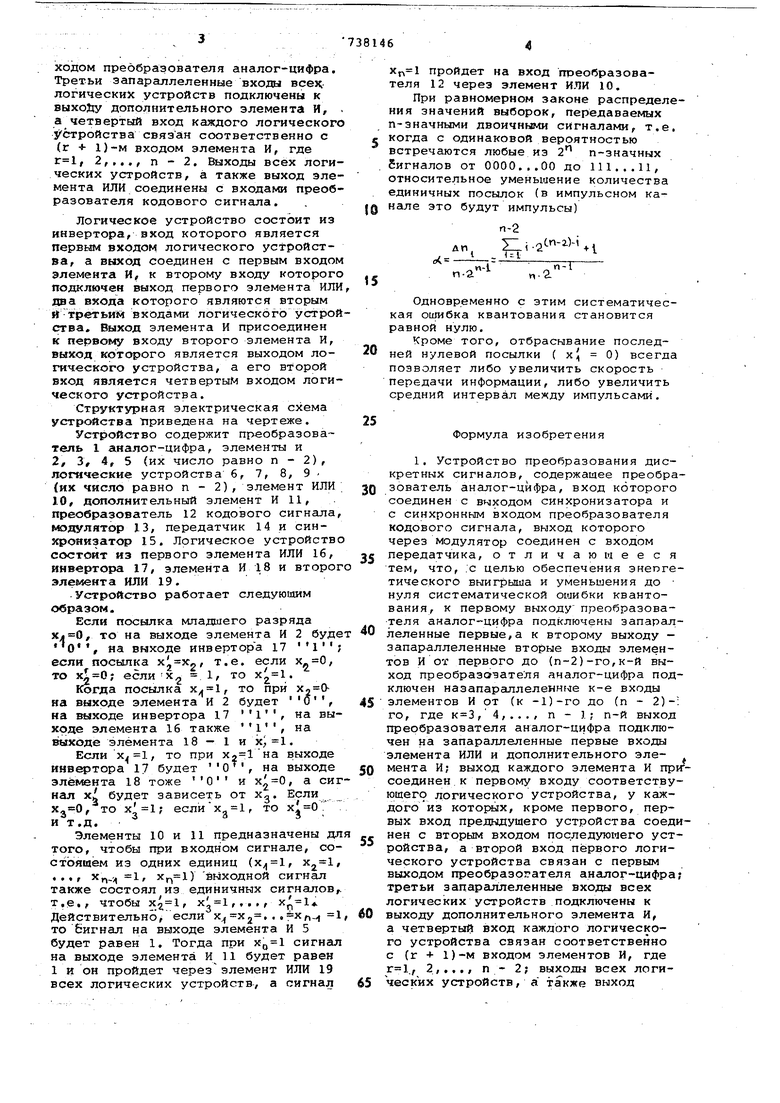

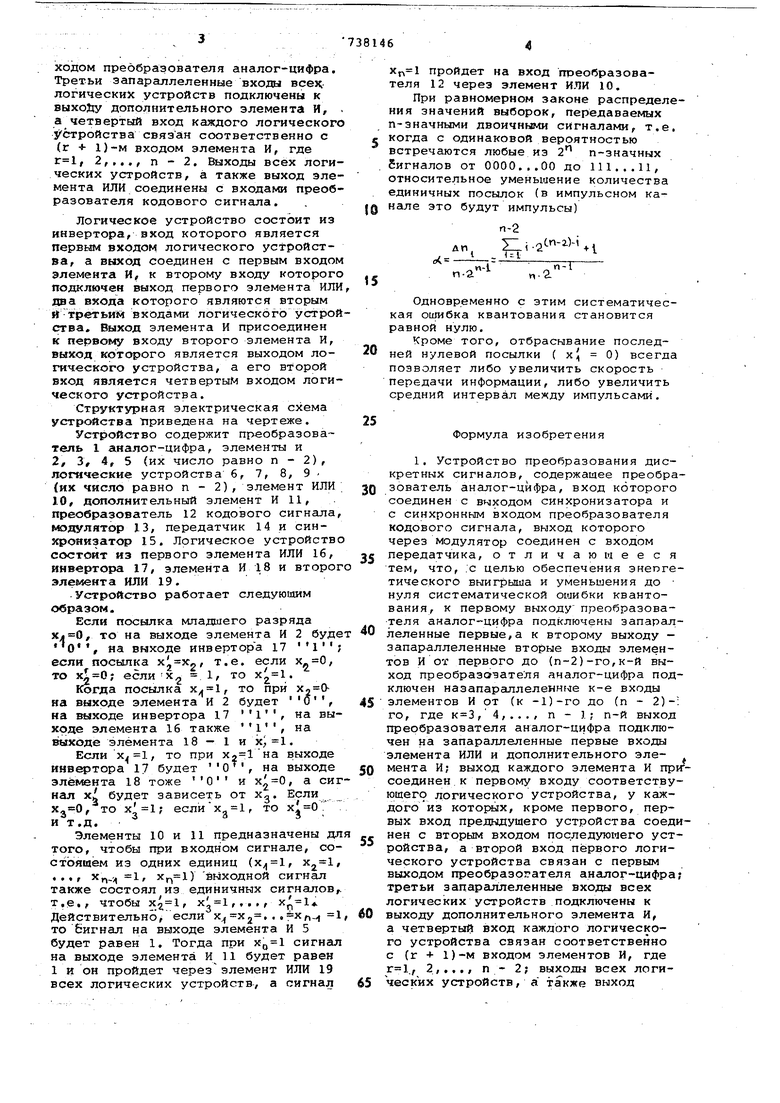

(54) УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЖ)В Изобретение относится к телеметрии связи. Известно устройство преобразования дискретных, сигналов, позволяюиее каждую выборку представить в виде п-значного двоичного сигнала, содержащее коммутатор каналов, преобразователь аналог - цифра, накопитель преобразователь кода и передатчик Г Недостатком этого устройства является то, что при передаче цифровых сигналов простым двоичным кодом при равномерном законе распределения значений выборок исходных сообшений на каждую выборку в среднем единичных посылок, Известно устройство преобразования дискретных сигналов, содержашее преобразователь аналог-цифра, соединенный через анализатор качества посылок с триггером, синхронизатором, выходы которого соединены с синхронньв«1 входами преобразователя аналог-код, триггера и синхронизатора 2 . Недостатком устройства является необходимость применения на приемно стороне преобразователя сигналов и сложной схемы символьной синхрониза ции. Цель изобретения - обеспечение энергетического выигрыша н уменьшения до нуля .систематической ошибки квантования. Указанная цель достигается тем, что в устройство преобразования дискретных сигналов, содержащее преобразователь аналог-цифра, синхронизатор, преобразователь кодового сигнала, передатчик,к первому выходу преобразователя аналог-цифра подк.пючены запараллеленные первые, а к второму выходу - запараллеленные вторые входы элементов И от первого до (fii - 2)-го, к-й выход преобразовате.пя аналог-цифра подключен на запарал|Лелённые к-е входы элекГентов И ог (к - 1)-го до (п - 2)-го, где к 3, 4,..., п - 1; п-Й выход преобразователя аналог-цифра подключен иа запараллельные первые входы элемента ИЛИ и дополнительного элемента И, Выход кадсдого элемента И присоедй1нея кйервому входу соответстзуюшвго логического устройства, у каждого из которых, кроме первого, первый вход предыдущего устройства соединен с оторым входом последующего устрбйст на, а второй вход первого логического устройства Связанс первым выходом преобразователя аналог-цифра. Третьи запараллеленные входы всек логических устройств подключены к BHxoJiy дополнительного элемента И, а четвертый вход каждого логическог Устройства свяэан соответственно с (г + 1)-м входом элемента И, где , 2,,.,, п - 2. Выходы всех логи ческих устройств, а также выход эле мента ИЛИ соединены с входами преоб разователя кодового сигнала. Логическое устройство состоит из инвертора, вход которого является первым входом логического устройства, а выход соединен с первым входом элемента И, к второму входу которого подключен выход первого элемента ИЛИ два вкода которого являются вторым й-третьим входами логическогО устрой ства. Выход элемента И присоединен к первому входу второго элемента И, выход которого является выходом логического устройства, а его второй вход является четвертым входом логического устройства. Структурная электрическая схема устройства приведена на чертеже. Устройство содержит преобразователь 1 аналог-цифра, элементы и 2, 3, 4, 5 их число равно п - 2), логические устройства 6, 7, 8, 9 (их число равно п - 2), элемент ИЛИ 10, дополнительный элемент И 11, преобразователь 12 кодового сигнала модулятор 13, передатчик 14 и синхронизатор 15. Логическое устройств ссхгтойт из первого элемента ИЛИ 16, инвертора 17, элемента И 18 и второг элемента ИЛИ 19. Устройство работает следующим образом. Если посылка младшего разряда , то на выходе элемента И 2 буде , на выходе инвертора 17 если посылка , т.е. если , то 1, то . Когда посылка х 1, то при Xj Oвыходе элемента И 2 будет О, на выходе инвертора 17 , на выходе элемента 16 также , на выходе элемента 18 - 1 и Х; 1. Еслих 1, то при выходе -1 1 Ктгт-глгтч Я tJl,TVr4TT S инвертора17 будет О , на выходе и , а сиг элемента 18 тоже О нал х будет зависеть от Хд. Если , то еслйХд 1, то . и т.д. Элементы 10 и 11 предназначены дл того, чтобы при входном сигнале, состоящем из одних единиц (х,1, Х2,1, .«, х,.. 1, Хг)1) выходной сигнал также состоял из единичных сигналов, т.е., чтобы xji l, ,. . ,, . Действительно, если ...Хо 1 то бигнал на выходе элемента И 5 будет равен 1. Тогда при сигнал на выходе элемента И 11 будет равен 1 и он пройдет черезэлемент ИЛИ 19 всех логических устройств, а сигнал пройдет на вход преобразователя 12 через элемент ИЛИ 10. При равномерном законе распределения значений выборок, передаваемых п-значными двоичными сигналами, т.е. когда с одинаковой вероятностью встречаются любые из 2 п-значных 5игналов от 0000...00 до 111... 11, относительное уменьшение количества единичных посылок (в импульсном канале это будут импульсы) дп . п-1 Одновременно с этим систематическая ошибка квантования становится равной нулю. Кроме того, отбрасывание последней нулевой посылки ( xij 0) всегда позволяет либо увеличить скорость передачи информации, либо увеличить средний интервал между импульсами. Формула изобретения 1. Устройство преобразования дискретных сигналов, содержащее преобразователь аналог-цифра, вход которого соединен с выходом синхронизатора и с синхронным входом преобразователя кодового сигнала, выход которого через модулятор соединен с входом передатчика, отличающееся тем, что, .с целью обеспечения энепгетического выигрыша и уменьшения до нуля систематической ошибки квантования, к первому выходу преобразователя аналог-цифра подключены запараллеленные первые,а к второму выходу - запараллеленные вторые входы элементов И от первого до (п-2)-го,к-й выход преобразователя аналог-цифра подключен назапараллеленнке к-е входы элементов И от (к -1)-го до (п - 2)-; го, где к 3, 4, .. . , п - 1; п-й выход преобразователя аналог-цифра подключен на запараллеленные первые входы элемента ИЛИ и дополнительного элемента И; выход каждого элемента И при соединен к первому входу соответствующего логического устройства, у каждого из которых, кроме первого, первых вход предыдущего устройства соединен с вторым входом последующего устройства, а второй вход первого логического устройства связан с первым выходом преобразрг-ателя ангшог-цифра; третьи запараллеленные входы всех логических устройств подключены к выходу дополнительного элемента И, а четвертый вход каждого логического устройства связан соответственно с (г + 1)-м входом элементов И, где ., 2,..., п - 2; выходы всех логических устройств, а выход

| название | год | авторы | номер документа |

|---|---|---|---|

| Система передачи и приема сообщений | 1977 |

|

SU734781A1 |

| Система передачи и приема информации с коррекцией ошибок | 1982 |

|

SU1078653A1 |

| Устройство для передачи информации | 1978 |

|

SU743220A1 |

| УСТРОЙСТВО ШИРОКОПОЛОСНОЙ РАДИОСВЯЗИ ШУМОПОДОБНЫМИ СИГНАЛАМИ | 1982 |

|

SU1840540A1 |

| Цифровая система передачи и приема информации с обнаружением ошибок | 1982 |

|

SU1123111A1 |

| Устройство для передачи сигналов приращений | 1981 |

|

SU955163A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

| Устройство для передачи информации с контролем ошибок высокой кратности | 1987 |

|

SU1480129A1 |

| ПЕРЕДАТЧИК СИГНАЛОВ ТИПА ЧАСТОТНО-ВРЕМЕННОЙ МАТРИЦЫ | 1996 |

|

RU2109406C1 |

| Цифровая система связи с исправле-НиЕМ ОшибОК | 1979 |

|

SU818024A1 |

Авторы

Даты

1980-05-30—Публикация

1977-05-25—Подача