1

Изобретение относится к радиотехнике и Может быть использовано в радиосвязи, радиотелеметрии, радиоуправлении и т. д.

Известны устройства для формирования импульсных кодов псевдослучайных последовательностей, характеризующиеся большим количеством аппаратуры 1.

Наиболее близким к данному техническому решению является устройство, содержащее шифрующую матрицу с (P-f-I) входами, регистр сдвига, состоящий из последовательно соединенных элементов памяти с раздельными входами «запись, соединенными с выходами шифрующей матрицы, синхронизатор, первый выход Kotoporo соединен со входом регистра сдвига,и формирователь импульсов 2.,.

Однако недостатком известного устройства является то, что при увеличении числа 2 разрядов формируемых кодов аппаратуры затраты увеличиваются в прямой зависимости от числа разрядов (например число элементов памяти сдвигающего регистра) или в квадратичной зависимости (например сложность шифрующей матрицы).

Целью изобретения является сокращение аппаратурных затрат при увеличении числа 2 разрядов формируемых кодов.

Поставленная цель достигается тем, что устройство, для формирования импульсов кодов псевдослучайных последовательностей дополнительно содержит второй регистр сдви га, состоящий из К последовательно соединенных элементов памяти, вход которого подключен.к выходу первого регистра сдви10га, состоящего из (N-bm-bl) элементов памяти, сумматор по модулю два, выход которого соединен со входом регистра сдвига, а входы которого соединены с выходами (N+1) элементов памяти первого регистра сдвига, (N-bm-|-k-|-1) элементов И на два

15 входа, первые из которых соединены с выходами элементов памяти регистров сдвига, элемент ИЛИ, (N-|-m + ) входов которого соединены с выходами элементов И, а выход соединен с входом формирователя

20 импульсов, и блок опроса, выходы которого соединены со входами (N-bm + k-i-1) элементов И, а входы блока опроса подключены к первому и второму выходам синхронизатора.

При этом блок опроса содержит декодирующую матрицу, двоичный реверсивный счетчик, делитель синхрочастоты на два, два элемента И и генератор М-последовательности, состоящий из (N + 1) последовательно соединенных элементов памяти с раздельными входами «запись и сумматора по модулю два, причем в блоке опроса (N -f m + + k -f 1) выходов декодирующей матрицы соединены с выходными шинами блока опроса, выходы реверсивного счетчика соединены со входами декодирующей матрицы, два входа первого элемента И соединены с прямыми, а два входа второго элемента И соединены с инверсными выходами N-ro и (N+l)-ro элементов памяти генератора М-последовательности соответственно, выход первого элемента И соединен с суммирующим, а выход второго элемента И соединен с вычитающим входами реверсивного счетчика, причем управляющий вход декодирующей матрицы через делитель синхрочастоты на два, третьи входы двух элементов И через элемент задержки, а управляющий вход генератора М-последовательности непосредственно соединены со второй входной щиной блока опроса, управляющий вход реверсивного счетчика и входы «запись генератора М-последовательности соединены

с первой входной щиной блока опроса.

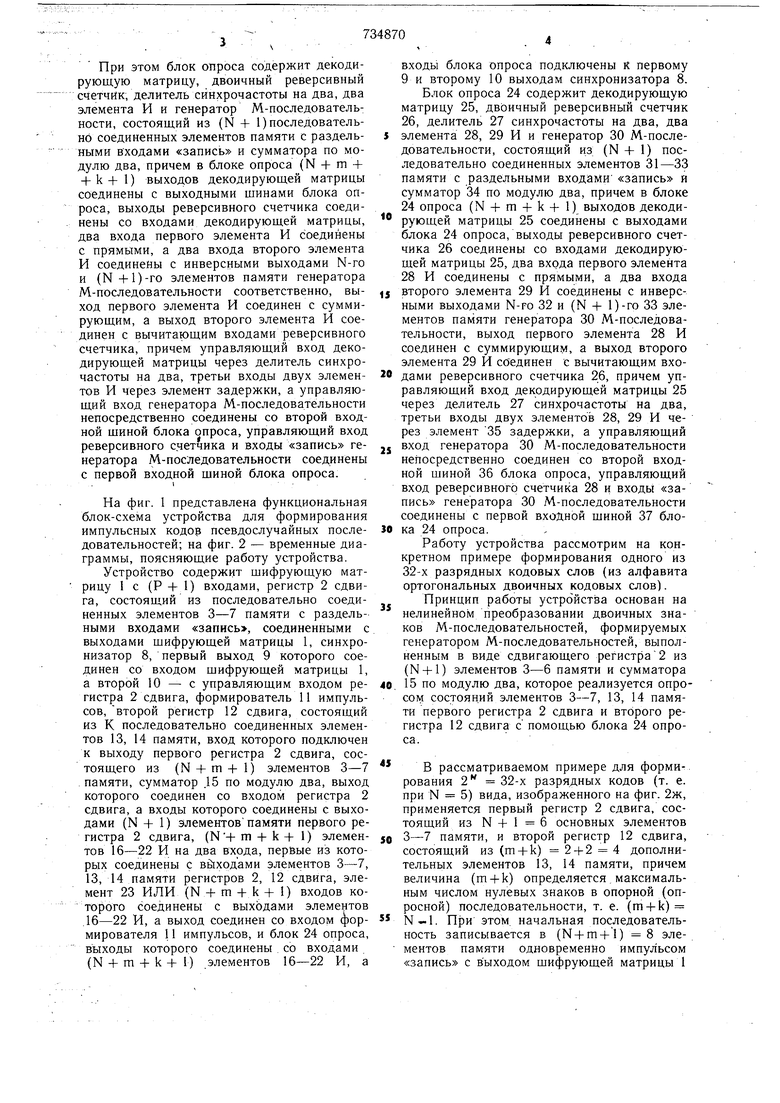

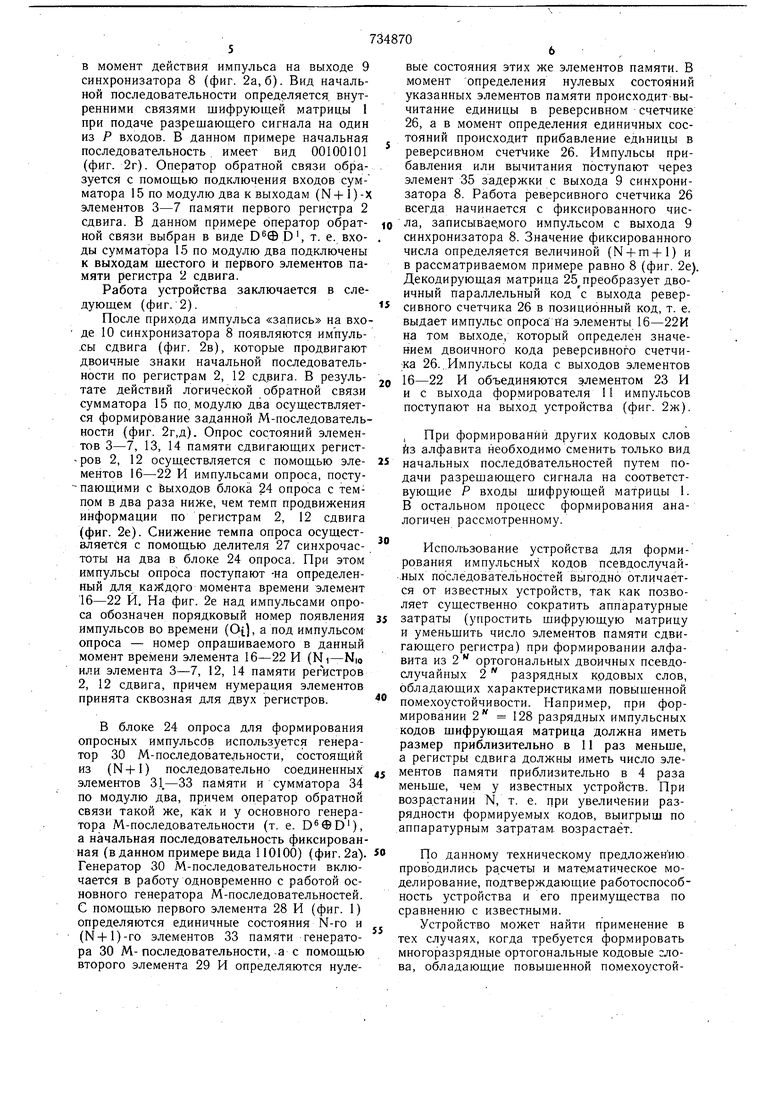

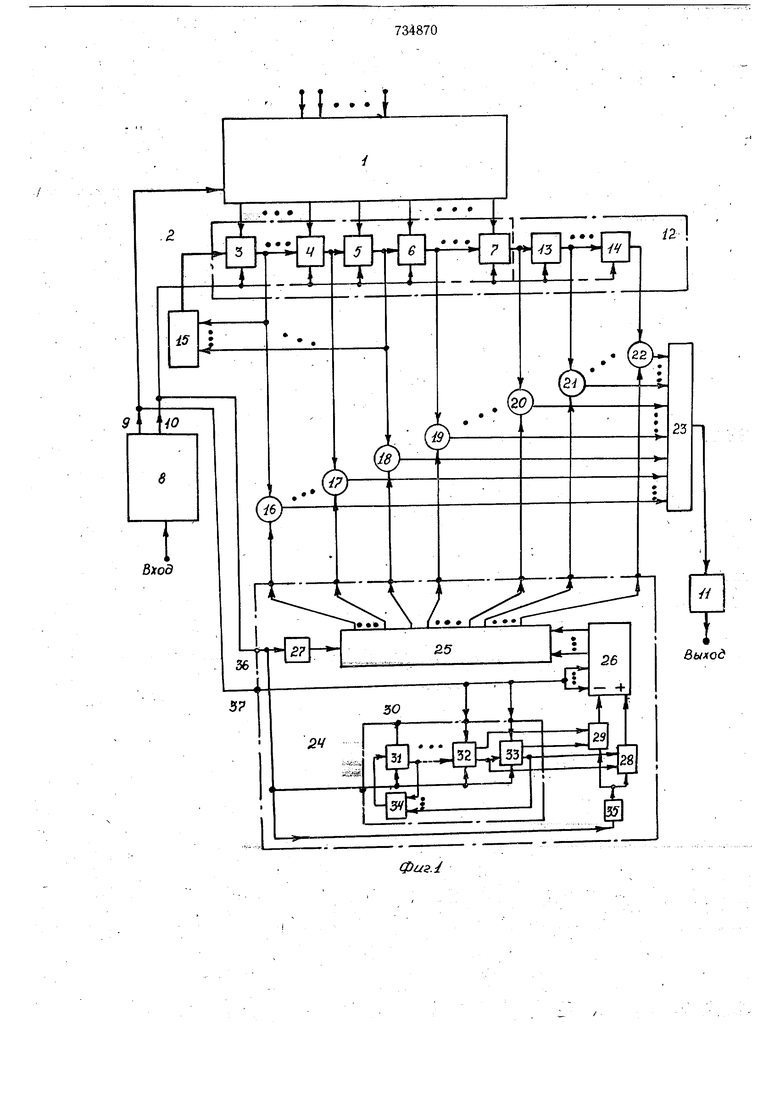

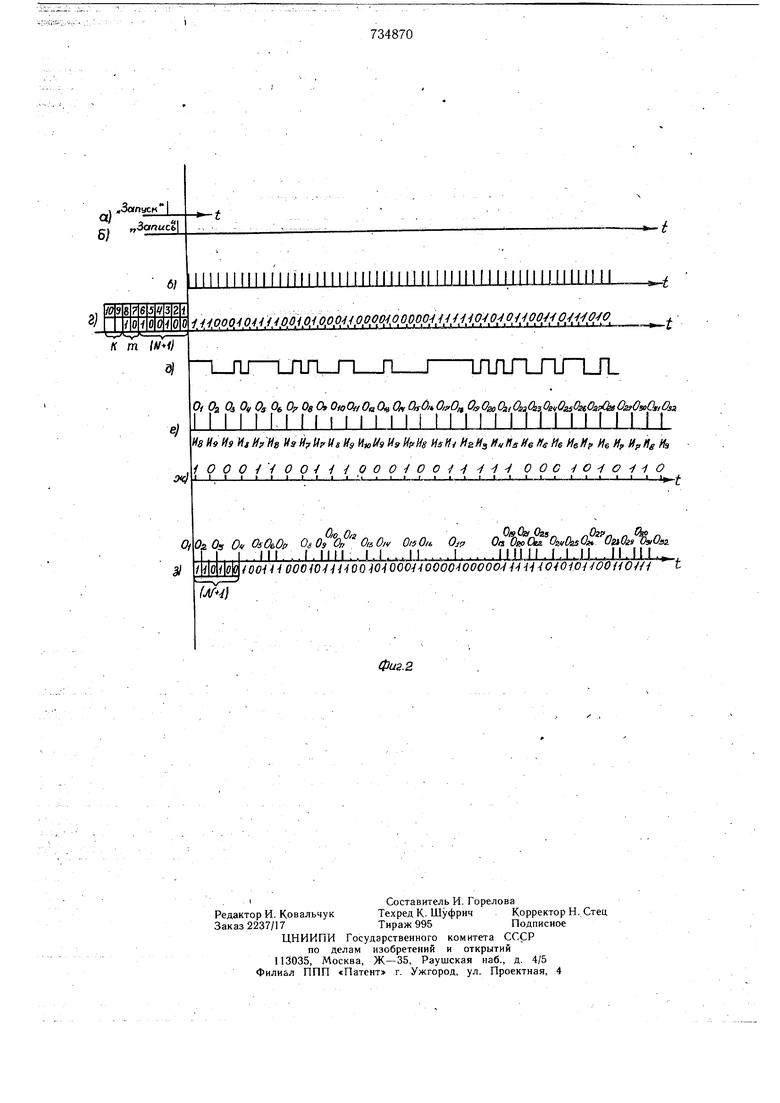

На фиг. 1 представлена функциональная блок-схема устройства для формирования импульсных кодов псевдослучайных последовательностей; на фиг. 2 - временные диаграммы, поясняющие работу устройства.

Устройство содержит шифрующую матрицу I с (Р -f 1) входами, регистр 2 сдвига, состоящий из последовательно соединенных элементов 3-7 памяти с раздельными входами «запись, соединенными с выходами шифрующей матрицы 1, синхронизатор 8, первый выход 9 которого соединен со входом щифрующей матрицы 1, а второй 10 - с управляющим входом регистра 2 сдвига, формирователь 11 импульсов, второй регистр 12 сдвига, состоящий из К последовательно соединенных элементов 13, 14 памяти, вход которого подключен к выходу первого регистра 2 сдвига, состоящего из (N + m + 1) элементов 3-7 памяти, сумматор .15 по модулю два, выход которого соединен со входом регистра 2 сдвига, а входы которого соединены с выходами (N + 1) элементовпамяти первого регистра 2 сдвига, (N+ m + k + 1) элементов 16-22 И на два входа, первые из которых соединены с вйходами элементов 3-7, 13, 14 памяти регистров 2, 12 сдвига, элемент 23 ИЛИ (N -f ш + k + I) входов которого соединены с выходами элементов 16-22 И, а выход соединен со входом формирователя 11 импульсов, и блок 24 опроса, выходы которого соединены со входами (N -f m + k + 1) элементов 16-22 И, а

входы блока опроса подключены к первому 9 и второму 10 выходам синхронизатора 8. Блок опроса 24 содержит декодирующую матрицу 25, двоичный реверсивный счетчик 26, делитель 27 синхрочастоты на два, два элемента 28, 29 И и генератор 30 М-последовательности, состоящий из (N + 1) последовательно соединенных элементов 31-33 памяти с раздельными входами «запись и сумматор 34 по модулю два, причем в блоке 24 опроса (N + ш + k -f 1) выходов декодирующей матрицы 25 соединены с выходами блока 24 опроса, выходы реверсивного счетчика 26 соединены со входами декодирующей матрицы 25, два входа первого элемента 28 И соединены с прямыми, а два входа

5 второго элемента 29 И соединены с инверсными выходами N-ro 32 и (N + 1)-го 33 элементов памяти генератора 30 М-последовательности, выход первого элемента 28 И соединен с суммирующим, а выход второго элемента 29 И соединен с вычитающим входами реверсивного счетчика 26, причем управляющий вход декодирующей матрицы 25 через делитель 27 синхрочастоты на два, третьи входы двух элементов 28, 29 И через элемент 35 задержки, а управляющий

J вход генератора 30 М-последовательности непосредственно соединен со второй входной шиной 36 блока опроса, управляющий вход реверсивного счетчика 28 и входы «запись генератора 30 М-последовательности соединены с первой входной шиной 37 блоO ка 24 опроса.

Работу устройства рассмотрим на конкретном примере формирования одного из 32-х разрядных кодовых слов (из алфавита ортогональных двоичных кодовых слов).

Принцип работы устройства основан на нелинейном преобразовании двоичных знаков М-последовательностей, формируемых генератором М-последовательностей, выполненным в виде сдвигающего регистра 2 из (N-f 1) элементов 3-6 памяти и сумматора

0. 15 по модулю два, которое реализуется опросом состояний элементов 3-7, 13, 14 памяти первого регистра 2 сдвига и второго регистра 12 сдвига с помощью блока 24 опроса.

В рассматриваемом примере для формирования 2 32-х разрядных кодов (т. е. при N 5) вида, изображенного на фиг. 2ж, применяется первый регистр 2 сдвига, состоящий из N + основных элементов

0 3-7 памяти, и второй регистр 12 сдвига, состоящий из (m + k) 2-f 2 4 дополнительных элементов 13, 14 памяти, причем величина (m + k) определяется, максимальным числом нулевых знаков в опорной (опросной) последовательности, т. е. (m + k)

. При этом, начальная последовательность записывается в (N + rn+l) 8 элементов памяти одновременно импульсом «запись с выходом щифрующей матрицы 1 в момент действия импульса на выходе 9 синхронизатора 8 (фиг. 2а, б). Вид начальной последовательности определяется внутренними связями шифрующей матрицы 1 при подаче разрешающего сигнала на один из Р входов. В данном примере начальная последовательность имеет вид 00100101 (фиг. 2г). Оператор обратной связи образуется с помощью подключения входов сумматора 15 по модулю два к выходам (N-bl)-X элементов 3-7 памяти первого регистра 2 сдвига. В данном примере оператор обратной связи выбран в виде , т. е. входы сумматора 15 по модулю два подключены к выходам шестого и первого элементов памяти регистра 2 сдвига. Работа устройства заключается в следующем (фиг. 2). После прихода импульса «запись на входе 10 синхронизатора 8 появляются импуль,сы сдвига (фиг. 2в), которые продвигают двоичные знаки начальной последовательности по регистрам 2, 12 сдвига. В результате действий логической обратной связи сумматора 15 по, модулю два осуществляется формирование заданной М-последовательности (фиг. 2г,д). Опрос состояний элементов 3-7, 13, 14 памяти сдвигающих регист-ров 2, 12 осуществляется с помощью элементов 16-22 И импульсами опроса, посту-пающими с Ьыходов блока 24 опроса с темпом в два раза ниже, чем темп продвижения информации по регистрам 2, 12 сдвига (фиг. 2е). Снижение темпа опроса осуществляется с помощью делителя 27 синхрочастоты на два в блоке 24 опроса. При этом импульсы опроса поступают -на определенный для каждого момента времени элемент 16-22 И. На фиг. 2е над импульсами опроса обозначен порядковый номер появления импульсов во времени (О{), а под импульсом опроса - номер опрашиваемого в данный момент времени элемента 16-22 И ( или элемента 3-7, 12, 14 памяти регистров 2, 12 сдвига, причем нумерация элементов принята сквозная для двух регистров. В блоке 24 опроса для формирования опросных импульсов используется генератор 30 М-последовате 1ьности, состоящий из (N-fl) последовательно соединенных элементов 31,-33 памяти и сумматора 34 по модулю два, причем оператор обратной связи такой же, как и у основного генератора М-последовательности (т. е. ), а начальная последовательность фиксированная (в данном примере вида 110100) (фиг. 2а). Генератор 30 М-последовательности включается в работу одновременно с работой основного генератора М-последовательностей. С помощью первого элемента 28 И (фиг. 1) определяются единичные состояния N-ro и (N+l)-ro элементов 33 памяти генератора 30 М-последовательности, а с помощью второго элемента 29 И определяются нулевые состояния этих же элементов памяти. В момент определения нулевых состояний указанных элементов памяти происходит-вычитание единицы в реверсивном счетчике 26, а в момент определения единичных состояний происходит прибавление единицы в реверсивном счетЧике 26. Импульсы прибавления или вычитания поступают через элемент 35 задержки с выхода 9 синхронизатора 8. Работа реверсивного счетчика 26 всегда начинается с фиксированного числа, записываемого импульсом с выхода 9 синхронизатора 8. Значение фиксированного числа определяется величиной (N-fm+1) и в рассматриваемом примере равно 8 (фиг. 2е). Декодирующая матрица 25 преобразует двоичный параллельный код с выхода реверсивного счетчика 26 в позиционный код, т. е. выдает импульс опроса На элементы 16-22И на том выходе, который определен значением двоичного кода реверсивного счетчика 26. ..Импульсы кода с выходов элементов 16-22 И объединяются элементом 23 И и с выхода формирователя II импульсов поступают на выход устройства (фиг. 2ж). , При формировании других кодовых слов из алфавита необходимо сменить только вид начальных последбвательностей путем подачи разрешающего сигнала на соответствующие Р входы шифрующей матрицы 1. В остальном процесс формирования аналогичен рассмотренному. Использование устройства для формирования импульсных кодов псевдослучай,ных последовательностей выгодно отличается от известных устройств, так как позволяет существенно сократить аппаратурные затраты (упростить шифрующую матрицу и уменьщить число элементов памяти сдвигающего регистра) при формировании алфавита из 2 ортогональных двоичных псевдослучайных 2 разрядных кодовых слов, обладающих характеристиками повышенной помехоустойчивости. Например, при формировании 2 128 разрядных импульсных кодов шифрующая матрица должна иметь размер приблизительно в 11 раз меньше, а регистры сдвига должны иметь число элементов памяти приблизительно в 4 раза меньше, чем у известных устройств. При возрастании N, т. е. при увеличении разрядности формируемых кодов, выигрыш по аппаратурным затратам, возрастает. По данному техническому предложению проводились расчеты и мате..матическое моделирование, подтверждающие работоспособность устройства и его преимущества по сравнению с известными. Устройство может найти применение в тех случаях, когда требуется формировать многоразрядные ортогональные кодовые глова, обладающие повышенной помехоустойчивостью, например, в дальней командной или телеметрической системе связи, гидролокации и т. д. Формула изобретения 1. Устройство для формирования импульс ных кодов псевдослучайных последователь; ностей, содержащее шифрующую матрицу с (Р+1) входами, регистр сдвига, состоящий из последовательно соединенных элементов памяти с раздельными входами «запись, соединенными с выходами шифрующей матрицы, синхронизатор, первый выход которого соединен со входом шифрующей матрицы, а второй - с управляющим входом регистра сдвига, и формирователь импульсов, обличающееся тем, что, с целью сбкращения аппаратурных затрат при увеличении числа 2 разрядов формируемых кодов; оно дополнительно содержит второй регистр сдвига, состоящий из К последовательно соединенных элементов памяти, вход которого подключен к выходу первого регистра сдвига, состоящего из (N + rn + l) aJieMeHTOB памяти, сумматор по модулю два, вь1ход которого, соединен со входом регистра сдвига, а входы которого соединены с выходами (N-f-1) элементов памяти первого регистра сдвига, (N + m + k+l) элементов И на два вхоДа, первые из которых соединены с выходами элементов памяти регистров сдвига, элемент ИЛИ, (N + m + k+1) входов которого соединены с выходами элементов И, а выход соединен со входом формирователя импульсов, и блок опроса, выходы которого соединены со входами (N -Ь m Ч- k + 1) элементов И, а входы блока опроса подключены к первому и второму выходам синхронизатора. 2. Устройстви по п. 1, отличающееся тем, что блок опроса содержит декодирующую матрицу, двоичный реверсивный счетчик, делитель синхрочастоты на два, два элемента И и генератор М-последовательности, состоящий из (N + 1) последовательно соединенных элементов памяти с раздельными входами «запись и сумматора по модулю два, причем в блоке опроса (N m -f k + 1) выходов декодирующей матрицы соединены с выходными шинами блока опроса, выходь реверсивного счетчика соединены со входами декодирующей матрицы, два входа первого элемента И соединены с прямыми, а два входа второго элемента И соединены с инверсными выходами N-ro и (N+ 1)-го элементов памяти генератора М-последовательности соответственно, выход первого элемента И соединен с суммирующим, а выход второго элемента И соединен с вычитающим выходами реверсивного счетчика, причем управляющий вход декодирующей матрицы через делитель синхрочастоты на два, третьи входы двух элементов И через элемент задержки, а управляющий вход генератора Мпоследовательности непосредственно соединены со второй входной шиной блока опроса, управляющий вход реверсивного счетчика и входы «запись генератора М-последовательности соединены с первой входной шиной блока опроса. Источники информации, принятые во внимание при экспертизе 1.Томэн Цифровая полевая система связи. «Зарубежная радиоэлектроника, 1964, № 4. 2.Новик А. А. Эффективное кодирование, Л., «Энергия, 1965, с. 113, 123./

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство формирования укороченного псевдослучайного @ -разрядного кода | 1982 |

|

SU1200424A1 |

| Цифровой фазометр | 1983 |

|

SU1188669A2 |

| Цифровой фазовый дискриминатор | 1986 |

|

SU1354387A1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ В АДАПТИВНЫХ ТЕЛЕМЕТРИЧЕСКИХ СИСТЕМАХ | 1995 |

|

RU2103745C1 |

| Измеритель сдвига фаз (его варианты) | 1982 |

|

SU1040432A1 |

| Устройство для формирования информации на телевизионном индикаторе | 1981 |

|

SU1075298A1 |

| Цифровой фазометр | 1983 |

|

SU1187100A2 |

| Кодек самоортогонального квазициклического кода | 1986 |

|

SU1376247A1 |

| Телевизионный координатор | 1983 |

|

SU1109956A1 |

Авторы

Даты

1980-05-15—Публикация

1973-06-11—Подача