1

Изобретение относится к вычислительной технике и может быть использовано для сопряжения электронной цифровой вычислительной машины (ЦВМ) и устройств ввода-вывода, имеющих различные интерфейсы.

Известно устройство для сопряжения вычислительных .машин с различными интерфейсами, содержащее блок динамической памяти, блок приема информации, буферный регистр, блоки приема и сравнения адреса, блок приема команд, блок передачи данных, регистры адреса и команд и дешифратор 1 .

Недостатками такого устройства являются ограниченные функциональные возможности, непозволяющие выполнять преобразование информации непосредственно в устройстве управления для сопряжения ЦВМ, что в конечном счете приводит к существенным затратам производительности ЦВМ на предварительную обработку информации.

Наиболее близким по технической сущности к предлагаемому является устройство для сопряжения цифровых вычислительных машин, содержащее буферный регистр, дешифратор управляющих сигналов, первый

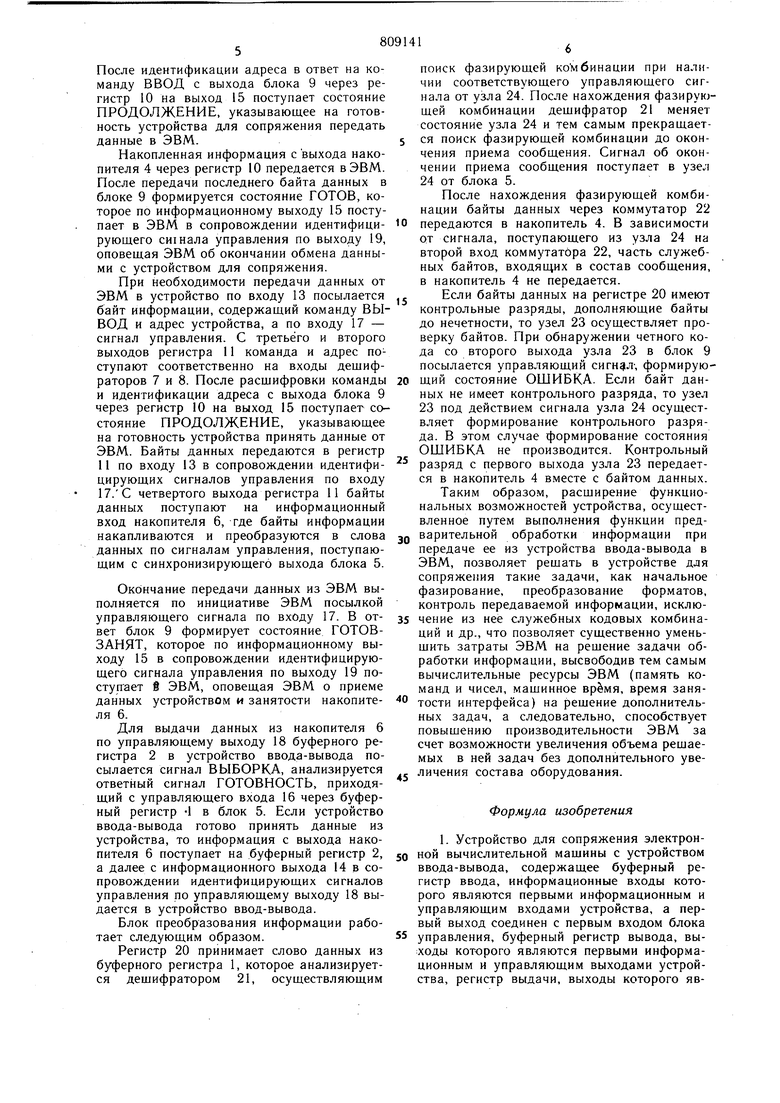

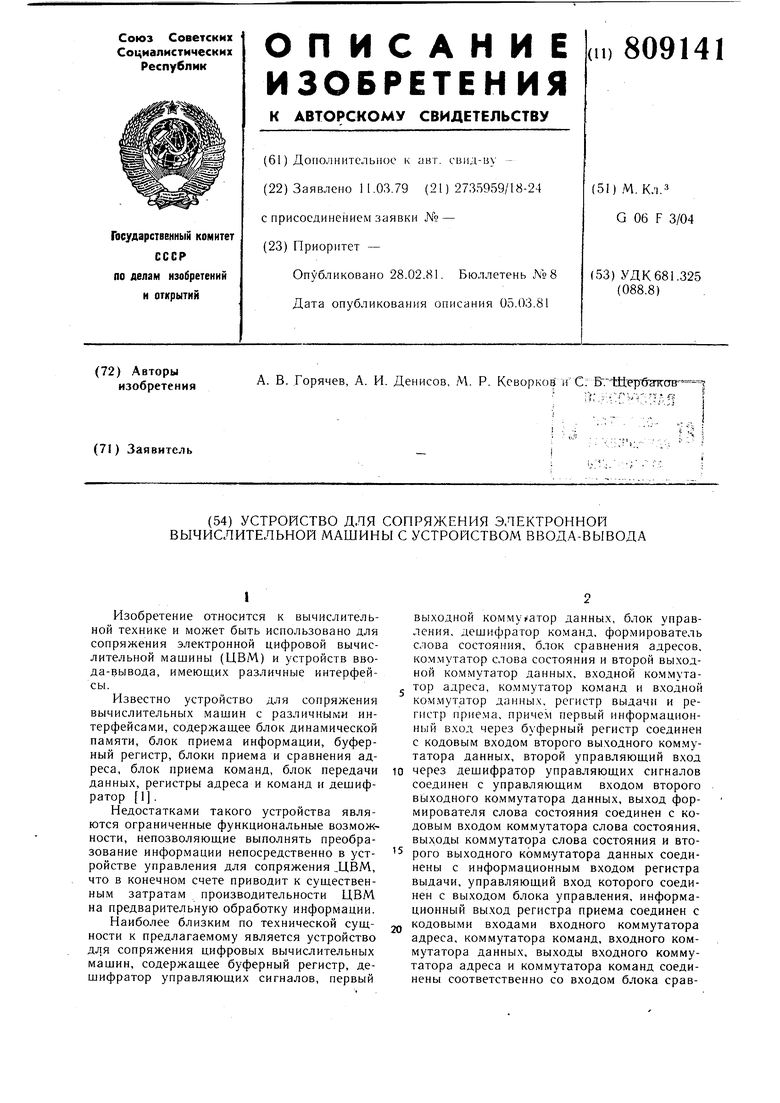

выходной коммуiiaTOp данных, блок управления, дешифратор команд, формирователь слова состояния, блок сравнения адресов, коммутатор слова состояния и второй выходной коммутатор данных, входной коммутатор адреса, коммутатор ко.манд и в.чодной ком.мутатор данных, регистр выдачи и регистр прие.ма, причем первый информационный вход через буферный регистр соединен с кодовым входом второго выходного коммутатора данных, второй управляющий вход через дешифратор управляющих сигналов соединен с управляющим входом второго выходного коммутатора данных, выход формирователя слова состояния соединен с кодовым входом коммутатора слова состояния, выходы коммутатора слова состояния и второго выходного коммутатора данных соединены с информационным входом регистра выдачи, управляющий вход которого соединен с выходом блока управления, информационный выход регистра приема соединен с кодовыми входами входного коммутатора адреса, коммутатора команд, входного коммутатора данных, вы.ходы входного коммутатора адреса и коммутатора команд соединены соответственно со входом блока сравнения адреса и входом дешифратора команд, выход которого соединен со входом блока управления, выход входного коммутатора данных через первый выходной коммутатор данных соединен с первым информационным выходом устройства 2. Недостатки известного устройства заключаются в ограниченных функциональных возможностях, поскольку в нем исключена возможность предварительной обработки данных (например, накопление байтов данных после обнаружения фазирующей комбинации в составе принимаемой информации, исключение в процессе накопления служебной информации, контроль байтов по четности и т.п.), потребность в которой возникает из-за различного представления данных в сопрягаемых вычислительных устройствах с разнотипными интерфейсами. Это приводит к существенным затратам производительности ЦВМ на предварительную обработку данных. Цель изобретения - расщирение функциональных возможностей устройства за счет транзитного преобразования данных. Поставленная цель достигается тем, что в устройство, содержащее буферный регистр ввода, информационные входы которого являются первыми информационном и управляющим входами устройства, а первый выход соединен с первым входом блока,.управления, буферный регистр вывода, выходы которого являются первыми информационным и управляющим выходами устройства, регистр выдачи, выходы которого являются вторыми информационным и управляющим выходами устройства, а первый вход подключен к выходу блока формирования слова состояния, первый вход которого соединен с первым выходом регистра приема, а второй - с первым выходом дешифратора команд, второй выход которого соединен со вторым входом блока управления, третьим входом соединенного через дешифратор адреса со вторым выходом регистра приема, третий выход которого подключен ко входу дешифратора команд, а входы являются вторыми информационным и управляющим входами устройства, введены наконитель приема, накопитель выдачи и блок формирования информации, причем информационный вход блока преобразования информации подключен к второму выходу буферного регистра ввода, управляющий выход - к третьему входу блока формирования слова состояния, информационный выход - к информационному входу накопителя приема, а управляющий вход - к управляющему входу накопителя приема, соединенного информационным выходом со вторым входом регистра выдачи, к синхронизирующему выходу блока управления и управляющему входу накопителя приема, информационные вход и выход которого подключены соответственно к четвертому выходу регистра приема и входу буферного регистра вывода, а также тем, что блок преобразования информации содержит регистр, дешифратор, узел синхронизации, первый вход которого является управляющим входом блока, узел свертки и коммутатор, причем выход коммутатора и первый выход узла свертки соединены с информационным выходом блока, их первые входы - соответственно с первым и втоpbiM выходами регистра, а вторые входы - соответственно с первым и вторым выходами узла синхронизации, второй в.ход и третий выход которого подключены соответственно к выходу и первому входу дешифратора, вторым входом соединенного с третьим выходом регистра, вход которого является информационным входом блока, второй выход узла свертки является управляющим выходом блока. На фиг. 1 представлена блок-схема устройства; на фиг. 2 - блок-схе.ма блока преобразования информации. Устройство содержит {фиг. 1) буферный регистр 1 ввода, буферный регистр 2 вывода, блок 3 преобразования информации, накопитель 4 приема, блок 5 управления, накопитель 6 выдачи, дещифратор 7 команд, дешифратор 8 адреса, блок 9 формирования слова состояния, регистр 10 выдачи, регистр И приема, информационные входы 12 и 13 и выходы 14 и 15 устройства, управляющие входы 16 и 17 и выходы 18 и 19 устройства. Блок 3 преобразования информации содержит (фиг. 2) регистр 20, дешифратор 21, коммутатор 22, узел 23 свертки и узел 24 синхронизации. Уctpoйcтвo работает следующим образом. Нри необходимости передать очередное слово данных от устройства ввода-вывода по входу 16 поступает сигнал ГОТОВНОСТЬ на буферный регистр 1, в ответ устройство для сопряжения по выходу 14 сигналом ПРИЕМ разрешает выставить информацию на вход 12. Каждое очередное слово данных через буферный регистр 1 поступает на вход блока 3, с помощью которого производится преобразование форматов поступающей информации, начальное фазирование, контроль и исключение служебной информации. Из блока 3 данные побайтно поступают в накопитель 4, где происходит формирование сообщения. После заполнения накопителя 4 сообщением блок 9 формирует состояние ЗАПРОС, которое поступает на регистр 1.0 и передается с выхода 15 в сопровождении идентифицирующего сигнала управления по выходу 19 и ЭВМ. В ответ на состояние ЗАПРОС ЭВМ по входу 13 посылает байт информации, содержащий команду ВВОД и адрес устройства для сопряжения, а по входу 17 - сигнал управления. С третьего и второго выходов регистра 11 команда и адрес поступают соответственно на входы дешифраторов 7 и 8.

После идентификации адреса в ответ на команду ВВОД с выхода блока 9 через регистр 10 на выход 15 поступает состояние ПРОДОЛЖЕНИЕ, указывающее на готовность устройства для сопряжения передать данные в ЭВМ.

Накопленная информация с выхода накопителя 4 через регистр 10 передается в ЭВМ. После передачи последнего байта данных в блоке 9 формируется состояние ГОТОВ, которое по информационному выходу 15 поступает в ЭВМ в сопровождении идентифицирующего си1нала управления по выходу 19, оповещая ЭВМ об окончании обмена данными с устройством для сопряжения.

При необходимости передачи данных от ЭВМ в устройство по входу 13 посылается байт информации, содержащий команду ВЫВОД и адрес устройства, а по входу 17 - сигнал управления. С третьего и второго выходов регистра 11 команда и адрес поступают соответственно на входы дешифраторов 7 и 8. После расщифровки команды и идентификации адреса с выхода блока 9 через регистр 10 на выход 15 поступает состояние ПРОДОЛЖЕНИЕ, указывающее на готовность устройства принять данные от ЭВМ. Байты данных передаются в регистр 11 по входу 13 в сопровождении идентифицирующих сигналов управления по входу 17.С четвертого выхода регистра 11 байты данных поступают на информационный вход накопителя 6, где байты информации накапливаются и преобразуются в слова данных по сигналам управления, поступающим с синхронизирующего выхода блока 5.

Окончание передачи данных из ЭВМ выполняется по инициативе ЭВМ посылкой управляющего сигнала по входу 17. В ответ блок 9 формирует состояние ГОТОВЗАНЯТ, которое по информационному выходу 15 в сопровождении идентифицирующего сигнала управления по выходу 19 поступает 8 ЭВМ, оповещая ЭВМ о приеме данных устройством и занятости накопителя 6.

Для выдачи данных из накопителя 6 по управляющему выходу 18 буферного регистра 2 в устройство ввода-вывода посылается сигнал ВЫБОРКА, анализируется ответный сигнал ГОТОВНОСТЬ, приходящий с управляющего входа 16 через буферный регистр -1 в блок 5. Если устройство ввода-вывода готово принять данные из устройства, то информация с выхода накопителя б поступает на буферный регистр 2, а далее с информационного выхода 14 в сопровождении идентифицирующих сигналов управления по управляющему выходу 18 выдается в устройство ввод-вывода.

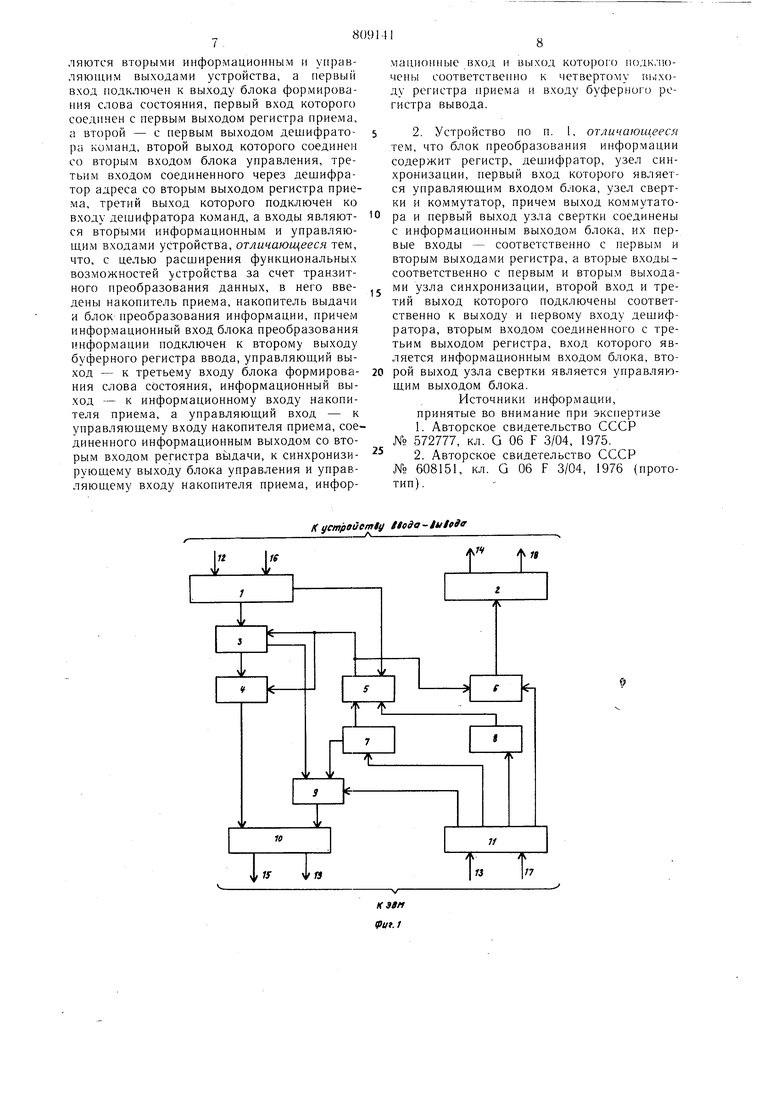

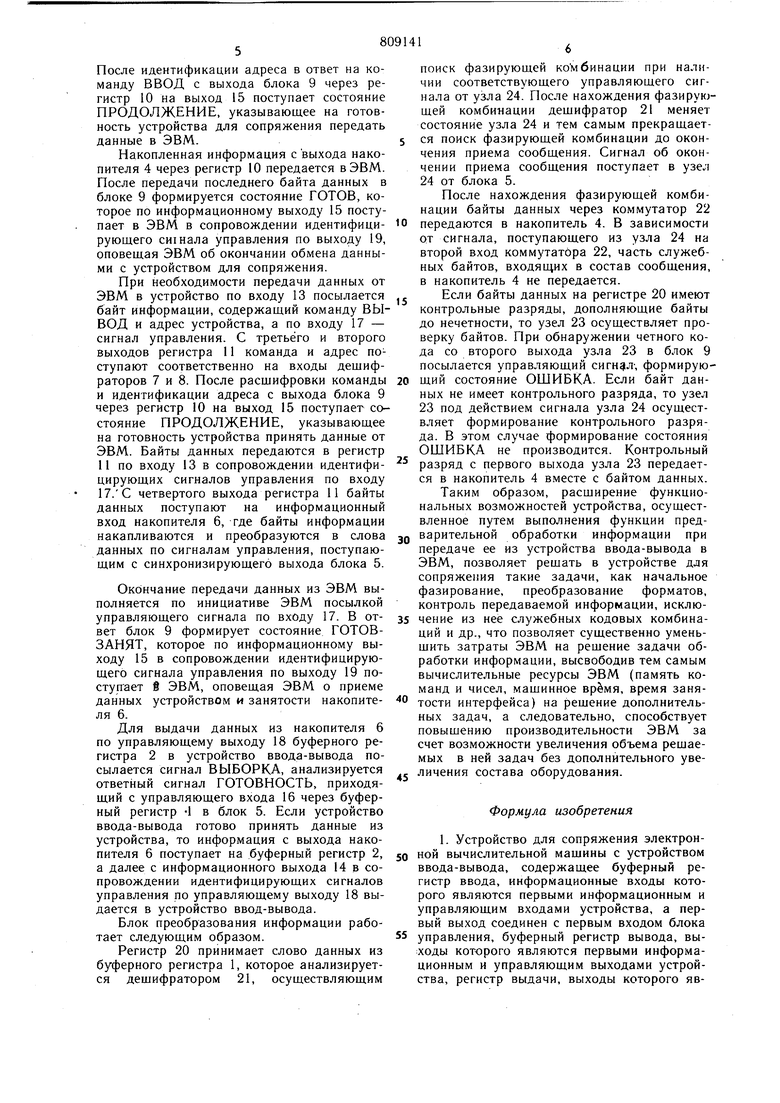

Блок преобразования информации работает следующим образом.

Регистр 20 принимает слово данных из буферного регистра 1, которое анализируется дещифратором 21, осуществляющим

поиск фазирующей комбинации при наличии соответствующего управляющего сигнала от узла 24. После нахождения фазирующей комбинации дешифратор 21 меняет состояние узла 24 и тем самым прекращается поиск фазирующей комбинации до окончения приема сообщения. Сигнал об окончении приема сообщения поступает в узел 24 от блока 5.

После нахождения фазирующей комбинации байты данных через коммутатор 22 передаются в накопитель 4. В зависимости от сигнала, поступающего из узла 24 на второй вход коммутатора 22, часть служебных байтов, входящих в состав сообщения, в накопитель 4 не передается.

Если байты данных на регистре 20 имеют контрольные разряды, дополняющие байты до нечетности, то узел 23 осуществляет проверку байтов. При обнаружении четного кода со второго выхода узла 23 в блок 9 посылается управляющий сигнал-, формирующий состояние ОШИБКА. Если байт данных не имеет контрольного разряда, то узел 23 под действием сигнала узла 24 осуществляет формирование контрольного разряда. В этом случае формирование состояния ОШИБКА не производится. Контрольный разряд с первого выхода узла 23 передается в накопитель 4 вместе с байтом данных.

Таким образом, расширение функциональных возможностей устройства, осуществленное путем выполнения функции предварительной обработки информации при передаче ее из устройства ввода-вывода в ЭВМ, позволяет решать в устройстве для сопряжения такие задачи, как начальное фазирование, преобразование форматов, контроль передаваемой информации, исключение из нее служебных кодовых комбинаций и др., что позволяет существенно уменьшить затраты ЭВМ на решение задачи обработки информации, высвободив тем самым вычислительные ресурсы ЭВМ (память команд и чисел, машинное время, время занятости интерфейса) на решение дополнительных задач, а следовательно, способствует повышению производительности ЭВМ за счет возможности увеличения объема решаемых в ней задач без дополнительного увеличения состава оборудования.

Формула изобретения

1. Устройство для сопряжения электронной вычислительной машины с устройством ввода-вывода, содержащее буферный регистр ввода, информационные входы которого являются первыми информационным и управляющим входами устройства, а первый выход соединен с первым входом блока управления, буферный регистр вывода, выходы которого являются первыми информационным и управляющим выходами устройства, регистр выдачи, выходы которого являются вторыми информационным и унравЛЯЮ1ЦИМ выходами устройства, а первый вход подключен к выходу блока формирования слова состояния, первый вход которого соединен с первым выходом регистра приема, а второй - с первым выходом дешифратора команд, второй выход которого соединен со вторым входом блока управления, третьим Е5ХОДОМ соединенного через дешифратор адреса со вторым выходом регистра приема, третий выход которого подключен ко входу дешифратора команд, а входы являются вторыми информационным и управляющим входами устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет транзитного преобразования данных, в него введены накопитель приема, накопитель выдачи и блок преобразования информации, причем информационный вход блока преобразования информации подключен к второму выходу буферного регистра ввода, управляющий выход - к третьему входу блока формирования слова состояния, информационный выход - к информационному входу накопителя приема, а управляющий вход - к управляющему входу накопителя приема, соединенного информационным выходом со вторым входом регистра вьщачи, к синхронизирующему выходу блока управления и управляющему входу накопителя приема, инфор/( устройemiy Иода - tulfiff

15Ф

1 /|v п

«I мационные вход и выход KOTOpoio подключены соответственно к четвертому BI.IXOду регистра приема и входу буферного регистра вывода. 2. Устройство по п. I, отличающееся тем, что блок преобразования информации содержит регистр, дешифратор, узел синхронизации, первый вход которого является управляюшим входом блока, узел свертки и коммутатор, причем выход коммутатора и первый выход узла свертки соединены с информационным выходом блока, их первые входы - соответственно с первым и вторым выходами регистра, а вторые входысоответственно с первым и вторым выходами узла синхронизации, второй вход и третий выход которого подключены соответственно к выходу и первому входу дешифратора, вторым входом соединенного с третьим выходом регистра, вход которого является информационным входом блока, второй выход узла свертки является управляющим выходом блока. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 572777, кл. G 06 F 3/04, 1975. 2.Авторское свидетельство СССР № 608151, кл. G 06 F 3/04, 1976 (прототип).

Г

го

f

22

У Ф

В накопитель

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для обмена информацией | 1986 |

|

SU1336017A1 |

| Устройство для сопряжения | 1978 |

|

SU712821A1 |

| УСТРОЙСТВО ЗАЩИТЫ ИНФОРМАЦИИ | 1990 |

|

RU2022346C1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Устройство для сопряжения двух цифровых вычислительных машин | 1979 |

|

SU868741A1 |

| Устройство для сопряжения электрон-НыХ ВычиСлиТЕльНыХ МАшиН | 1979 |

|

SU809145A1 |

| Устройство для отображения информации | 1986 |

|

SU1506478A1 |

Авторы

Даты

1981-02-28—Публикация

1979-03-11—Подача